Содержание

Введение................................................................................................................................. 3

1. Разработка структурной схемы......................................................................................... 4

2. Разработка принципиальной

схемы................................................................................. 5

2.1. Математические сопроцессор................................................................................... 5

2.2. Система прерываний................................................................................................. 6

2.2.1. Формирование прерываний

и передача в ЦПУ вектора прерываний......... 6

2.2.2. Возврат из

прерываний и его реализация...................................................... 10

2.2.3. Запоминание и

восстановление состояния прерываемой программы....... 10

2.2.4. Управление приоритетами.............................................................................. 12

2.3. КЭШ........................................................................................................................... 14

2.3.1. Работа ЦПУ при удачном и

неудачном обращении к КЭШу...................... 14

2.3.2. Структурная организация

КЭШа, размер блока........................................... 16

2.3.3. Используемый алгоритм

свопинга................................................................. 16

2.3.4. Механизм отмены

содержимого КЭШа и замещения информации в КЭШе 18

2.4. Оперативная память................................................................................................. 19

2.4.1. Используемый способ

расширения емкости оперативной памяти............. 19

2.4.2. Максимальный объем

расширенной памяти................................................. 20

2.4.3. Используемые типы

адресов........................................................................... 20

2.5. Система контроля..................................................................................................... 21

2.5.1. Система контроля памяти

по Хэммингу........................................................ 21

2.5.2. Система контроля ввода –

вывода по паритету............................................ 28

2.5.3.

Асинхронная связь........................................................................................... 31

2.5.4.

Синхронная связь............................................................................................. 34

3. Заключение....................................................................................................................... 36

4. Используемая литература................................................................................................ 37

Введение

Целью данной курсовой работы является разработка основных

компонентов электронно-вычислительной машины (ЭВМ).

Основное внимание в работе будет уделено блоку системы

прерывания:

·

формирование прерываний и передача в ЦПУ вектора

прерываний;

·

возврат из прерываний и его реализация;

·

запоминание и восстановление состояния прерываний;

·

управление приоритетами.

Помимо этого будут рассмотрены такие вопросы, как:

·

использование КЭШ;

·

структура и принципы функционирования

оперативной памяти;

·

физическая и программная реализация управления

вводом - выводом;

1. Разработка структурной схемы

ЭВМ предназначены для обработки информации и отображения

результатов обработки. Для решения задачи должна быть написана программа.

Во время решения задачи программа и операнды (числа, над

которыми производится операции) находятся в оперативной памяти (ОЗУ).

Быстродействие ОЗУ соизмеримо с быстродействием АЛУ. В процессе решения задачи

АЛУ постоянно взаимодействует с ОЗУ, передавая в ОЗУ промежуточные и конечные результаты

и получая из ОЗУ операнды действия всех частей ЭВМ при решении задачи

осуществляется под воздействием управляющих сигналов, вырабатываемых

устройством управления в соответствии с программой, записанной в ОЗУ.

ПЗУ предназначено для хранения стандартных программ, таких

как sin и cos, констант , е.

Существует еще сверх ОЗУ (СОЗУ), которое обладает малым

объемом и высоким быстродействием. СОЗУ применяется для кратковременного

хранения операндов и промежуточных результатов.

Качество ЭВМ определяется: объемом ОЗУ (т.е. количеством

одновременно хранимых в ОЗУ двоичных

слов); быстродействием, определяемым количеством операций в сек. После

выполнения задачи, программа и результаты через устройство вывода записываются

во внешнее ЗУ. В качестве внешних ЗУ используются магнитная лента, гибкий

магнитный диск, магнитный барабан, перфолента, перфокарты. Программа вводится в

ОЗУ с внешних ЗУ или с клавиатуры через устройство ввода.

2. Разработка принципиальной схемы

2.1. Математические сопроцессор

Математический сопроцессор - это специальный модуль для

выполнения операций с плавающей запятой, который работает в содружестве с

центральным процессором.

Математический сопроцессор не является обязательным

элементом персонального компьютера. От него, в принципе, можно отказаться. Так

раньше и поступали из соображений экономии.

Однако, при решении задач, которые требовали выполнения большого количества

математических вычислений, например, при научных или инженерных расчетах, остро

встал вопрос о повышении производительности компьютера.

Для этого решили использовать дополнительный специальный

процессор, который "настроен" на выполнение математических операций и

реализует их во много раз быстрее, чем центральный процессор. Таким образом,

была получена возможность наращивать производительность центрального процессора

за счет специального модуля - математического сопроцессора.

Не в пример центральному процессору, математический

сопроцессор не держит под управлением основную массу цепей компьютера. Наоборот,

вся деятельность математического сопроцессора определяется центральным

процессором, который может посылать математическому сопроцессору команды на

выполнение программ и формирование результатов.

В обычном режиме центральный процессор выполняет все функции

компьютера. И лишь, когда встречается задача, с которой лучше справится

математический сопроцессор, ему выдаются данные и команды, а центральный

процессор ожидает результаты. К таким задачам относятся, например,

математические операции между вещественными числами (операции между числами с

плавающей запятой), где числа представлены мантиссой и ординатой (десятичная

степень числа, определяющая положение десятичной запятой).

Если раньше, в компьютерах первых поколений (i80386, i80486)

модуль математического сопроцессора устанавливался на материнскую плату в виде

отдельного чипа, то в современных компьютерах использование математического

сопроцессора, как отдельного чипа, не требуется, поскольку он уже встроен в

центральный процессор.

Преимущества, получаемые от использования математического

сопроцессора, зависят от того, какие задачи решаются на ЭВМ.

Согласно данным компании INTEL, математический сопроцессор может уменьшить

время выполнения математических операций, таких, как умножение, деление и возведение

в степень, на 80 процентов и более. Скорость выполнения простых математических

операций, таких, как сложение и вычитание, не изменяется.

С практической точки зрения, производительность

персонального компьютера, касающаяся подготовки текстов и ведения базы данных

(функций, не требующих сложных математических расчетов), не может быть улучшена

математическим сопроцессором. Однако, можно получить ощутимый прирост

производительности при проведении научных и инженерных расчетов, обработке

статистических данных, а также при работе с графикой, так как последняя требует

интенсивных математических расчетов.

2.2. Система прерываний

2.2.1. Формирование прерываний и передача в ЦПУ

вектора прерываний

Прерывание принудительная передача управления

от выполняемой программы к системе, происходящая при возникновении

определенного события.

Механизм прерываний позволяет координировать параллельное

функционирование отдельных устройств вычислительной системы и реагировать на

особые состояния, возникающие при работе процессора. Идея прерывания была

предложена в середине 50-х годов, основная цель введения механизма прерываний –

реализация асинхронного (независимого для разных компонентов) режима работы и

распараллеливание работы отдельных устройств.

Суть механизма прерываний заключается в следующем.

Во время выполнения ЭВМ текущей программы внутри машины и в

связанной с ней внешней среде (например, в технологическом процессе,

управляемом ЭВМ) могут возникать события, требующие немедленной реакции на них

со стороны машины. Реакция состоит в том, что машина прерывает обработку

текущей программы и переходит к выполнению некоторой другой программы,

специально предназначенной для данного события. По завершении этой программы

ЭВМ возвращается к выполнению прерванной программы.

Принципиально важным является то, что моменты возникновения

событий, требующих прерывания программ, заранее неизвестны и поэтому не могут

быть учтены при программировании.

Каждое событие, требующее прерывания, сопровождается

сигналом, оповещающим ЭВМ. Эти сигналы называются запросами прерывания.

Запросы на прерывания могут возникать внутри самой ЭВМ и в ее внешней среде. К

первым относятся, например, запросы при возникновении в ЭВМ таких событий, как

появление ошибки в работе ее аппаратуры, переполнение разрядной сетки, попытка

деления на 0, выход из установленной для данной программы области памяти,

затребование периферийным устройством операции ввода-вывода, завершение

операции ввода-вывода периферийным устройством или возникновение при этой

операции особой ситуации и др. Хотя. некоторые из указанных событий порождаются

самой программой, моменты их появления, как правило, невозможно предусмотреть.

Запросы во внешней среде могут возникать от других ЭВМ, от аварийных и

некоторых других датчиков технологического процесса и т.п.

Механизм прерываний организуется аппаратными и программными

средствами. Схема прерывания в зависимости от его типа и аппаратной архитектуры

может быть организована различными способами, но в любом случае прерывание

характеризуется одной важной особенностью – прерывание непременно влечет за

собой изменение порядка выполнения команд процессором.

Возможность прерывания программ — важное архитектурное

свойство ЭВМ, позволяющее эффективно использовать производительность процессора

при наличии нескольких протекающих параллельно во времени процессов, требующих

в произвольные моменты времени управления и обслуживания со стороны процессора.

В первую очередь это относится к организации параллельной во времени работы

процессора и периферийных устройств машины, а также к использованию ЭВМ для

управления в реальном времени технологическими процессами.

Чтобы ЭВМ могла, не требуя больших усилий от программиста,

реализовывать с высоким быстродействием прерывания программ, машине необходимо

придать соответствующие аппаратные и программные средства, совокупность которых

получила название системы прерывания программ или контроллера

прерывания.

Главные функции механизма прерываний:

·

распознавание и классификация прерываний

·

передача управления обработчику прерываний

·

корректное возвращение к прерванной программе.

При этом переход от прерванной программы к обработчику

прерываний и обратно должен выполняться как можно быстрее. Соответствующий

промежуток времени называется латентной

задержкой и является важной характеристикой вычислительной системы.

Схема обработки прерывания представлена на рисунке.

Замечания:

1.

Передача управления осуществляется аппаратно.

2.

Программой Q может быть и прерванная программа Р.

3.

Для корректной обработки прерывания очень важно

запретить любые прерывания до окончания начатой обработки, поскольку иначе

может возникать бесконечная последовательность вложенных прерываний. По

окончанию обработки прерывания необходимо восстановить прежний режим системы

прерываний, т.е. разрешить их.

Схема обработки прерываний:

Обозначения:

! Прерывание (сигнал – установление

факта прерывания)

1 Идентификация прерывания

2 Отключение всех других прерываний

3 Смена контекста_1 (сохранение

состояния прерванного процесса из системных регистров, загрузка в системные

регистры контекста соответствующего обработчика прерываний)

4 Обработка прерывания, включающая

определение программы Q, которую следует запустить;

5 Смена контекста_2 (загрузка в

системные регистры контекста определенной на предыдущем шаге программы Q)

6 Установка прежнего режима системы

прерываний.

2.2.2. Возврат из прерываний и его

реализация

При наличии нескольких источников запросов прерывания должен

быть установлен определенный порядок (дисциплина) в обслуживании поступающих

запросов. Другими словами, между запросами (и соответствующими прерывающими

программами) должны быть установлены приоритетные соотношения,

определяющие, какой из нескольких поступивших запросов подлежит обработке в

первую очередь, и устанавливающие, имеет право или не имеет данный запрос

(прерывающая программа) прерывать ту или иную программу. Приоритетный выбор

запроса для исполнения входит в процедуру перехода к прерывающей программе.

Назовем вектором прерывания вектор "начального

состояния прерывающей программы. Вектор прерывания содержит всю необходимую

информацию для перехода к прерывающей программе, в том числе ее начальный

адрес. Каждому запросу (уровню) прерывания, а в ряде случаев, например в малых

и микроЭВМ и микропроцессорах, каждому периферийному устройству соответствует

свой вектор прерывания, способный инициировать выполнение соответствующей

прерывающей программы. Векторы прерывания обычно находятся в специально

выделенных фиксированных ячейках памяти.

2.2.3. Запоминание и восстановление состояния

прерываемой программы

Главное место в процедуре перехода к прерывающей программе

занимают передача из соответствующего регистра (регистров) процессора в память

(в частности, в стек) на сохранение текущего вектора состояния прерываемой

программы (чтобы можно было вернуться к ее исполнению) и загрузка в регистр

(регистры) процессора вектора прерывания прерывающей программы, к которой при

этом переходит управление процессором.

Прерывания, возникающие при работе вычислительной системы,

можно разделить на три класса:

·

внутренние

аппаратные (синхронные);

·

внешние аппаратные (асинхронные);

·

программные.

Внешние аппаратные

прерывания асинхронные

события, которые происходят вне процесса (сигнал прерывания формируется вне

процессора, инициируется контроллером периферийного устройства или

сопроцессором):

·

прерывания от таймера,

·

от внешних устройств,

·

прерывание по нарушению питания,

·

прерывание с пульта вычисления системы,

·

прерывание от другого процессора в

вычислительной сети.

Внутренние аппаратные прерывания синхронные события, которые связаны

с работой процессора и являются его синхронными операциями (сигнал прерывания

формируется внутри процессора при выполнении программы, закрепленные за

событиями номера прерываний зашиты внутри процессора и не могут быть изменены):

·

нарушение адресации,

·

наличие в поле кода операции незадействованной

двоичной операции,

·

переполнение и исчезновение порядка,

·

ошибки четности.

Программные прерывания

(по внутрипрограммной команде) также являются синхронными операциями. Любая

программа может инициировать синхронное программное прерывание путем выполнения

программы INT. MS-DOS использует для

взаимодействия с программами прерывания с номерами 20Н – 1FH, программы BIOS и

прикладные программы использует другие номера. При этом распределение номеров

условно и аппаратно не закреплено.

2.2.4. Управление приоритетами

Сигналы могут возникать одновременно, тогда выбор одного из

них для обработки осуществляется на основе приоритетов, приписанных каждому

типу прерывания, т.е. процедура организации перехода к прерывающей программе

включает в себя выделение из выставленных запросов такого, который имеет

наибольший приоритет.

Различают абсолютный и относительный приоритеты.

Запрос, имеющий абсолютный приоритет, прерывает выполняемую программу и

инициирует выполнение соответствующей прерывающей, программы. Запрос с

относительным приоритетом является первым кандидатом на обслуживание после

завершения выполнения текущей программы.

Если наиболее приоритетный из выставленных запросов прерывания

не превосходит по уровню приоритета выполняемую процессором программу, то

запрос прерывания игнорируется или его обслуживание откладывается до завершения

выполнения текущей программы.

Простейший способ установления приоритетных соотношений

между запросами (уровнями) прерывания состоит в том, что приоритет определяется

порядком присоединения линий сигналов запросов к входам системы прерывания. При

появлении нескольких запросов прерывания первым воспринимается запрос,

поступивший на вход с меньшим номером. В этом случае приоритет является жестко

фиксированным. Изменить приоритетные соотношения можно лишь пересоединением

линий сигналов запросов на входах системы прерывания.

Стандартное распределение приоритетов внутри вычислительной

системы:

|

-

Средства контроля

процессора

-

Системный

таймер

-

Внешние

устройства

§

Магнитные диски

§

Сетевое

оборудование

§

Терминалы и

мониторы

§

Прочие

периферийные устройства

-

Программные

прерывания

|

Высокий приоритет

Низкий приоритет

|

Не всегда сигнал прерывания вызывает прерывание

исполняющейся программы. Прерывание можно запрещать посредством отключения

системы прерываний или операций маскирования отдельных прерываний.

Кроме того, может быть организовано программное управление

обслуживанием прерываний в соответствии с дисциплиной обслуживания:

·

с относительными приоритетами обслуживание не прерывается при появлении сигнала прерывания с более

высоким приоритетом;

·

с абсолютными приоритетами многоуровневое обслуживание, всегда

обслуживается прерывание с наивысшим приоритетом;

·

по принципу стека, очереди и пр.

На рисунке 1 показан фрагмент временной диаграммы работы

планировщика в системе, где одновременно выполняются четыре процесса. В данном

случае неважно, по какому правилу выбираются процессы на выполнение и каким

образом изменяются их приоритеты. Существенное значение имеют лишь события,

вызывающие активизацию планировщика.

Рис.1. Моменты перепланирования

Первые четыре цикла работы планировщика, приведенные на

рисунке, были инициированы прерываниями от

таймера по истечении

квантов времени (эти события обозначены на рисунке как Т).

Следующая передача управления планировщику была осуществлена

в результате выполнения процессом системного запроса на ввод-вывод (событие

I/O). Планировщик перевел этот процесс в состояние ожидания, а затем переключил

процессор на процесс 2. Процесс 2 полностью использовал свой квант, произошло

прерывание от таймера, и планировщик активизировал процесс 1.

При выполнении процесса 1 произошло событие R – системный

вызов, в результате которого освободился некоторый ресурс (например, был закрыт

файл). Это событие вызвало перепланировку процессов. Планировщик просмотрел

очередь ожидающих процессов и обнаружил, что процесс 4 ждет освобождения

данного ресурса. Этот процесс был переведен в состояние готовности, но

поскольку приоритет выполняющегося в данный момент процесса 1 выше приоритета

процесса 4, планировщик вернул процессор процессу 1.

2.3. КЭШ

2.3.1. Работа ЦПУ при удачном и неудачном обращении

к КЭШу

Кэш-память - это способ организации совместного

функционирования двух типов запоминающих устройств, отличающихся временем

доступа и стоимостью хранения данных, который позволяет уменьшить среднее время

доступа к данным за счет динамического копирования в "быстрое" ЗУ

наиболее часто используемой информации из "медленного" ЗУ.

Кэш-памятью часто называют не только способ организации

работы двух типов запоминающих устройств, но и одно из устройств -

"быстрое" ЗУ. Оно стоит дороже и, как правило, имеет сравнительно

небольшой объем. Важно, что механизм кэш-памяти является прозрачным для

пользователя, который не должен сообщать никакой информации об интенсивности

использования данных и не должен никак участвовать в перемещении данных из ЗУ

одного типа в ЗУ другого типа, все это делается автоматически системными

средствами.

При использовании

кэш-памяти, каждый запрос к оперативной памяти выполняется в соответствии со

следующим алгоритмом:

1. Просматривается содержимое

кэш-памяти с целью определения, не находятся ли нужные данные в кэш-памяти;

кэш-память не является адресуемой, поэтому поиск нужных данных осуществляется

по содержимому - значению поля "адрес в оперативной памяти", взятому

из запроса.

2. Если данные обнаруживаются в

кэш-памяти, то они считываются из нее, и результат передается в процессор.

3. Если нужных данных нет, то

они вместе со своим адресом копируются из оперативной памяти в кэш-память, и

результат выполнения запроса передается в процессор. При копировании данных

может оказаться, что в кэш-памяти нет свободного места, тогда выбираются

данные, к которым в последний период было меньше всего обращений, для

вытеснения из кэш-памяти. Если вытесняемые данные были модифицированы за время

нахождения в кэш-памяти, то они переписываются в оперативную память. Если же

эти данные не были модифицированы, то их место в кэш-памяти объявляется

свободным.

2.3.2. Структурная организация КЭШа, размер блока.

Рассмотрим частный случай использования кэш-памяти для

уменьшения среднего времени доступа к данным, хранящимся в оперативной памяти.

Для этого между процессором и оперативной памятью помещается быстрое ЗУ,

называемое просто кэш-памятью (рисунок 2.1). В качестве такового может быть

использована, например, ассоциативная память. Содержимое кэш-памяти

представляет собой совокупность записей обо всех загруженных в нее элементах

данных. Каждая запись об элементе данных включает в себя адрес, который этот

элемент данных имеет в оперативной памяти, и управляющую информацию: признак

модификации и признак обращения к данным за некоторый последний период времени.

Рис. 2. Кэш-память

2.3.3. Используемый алгоритм свопинга

Разновидностью виртуальной памяти является свопинг.

На рисунке 2.2 показан график зависимости коэффициента

загрузки процессора в зависимости от числа одновременно выполняемых процессов и

доли времени, проводимого этими процессами в состоянии ожидания ввода-вывода.

Рис. 3. Зависимость загрузки процессора от

числа задач и интенсивности ввода-вывода

Из рисунка видно, что для загрузки процессора на 90%

достаточно всего трех счетных задач. Однако для того, чтобы обеспечить такую же

загрузку интерактивными задачами, выполняющими интенсивный ввод-вывод,

потребуются десятки таких задач. Необходимым условием для выполнения задачи

является загрузка ее в оперативную память, объем которой ограничен. В этих

условиях был предложен метод организации вычислительного процесса, называемый

свопингом. В соответствии с этим методом некоторые процессы (обычно находящиеся

в состоянии ожидания) временно выгружаются на диск. Планировщик операционной

системы не исключает их из своего рассмотрения, и при наступлении условий

активизации некоторого процесса, находящегося в области свопинга на диске, этот

процесс перемещается в оперативную память. Если свободного места в оперативной

памяти не хватает, то выгружается другой процесс.

При свопинге процесс перемещается между памятью и диском

целиком, то есть в течение некоторого времени процесс может полностью

отсутствовать в оперативной памяти.

2.3.4. Механизм отмены содержимого КЭШа и замещения

информации в КЭШе

В системах, оснащенных кэш-памятью, каждый запрос к

оперативной памяти выполняется в соответствии со следующим алгоритмом:

1.

Просматривается содержимое кэш-памяти с целью

определения, не находятся ли нужные данные в кэш-памяти; кэш-память не является

адресуемой, поэтому поиск нужных данных осуществляется по содержимому -

значению поля "адрес в оперативной памяти", взятому из запроса.

2.

Если данные обнаруживаются в кэш-памяти, то они

считываются из нее, и результат передается в процессор.

3.

Если нужных данных нет, то они вместе со своим адресом

копируются из оперативной памяти в кэш-память, и результат выполнения запроса

передается в процессор. При копировании данных может оказаться, что в

кэш-памяти нет свободного места, тогда выбираются данные, к которым в последний

период было меньше всего обращений, для вытеснения из кэш-памяти. Если

вытесняемые данные были модифицированы за время нахождения в кэш-памяти, то они

переписываются в оперативную память. Если же эти данные не были модифицированы,

то их место в кэш-памяти объявляется свободным.

В кэш-память считывается не один элемент данных, к которому

произошло обращение, а целый блок данных, это увеличивает вероятность так

называемого "попадания в кэш", то есть нахождения нужных данных в

кэш-памяти.

2.4. Оперативная память

2.4.1. Используемый способ расширения емкости оперативной

памяти

Для расширения емкости оперативной памяти используется виртуальная

память. Виртуальным называется ресурс, который пользователю или

пользовательской программе представляется обладающим свойствами, которыми он в

действительности не обладает. Так, например, может быть предоставлена

виртуальная оперативная память, размер которой превосходит всю имеющуюся в

системе реальную оперативную память. Программы пишутся так, как будто в их

распоряжении имеется однородная оперативная память большого объема, но в

действительности все данные, используемые программой, хранятся на одном или

нескольких разнородных запоминающих устройствах, на дисках, и при необходимости

частями отображаются в реальную память.

Таким образом, виртуальная память - это совокупность программно-аппаратных

средств, позволяющих использовать программы, размер которых превосходит

имеющуюся оперативную память; для этого виртуальная память решает следующие

задачи:

·

размещает данные в запоминающих устройствах

разного типа, например, часть программы в оперативной памяти, а часть на диске;

·

перемещает по мере необходимости данные между

запоминающими устройствами разного типа, например, подгружает нужную часть

программы с диска в оперативную память;

·

преобразует виртуальные адреса в физические.

Все эти действия выполняются автоматически, без

участия программиста, то есть механизм виртуальной памяти является прозрачным

по отношению к пользователю.

2.4.2. Максимальный объем расширенной памяти

Максимальный размер виртуального адресного пространства ограничивается

разрядностью адреса, присущей данной архитектуре компьютера, и не совпадает с

объемом физической памяти, имеющимся в компьютере.

2.4.3. Используемые типы адресов

Для идентификации переменных и команд используются

символьные имена (метки), виртуальные адреса и физические адреса (рисунок 3.1).

Символьные имена присваивает пользователь при написании

программы на алгоритмическом языке или ассемблере.

Виртуальные адреса вырабатывает транслятор, переводящий

программу на машинный язык. Так как во время трансляции в общем случае не

известно, в какое место оперативной памяти будет загружена программа, то

транслятор присваивает переменным и командам виртуальные (условные) адреса,

обычно считая по умолчанию, что программа будет размещена, начиная с нулевого

адреса. Совокупность виртуальных адресов процесса называется виртуальным

адресным пространством. Каждый процесс имеет собственное виртуальное

адресное пространство. Максимальный размер виртуального адресного пространства

ограничивается разрядностью адреса, присущей данной архитектуре компьютера, и,

как правило, не совпадает с объемом физической памяти, имеющимся в компьютере.

Рис. 4. Типы адресов

Физические адреса соответствуют номерам ячеек оперативной

памяти, где в действительности расположены или будут расположены переменные и

команды. Переход от виртуальных адресов к физическим может осуществляться двумя

способами. В первом случае замену виртуальных адресов на физические делает

специальная системная программа - перемещающий загрузчик. Перемещающий

загрузчик на основании имеющихся у него исходных данных о начальном адресе

физической памяти, в которую предстоит загружать программу, и информации,

предоставленной транслятором об адресно-зависимых константах программы,

выполняет загрузку программы, совмещая ее с заменой виртуальных адресов

физическими.

2.5. Система контроля

2.5.1. Система контроля памяти по Хэммингу

Параллельные ЭВМ, в частности, многопроцессорные, наряду с

высоким быстродействием естественным образом обеспечивают высокую надежность и

отказоустойчивость вычислений. Это достигается за счет многоэлементности

(многопроцессорности) и способности к реконфигурации этих ЭВМ. В этом параграфе

надежность и отказоустойчивость рассматриваются преимущественно в отношении

оборудования, а не программного обеспечения.

Приведем некоторые сведения из теории надежности,

необходимые для дальнейшего рассмотрения.

Надежность определяется как свойство технического

изделия выполнять заданные функции в течение требуемого времени.

Основным понятием теории надежности является отказ,

под которым понимают случайное событие, нарушающее работоспособность изделия.

Применительно к вычислительной технике различают два вида отказов: устойчивые

(собственно отказы) и самоустраняющиеся (сбой, перемежающиеся отказы). Сбой

возникает вследствие одновременного неблагоприятного изменения нескольких

параметров и существует кратковременно. Перемежающиеся отказы могут возникать,

например, при плохом контакте в соединителе. Сбои встречаются в ЭВМ наиболее

часто.

Основными параметрами надежности для невосстанавливаемых

изделий являются интенсивность отказов λ, вероятность

безотказной работы P(t), среднее время безотказной работы T:

Здесь m - число изделий, отказавших за время t,

а N - число исправных элементов на начало промежутка времени.

Следовательно, λ определяет долю (а не количество) изделий, отказавших в

единицу времени, в качестве которой обычно принимают один час. Интенсивность

принимается постоянной на этапе нормальной эксплуатации изделий.

Для микросхем обычно λ =10-6...10-8

1/час, поэтому среднее время безотказной работы большое: T=106...108

часов. Но в ЭВМ обычно входят тысячи микросхем. Поскольку

где λЭВМ, λi -

интенсивность отказов ЭВМ и микросхемы соответственно, а N - число

микросхем в составе ЭВМ, то время безотказной работы ЭВМ может составлять всего

десятки или сотни часов.

Для восстанавливаемых систем наиболее важным параметром

является наработка на отказ tср. Если восстановление является

полным, то время наработки на отказ tср восстанавливаемой

системы соответствует времени безотказной работы T невосстанавливаемой

системы.

По назначению вычислительные системы, к которым относятся и

многопроцессорные ЭВМ, можно разделить на две группы: системы для управления в

реальном масштабе времени и информационно-вычислительные системы. Для первых

отказ может вызвать тяжелые последствия, поэтому одним из основных показателей

эффективности таких систем является надежность. Вторые не критичны к отказу,

основным показателем их эффективности является производительность.

Рассмотрим показатели надежности ЭВМ, применяемых для систем

управления в реальном времени. Как говорилось выше, наработка на отказ ЭВМ

невысока. Основной способ повысить ее - резервирование. Различают

два вида резервирования: общее и поэлементное. При общем резервировании

резервируется вся ЭВМ, т. е. в случае выхода из строя она заменяется такой же.

При поэлементном резервировании резервируются отдельные части ЭВМ (процессоры,

каналы) и в случае отказов они заменяются идентичными. Наиболее употребительным

является постоянное (горячее) резервирование, при котором резервное устройство

выполняет ту же нагрузку, что и основное, и при отказе последнего резервное

устройство без задержки замещает основное. Число резервных устройств может быть

более одного.

Общее резервирование значительно повышает надежность

системы, в частности для системы без восстановления вероятность безотказной

работы Pрез(t) равна:

где P(t) - вероятность безотказной работы одной ЭВМ,

а m - число ЭВМ в системе. Так, если P(t) = 0,9, а m = 2

(используется дублирование), то Pрез(t) = 0,99. Для

восстанавливаемых систем и при m = 3...4 резервирование позволяет

достичь характеристик, близких к идеальным.

Однако, резервирование неэкономично, так как объем

оборудования возрастает в m раз, а производительность остается на уровне

одной ЭВМ. Такую систему нельзя назвать и параллельной, поскольку в последней

каждая ЭВМ выполняет независимую работу. Значительно эффективнее поэлементное

резервирование, которое прямолинейно реализуется структурой многопроцессорной

ЭВМ.

Пусть многопроцессорная ЭВМ содержит m одинаковых

процессоров, l из которых являются избыточными. Избыточный процессор

полноценно заменяет любой из основных в случае отказа последнего, то есть

реализуется плавающее резервирование. Каждый из основных процессоров выполняет

независимую часть работы.

Пусть процессор имеет интенсивность отказов λ и

интенсивность восстановления μ (μ = 1/Tμ , где

Tμ - среднее время восстановления процессора). В этом

случае средняя наработка на отказ многопроцессорной системы с l

резервными элементами:

Так как 1/(mλ) - наработка на отказ неизбыточной

ЭВМ, то при малых l выигрыш надежности избыточной ЭВМ будет:

В практически важных случаях μ/λ>>1,

тогда G [μ/(mλ)]l.

Для ЭВМ обычно μ/(mλ)≥100, то уже при l=2 или 3

наработка на отказ избыточной ЭВМ будет приближаться к границе долговечности.

[μ/(mλ)]l.

Для ЭВМ обычно μ/(mλ)≥100, то уже при l=2 или 3

наработка на отказ избыточной ЭВМ будет приближаться к границе долговечности.

Система с плавающим резервированием должна обладать

способностью к реконфигурированию.

Все вышеприведенное относилось к системам управления

реального времени, которые можно определить как двухпозиционные системы:

работает - не работает. Именно для таких систем основной характеристикой

функционирования является надежность.

Информационно-вычислительные системы являются

многопозиционными. Функции, выполняемые этими системами, можно разделить на

основные и второстепенные. Если отказ одного из элементов делает невозможным

выполнение одной из второстепенных функций, это не препятствует дальнейшему

функционированию системы. Если же отказ затрагивает исполнение основной

функции, то в результате автоматической реконфигурации выполнение этой основной

функции передается на оставшиеся работоспособные элементы (возможно, с

вытеснением второстепенных функций). В таких системах возможен отказ более чем

одного элемента при сохранении работоспособности системы. После восстановления

отказавших элементов система будет выполнять функции в полном объеме.

Восстановление производится в процессе функционирования системы.

Системы, обладающие вышеуказанными свойствами, называют

отказоустойчивыми (толерантными, "живучими").

Очевидно, для отказоустойчивых систем не подходит понятие

отказа в вышеописанном случае, а надежность не является основным показателем

эффективности. В таких системах отказом следует считать такой отказ элементов

системы (в общем случае многократный), который вызывает поражение одной из

основных функций. Что касается эффективности, то для

информационно-вычислительных систем одним из основных ее показателей является

производительность, которую можно определить выражением:

где Vc - средняя производительность

системы, V - производительность одного элемента системы (процессора), m

- максимальное число элементов в системе, i - число элементов в

конфигурации, pi - вероятность этой конфигурации.

Системы с восстановлением имеют существенно лучшее

распределение вероятностей pi, чем системы без

восстановления.

Частным случаем отказоустойчивых систем являются системы с

постепенной деградацией, в которых ремонт и восстановление невозможны или по

каким-либо причинам нецелесообразны. Такие системы продолжают функционировать

до тех пор, пока число работоспособных элементов не достигнет минимально

допустимого уровня.

Центральным качеством надежных и отказоустойчивых систем

является автоматическая реконфигурация. Реконфигурация возможна, если в

многопроцессорной ЭВМ имеются аппаратные и программные средства контроля и

диагностики, реконфигурации и повторного запуска системы после отказа

(рестарта).

Средства контроля могут быть реализованы аппаратным,

программным или смешанным способом. Аппаратные средства контроля предназначены

для контроля передачи информации и кон-троля правильности выполнения

арифметико-логических операций.

Контроль путей пересылки информации (память - АЛУ, память -

ВнУ и др.) производится на основе избыточного кодирования (коды Хэмминга, Грея

и др.). Особенное распространение имеет простой код с проверкой четности,

требующий только одного дополнительного разряда на блок двоичных разрядов

(обычно восьми). Эти же методы и дублирование блоков используется для контроля

операций в АЛУ. Аппаратный контроль выполняется в темпе основных вычислений,

что и является основным его достоинством.

Программный контроль не требует дополнительного

оборудования, однако он выполняется с задержкой во времени. К программным

методам контроля относятся тестовый и программно-логический контроль. Тестовый

контроль выполняется периодически, либо при наличии свободного времени в ЭВМ,

либо после обнаружения отказа другими средствами. В этом случае тестовый

контроль частично выполняет функции диагностики. Примерами

программно-логического контроля являются: двойной просчет, решение задачи по

основному и упрощенному алгоритму, проверка предельных значений переменных и

др.

Аппаратной основой реконфигурации является наличие развитой

системы коммутации, позволяющей исключать из структуры многопроцессорной ЭВМ

неисправные элементы в случае отказов и устанавливать новые связи между

исправными элементами. Разработано большое количество типов коммутаторов. Наиболее

перспективными являются коммутаторы типа многомерный куб. Следует отметить, что

коммутаторы являются неотъемлемыми элементами как параллельных, так и

отказоустойчивых ЭВМ.

К системному и прикладному программному обеспечению

отказоустойчивой ЭВМ предъявляются следующие требования:

1.

Вся адресация памяти, ВнУ, каналов должна выполняться

на логическом уровне. В этом случае отказ элемента приводит только к изменению

таблиц связи логических и физических адресов.

2.

Операционная система должна носить распределенный

характер, то есть в процессорах должны находиться копии ОС или ее частей.

В наибольшей степени этим условиям удовлетворяют

параллельные ЭВМ типа МКМД с децентрализованным управлением.

Для обеспечения рестарта в процессе вычислений необходимо

создавать контрольные точки, то есть запоминать результаты вычислений. Рестарт

осуществляется с ближайшей контрольной точки. Чем чаще устанавливаются

контрольные точки, тем меньше времени будет потрачено на повторение вычислений

в процессе рестарта, однако создание контрольных точек также требует

дополнительного времени.

2.5.2. Система контроля ввода – вывода по паритету

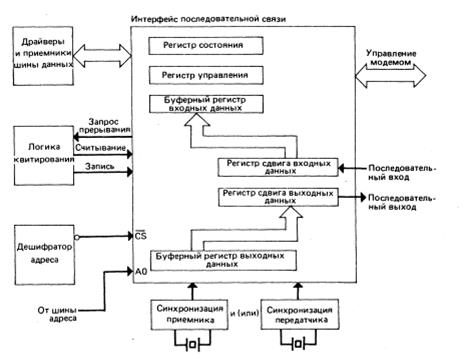

Многие устройства

ввода-вывода передают информацию в или из компьютера последовательно, т. е. по

одному биту, по паре проводников, причем каждый бит занимает определенный

временной интервал. Типичная конфигурация последовательного интерфейса показана

на рис. 3. Регистр состояния содержит информацию о состоянии текущей передачи

(например, об ошибках), а регистр управления хранит информацию о режиме работы

интерфейса. Буфер входных данных подключен к регистру сдвига с последовательным

входом и параллельным выходом. В операции ввода биты по одному подаются в

регистр сдвига, а после приема символа информация передается в буферный регистр

входных данных и ожидает ввода в ЦП. (Обычно одним данным является

буквенно-цифровой символ, который далее называется просто символом, но это не

обязательно.) Буферный регистр выходных данных аналогично подключен к регистру

сдвига с параллельным входом и последовательным выходом. Вывод осуществляется

выдачей данных в буфер выходных данных, передачей их в регистр сдвига и

последующим сдвигом данных на последовательную выходную линию.

Хотя имеется несколько

способов адресации четырех регистров порта, будем полагать, что из регистра

состояния можно только считывать, а в регистр управления — только записывать.

Следовательно, активный сигнал на линии считывания идентифицирует либо регистр

состояния, либо буферный регистр входных данных, а линию АО можно использовать

для различения этих регистров. Аналогично сигналы записи и АО допускают выбор

одного из остальных двух регистров.

Рис. 3. Последовательный интерфейс

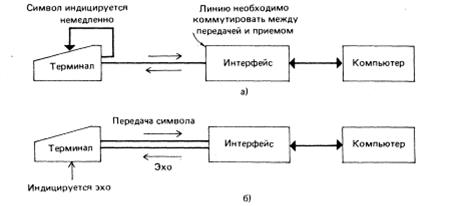

Интерфейс на рис. 3

имеет отдельные линии для передачи и приема информации. Когда для двух

направлений сигналов применяются различные линии, связь называется дуплексной. Такая система может

передавать и принимать одновременно. Терминалы и другие последовательные устройства,

подключенные к компьютеру дуплексной системой, обычно посылают каждый символ в

компьютер без его индикации. Компьютер сразу же посылает символ обратно (как

эхо) и терминал индицирует его. Потерь времени при этом не возникает, так как

эхо-символы можно передавать одновременно с вводом в компьютер новых символов.

Пользователь осуществляет визуальную проверку не только того, что он ударил по

правильной клавише, но и того, что компьютер получил правильный символ. В полудуплексной связи для ввода и вывода применяется

одна и та же линия. Здесь напечатанный на терминале символ индицируется

одновременно с передачей в компьютер и принцип эхо-печати не применяется. Если

компьютер принимал символы, а затем "хочет" передавать их (или

наоборот), линию связи необходимо скоммутировать, на что уходит некоторое

время. Хотя дуплексная связь и не требует коммутации и обеспечивает

эхо-передачу, для нее нужна дополнительная линия. Два рассмотренных режима

связи иллюстрируются рис. 4. Многие терминалы и интерфейсы допускают коммутацию

для полудуплексной связи и имеют отдельные контакты для дуплексной связи. Если

устройство, например принтер, требует только односторонней связи, достаточно

полудуплексной связи, а коммутация не нужна.

Рис.

4. Основные режимы передачи полудуплексный (а) и дуплексный (б)

Имеются два основных

вида последовательной связи. При асинхронной

последовательной связи символы разделяются специальными двоичными наборами,

а при синхронной должны быть

специальные символы "синхронизации" в начале каждого сообщения и

специальные "холостые" символы для "заполнения времени",

когда информация не передается. Асинхронная передача допускает любые промежутки

между символами, а в синхронной передаче символы должны точно размещаться, даже

если некоторые символы не содержат информации. Максимальная скорость передачи

информации синхронной линии выше, чем асинхронной линии с той же двоичной

скоростью, так как при асинхронной передаче каждый символ содержит

дополнительные биты. С другой стороны, частоты синхронизации передатчика и

приемника могут быть не точно одинаковыми (пока они находятся в допустимых

пределах), так как специальные наборы допускают ресинхронизацию в начале каждого

символа. При синхронной передаче действия должны быть синхронными, так как

именно это определяет положение каждого бита. Следовательно, помимо данных

требуется передавать сигналы синхронизации.

2.5.3. Асинхронная связь

Формат асинхронного

символа на рис. 4 показывает, что символ содержит закодированную информацию и

несколько дополнительных бит. До начала передачи символа линия должна

находиться в состоянии 1, которое часто называется состоянием маркера. Переход из этого состояния в

состояние 0, или пробел, отмечает

начало символа. Первый бит всегда содержит 0 и называется стартовым битом. Затем следуют 5-8 информационных битов, первым из

которых является младший бит символа. После информационных бит находится

необязательный бит четного или нечетного паритета. Число последних стоповых бит может быть 1, 1 1/21

или 2.

Хотя число

информационных бит, тип паритета (если он есть) и число стоповых бит могут

изменяться от одной передачи (т. е. последовательности символов) к другой, эти

параметры в одной передаче являются константами. В некоторых интерфейсах

параметры программируются с помощью регистров управления, а в других

определяются положениями переключателей. Если параметры программируются, в

интерфейсе появляется регистр управления, аналогичный показанному на рис. 9.5.

В нем биты 0 и 1 определяют число стоповых бит, биты 2 и 3 — число

информационных бит, а бит 4 показывает наличие или отсутствие бита паритета.

Если бит 4 содержит 1, бит 5 определяет тип паритета.

Рис.

5. Формат стандартной асинхронной передачи

Рис.

6. Типичный регистр управления для определения формата символа

В передатчике необходим

генератор синхронизации, определяющий интервал каждого бита посредством

регулирования временных отрезков между сдвигами в регистрах сдвига. После

выдвигания всех бит передатчик обычно выводит маркер, пока не будет готов к

передаче следующий символ. В приемнике также необходим генератор синхронизации

для измерения интервала между сдвигами, так чтобы входной сигнал опрашивался в

правильные моменты. Обычно частоты генераторов в 16, 32 или 64 раза больше двоичной

частоты. Если множитель равен 16, после обнаружения перехода 1 ->0 в начале символа приемник должен

отсчитать 8 импульсов синхронизации и опросить вход. При обнаружении 0 он

считает, что переход вызван стартовым битом, а не помехой. Затем приемник опрашивает

вход через интервалы в 16 периодов импульсов синхронизации до .ввода всех бит

символа, включая и стоповые биты, после чего он прекращает опрос и ожидает

следующего перехода 1 -> 0. Важно отметить, что ЦП не выдает и не принимает

стартовый и стоповый биты, а также бит паритета. При выводе передатчик вводит

эти биты в каждый символ, а при вводе приемник удаляет их из принятых данных.

Такой формат позволяет

передатчику вводить между символами промежутки любой длины, а приемнику

ресинхронизировать себя в начале каждого символа. Без этого механизма

ресинхронизации два генератора выйдут из режима синхронизации и приемник будет

опрашивать вход неправильно. При наличии ресинхронизации приемник должен

учитывать скорость передачи бит только для одного символа. Неправильный опрос

возникает только тогда, когда две частоты синхронизации столь различны, что

сдвиг в приемнике выполняется в неверный момент времени уже через несколько бит

после стартового бита. Если же это происходит, появляется большая вероятность того,

что приемник обнаружит нулевой бит на месте стопового. Когда вместо стопового

бита обнаруживается 0, возникает так называемая ошибка кадра. Таким образом, большинство асинхронных

последовательных интерфейсов должны обнаруживать три вида ошибок: паритета,

перегрузки и кадра.

Сигналы синхронизации

передачи и приема, которые определяют временные соотношения в интерфейсе, не

обязательно должны быть одними и теми же и не обязательно должны иметь

одинаковую частоту. Но имеются очевидные достоинства в единой синхронизации для

формирования всех необходимых в интерфейсе импульсов синхронизации. Если

двоичные скорости передачи и приема различны, электронные схемы на другом конце

линии связи должны быть рассчитаны на работу с двумя скоростями. Скорость

приема в этих схемах должна соответствовать скорости передачи интерфейса и

наоборот.

Устройства, которые

выполняют прием и передачу данных в формате рис. 6,

параллельно-последовательное и последовательно-параллельное преобразования и

обнаруживают ошибки паритета, перегрузки и кадра, называются универсальными асинхронными приемопередатчиками (УАПП

или UART). Многие фирмы выпускают

микросхемы УАПП и их разработки стандартизованы. Усилия фирм, выпускающих

микропроцессоры, направлены на разработки законченных и универсальных

интерфейсов. Иногда УАПП является только небольшой частью интерфейса, который

может реализовать большинство видов связи.

2.5.4. Синхронная связь

Передаваемый синхронно

символ также состоит из 5-8 бит с необязательным битом паритета, но не имеет

стартового и стоповых бит. Все символы содержат одинаковое число бит n и

время передачи разделяется на интервалы из n бит каждый. Опросом в приемнике управляет та же

самая синхронизация, которая применяется для генерирования бит, что гарантирует

синхронность двух процессов. Передатчик должен передавать символ в течение

каждого п -битного интервала. Если

символ к началу интервала отсутствует, возникает недогрузка и передатчик вводит

холостой символ. В зависимости от системы приемник может интерпретировать холостые

символы как ошибки недогрузки.

Проблемы запуска или

коммутации в асинхронной системе не существует, так как. передатчик просто

выдает в линию маркер до готовности начала передачи. Если помеха вызывает

случайный переход 1 -> 0, фиксируется ложный сигнал, когда первый опрос не

обнаруживает стартового бита, и система ожидает следующего перехода 1 -> 0.

В синхронной передаче проблема запуска после включения или другого нарушения

оказывается более сложной. Все передачи должны начинаться с серии символов синхронизации,

которые нельзя спутать с другими символами. Обычно они совпадают с холостыми

символами; в коде ASCII символ

синхронизации кодируется как 0010110.

Приемник, который должен

знать код символа синхронизации, проверяет каждый бит по мере его появления и,

когда последовательность бит точно соответствует битам в символе синхронизации,

полагает, что началась передача. Затем он считает следующие символы

передаваемой информацией или пытается соотнести один или несколько из них с

символом синхронизации. Так как помеха может вызвать ложную идентификацию

символа синхронизации, в большинстве систем требуется, чтобы передача

начиналась серией символов синхронизации. В этом случае приемник не фиксирует

начала передачи до поступления нужного числа символов синхронизации. Ненужные

холостые символы и символы синхронизации удаляет приемник или программа ввода.

Допускается

программирование числа информационных бит, наличия и вида паритета, числа и

кодов символов синхронизации. В интерфейсе потребуются специальные регистры для

хранения символа синхронизации и другой информации о формате.

3. Заключение

В данной работе рассматривалась разработка структурной и

принципиальной схем ЭВМ.

Было детально рассмотрено использование прерываний, а

именно, такие аспекты, как:

·

формирование прерываний и передача в ЦПУ вектора

прерываний;

·

возврат из прерываний;

·

запоминание и восстановлений состояния

прерываемой программы;

·

управление приоритетами.

Относительно работы с КЭШ рассматривались следующие вопросы:

·

работу центрального процессора при удачном и

неудачном обращении к КЭШ;

·

структурная организация КЭШ;

·

использование свопинга;

·

механизм отмены содержимого КЭШ и замещение

информации, содержащейся в КЭШ.

По работе оперативной памяти рассматривалось:

·

способ расширения емкости оперативной памяти;

·

максимальный объем оперативной памяти;

·

используемые типы адресов.

По системе ввода – вывода рассматривались:

·

управление вводом выводом;

·

физическая организация устройств ввода – вывода;

·

программное обеспечение ввода – вывода.

4. Используемая литература

1.

Дейтел Г.

Введение в операционные системы. В 2-х томах. М.: Мир, 1987 г.

2.

Краковяк С. Основы организации и функционирования ОС

ЭВМ. М.: Мир, 1988 г.

3.

Олифер Н. А.,

Олифер В. Г. Сетевые

операционные системы СПб.:Питер, 2002.

4.

Гордеев А.В., Молчанов А.Ю. Системное программное

обеспечение СПб.:Питер, 2002.-736с.

5.

Иртегов Д.В.

Введение в Операционные системы

СПб.:БХВ-Петербург, 2002.-624с.

6.

Жигарев А. Н.

Основы компьютерной грамоты. – Л.: Машиностроение. Ленинг. отд-ие, 1987

г.

7.

Кузнецов Е. Ю., Осман В. М. Персональные компьютеры и

программируемые микрокалькуляторы: Учеб. пособие для ВТУЗов. – М.: Высш. шк.,

1991 г.

8.

Растригин Л. А. С компьютером наедине. – М.: Радио и

связь, 1990 г.

9.

А.Марголис. Поиск и устранение неисправностей в

персональных компьютерах. - К.: фирма "Дианетика", 1994г.

10.

Уинн Л. Рош. Библия по модернизации персонального

компьютера. - Мн.: ИПП "Тивали-Стиль", 1995г.