Содержание

Введение..................................................................................................... 3

1. Основные компоненты ЭВМ................................................................. 4

1.1. Основная память (ОП). Структурная схема ОЗУ.......................... 4

1.2. Стековая память. Кэш-память первого, второго уровней............ 6

1.3. Эволюция микропроцессоров (МП). Основные технические характеристики

МП. Классификация МП...................................................... 8

1.4. Структурная схема микропроцессора......................................... 11

1.5. Полный цикл работы МП при выполнении команды................. 14

1.6. Система команд МП..................................................................... 16

1.6.1. Команды обращения к памяти.............................................. 17

1.6.2. Программирование на машинном языке.............................. 17

1.6.3. Структурная схема базовой модели микропроцессора фирмы Intel.................................................................................................................... 19

2. Организация прерываний в

микроЭВМ............................................ 20

Заключение.............................................................................................. 32

Введение

Целью данной курсовой работы является разработка основных

компонентов электронно-вычислительной машины (ЭВМ).

Основное внимание в работе будет уделено блоку системы

прерывания:

·

задача аппаратных средств обработки прерывания;

·

структура единой программы прерываний и ее связь с основной

программой.

·

обслуживание ВУ с помощью единой подпрограммы

·

организация системы прерываний в микроЭВМ

·

организацию векторной системы с интерфейсным

вектором

Помимо этого будут рассмотрены такие вопросы, как:

·

основная память;

·

стековая память;

·

структурная схема микропроцессора;

·

цикл работы микропроцессора;

·

организация прерываний.

1. Основные компоненты ЭВМ

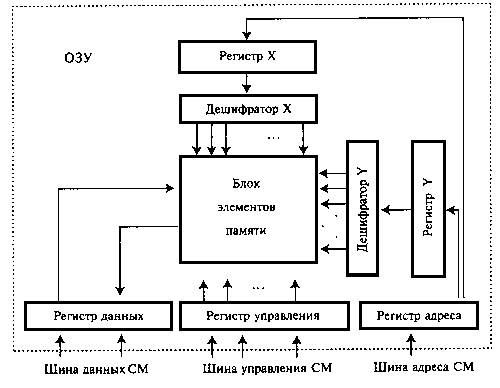

1.1. Основная память (ОП). Структурная схема ОЗУ

Комплекс технических средств, реализующих функции памяти,

называется запоминающим устройством (ЗУ). ЗУ делятся на основную память (ОП),

сверхоперативную память (СОЗУ) и внешние запоминающие устройств (ВЗУ). ОП

состоит из двух типов устройств :

·

оперативное ЗУ (ОЗУ или RAM - Random Accses Memory);

·

постоянное ЗУ (ПЗУ или ROM

- Read Only Memory).

Основной составной частью микросхемы памяти является массив

элементов памяти (ЭП). Каждый ЭП может хранить 1 бит информации. ЗУ,

позволяющее обращаться по адресу к любому ЭП в произвольном порядке, называется

ЗУ с произвольным доступом.

При матричной организации памяти адрес ЭП определяется двумя

координатами X и Y. На пересечении этих координат находится ЭП. Структурная

схема ОЗУ приведена на рис. 1.

Связь с ОЗУ осуществляется по системной магистрали (СМ). По

шине управления передается сигнал, определяющий, какую операцию необходимо

выполнить. ПО шине данных передается информация, записываемая в память или

считываемая из нее. По шине адреса передается адрес участвующих в обмене

элементов памяти (поскольку данные передаются машинными словами, а один элемент

памяти может воспринять только один бит информации, блок элементов памяти

состоит из n матриц ЭП, где n-количество разрядов в машинном слове).

Максимальная емкость памяти определяется количеством линий в шине адреса

системной магистрали: если количество линий обозначить через m, то емкость

памяти (т.е. количество элементов памяти, имеющих уникальных адреса)

определяется как  При 32

разрядной адресной шине максимальный обьем ОП равен

При 32

разрядной адресной шине максимальный обьем ОП равен

В зависимости от способа хранения информации ОЗУ

подразделяются на:

1.

Статические ОЗУ (SRAM - Static RAM).

2.

Динамические (DRAM - Dynamic RAM).

Рис.1. Структурная схема ОЗУ

В статических ОЗУ в качестве ЭП используется статический

триггер, который способен сохранять состояние 0 или 1 неограниченно долго (при

включенном ПК). Динамические ОЗУ строятся на конденсаторах, реализованные

внутри кристалла кремния. Динамические ЭП (конденсаторы) с течением времени

саморазряжаются и записанная информация теряется. Динамические ЭП требуют

периодического восстановления заряда - регенерации. Во время регенерации запись

новой информации должна быть запрещена.

Основными характеристиками ОЗУ являются время доступа

(быстродействие), емкость.

Время

доступа - это промежуток

времени, за который может быть записано или прочитано содержимое ячейки памяти

после подачи ее адреса и соответствующего управляющего сигнала.

Емкость

определяет количество ячеек или битов в устройстве памяти.

По сравнению со статическими, динамические ОЗУ имеют более

высокую удельную емкость и меньшую стоимость, но большее энергопотребление и

меньшее быстродействие. ОЗУ имеют модульную структуру. Увеличение емкости ОЗУ

производится установкой дополнительных модулей. Время доступа к модулям DRAM

составляет 60-70 нс.

На производительность ЭВМ влияет не только время доступа, но

и такие параметры, как тактовая частота и разрядность шины данных системной

магистрали. Если тактовая частота недостаточна высока, то ОЗУ простаивает в

ожидании обращения. При тактовой частоте, превышающей возможности ОЗУ, в

ожидании будет находиться системная магистраль, через которую поступил запрос в

ОЗУ.

Интегральной характеристикой производительности ОЗУ с учетом

частоты и разрядности шины данных является пропускная способность, которая

измеряется в Мегабайтах в секунду. Для ОЗУ с временем доступа 60-70 нс и разрядностью

шины данных 64 бита максимальная пропускная способность при тактовой частоте СМ

50 МГц составляет 400 Мбайт/с.

Микросхемы ПЗУ также построены по принципу матричной

структуры. Функции ЭП в них выполняют перемычки в виде проводников,

полупроводниковых диодов или транзисторов. В такой матрице наличие перемычки

соответствует "1", а ее отсутствие - 0. Запись информации в ПЗУ

осуществляется посредством программатора.

1.2. Стековая память. Кэш-память первого, второго

уровней

Сверхоперативные ЗУ используется для хранения небольших объемов

информации и имеют значительно меньшее время (в 2-10 раз) считывания/записи,

чем ОЗУ. СОЗУ обычно строятся на регистрах и регистровых структурах.

Если к любому регистру можно обратиться для записи/чтения по

его адресу, то такая регистровая структура образует СОЗУ с произвольным

доступом.

Безадресные регистровые структуры могут образовывать два

вида устройств памяти: магазинного типа и память с выборкой по содержанию

(ассоциативные ЗУ).

Если запись в регистровую структуру производится через один

регистр, а считывание - через другой, то такая память является аналогом

задержки и работает по принципу "первым вошел - последним вышел"

(FIFO-First Input, First Output).

Если же запись и чтение производится через один и тот же

регистр, то такое устройство называется стековой памятью, работающее по

принципу "первым вошел - последним вышел" (FILO-First Input, Last

Output).

Стековая память получила широкое распространение. Для ее

реализации в ОЗУ посредством программ операционной системы выделяется часть

памяти под стек. Специальный регистр МП (указатель стека) постоянно хранит

адрес ячейки ОЗУ, выполняющий функции вершины стека. Чтение числа всегда

производится из вершины стека, после чего указатель стека изменяется и

указывает на очередную ячейку стековой памяти.

В микропроцессорах ассоциативные ЗУ (память с выборкой по

содержанию) используются в составе кэш-памяти для хранения адресной части

команд и операндов исполняемой программы. При этом нет необходимости обращаться

к ОЗУ за следующей командой или требуемым операндом: достаточно поместить в

маску необходимый адрес, если искомая информация имеется в СОЗУ, то она сразу

будет выдана. Обращение к ОП будет необходимо лишь при отсутствии требуемой

информации в СОЗУ. За счет такого использования СОЗУ сокращается число

обращений к ОЗУ, а это позволяет экономить время, так как обращение к СОЗУ

требует в 2-10 раз меньше времени, чем обращение к ОЗУ.

Кэш-память может быть размещена в кристалле процессора (так

называемая "кэш-память I уровня") или выполнена в виде отдельной

микросхемы (внешняя кэш-память или кэш-память II уровня). Встроенная кэш-память

(I уровня) в процессорах Pentium имеет объём около 16 Кбайт, время доступа - 5

- 10 нс, работает с 32-битными словами и при частотах 75 - 166 МГц обеспечивает

пропускную способность от 300 до 667 Мбайт/с. внешняя кэш-память (II уровня)

имеет объём 256 Кбайт - 1 Мбайт, время доступа 15 нс, работает с 64-битными

словами при частоте 66 МГц обеспечивает максимальную пропускную способность 528

Мбайт/с

1.3. Эволюция микропроцессоров (МП). Основные

технические характеристики МП. Классификация МП

Микропроцессором (МП) называют полупроводниковый кристалл

или комплект кристаллов, на которых реализуется центральный процессор ЭВМ, т.е.

совокупность арифметико-логического устройства и центрального устройства

управления. В 1969 году компании Intel удалось создать комплект из четырех

интегральных микросхем (ИМС) с полным набором элементов характерным для

процессора. Длина слова первого МП составляла всего 4 бита. В 1971 г. был

выпущен 4-разрядный коммерческий МП Intel 4004, который стал применяться в

микрокалькуляторах. Уже в 1972г. появился 8-разрядный МП Intel 8008, а в 1947г.

- его улучшенный вариант Intel 8080. Он нашел применение в первых встроенных

ЭВМ для управления производственными процессами.

Развитие МП шло по разным направлениям, важнейшим из которых

-увеличение разрядности. Подавляющее большинство МП производимых в настоящее

являются однокристальными 32-разрядными, за исключением ряда 64-разрядных

комплектов. МП характеризуется :

·

тактовой частотой;

·

разрядностью;

·

архитектурой.

Тактовая

частота МП (более строго -тактовая частота, при которой способен

работать МП) определяется максимальным временем выполнения элементарного

действия в МП. Работа МП синхронизируется импульсами тактовой частоты от

задающего генератора. Чем выше тактовая частота МП (при прочих равных

условиях), тем выше его быстродействие.

Разрядностью

МП называют максимальное количество разрядов двоичного кода, которые

могут обрабатываться или передаваться одновременно. Понятие разрядность

включает:

·

разрядность внутренних регистров МП;

·

разрядность шины данных;

·

разрядность шины адреса.

От разрядности шины данных зависит скорость передачи

информации между МП и другими устройствами. Разрядность щины адреса определяет

адресное пространство МП.

Архитектура

МП является емким понятием, имеющим при этом неоднозначное

толкование. Архитектурой часто называют организацию МП с точки зрения

пользователя.

Можно ограничить рассмотрение архитектуры МП следующими элементами:

·

системой команд и способами адресации;

·

возможностью совмещения выполнения команд во

времени;

·

наличие дополнительных устройств и узлов в

составе МП;

·

режимами работы МП.

Система

команд представляет собой совокупность команд, которую способен

выполнить МП. Она включает полный список кодов операций, для каждой из которых

указывается число операндов и допустимые способы их адресации. Способы адресации определяют технику

вычисления адресов ячеек памяти и выполнения операций над адресными регистрами.

В соответствии с составом системы команд различают:

1.

МП с CISC-архитектурой (CISC-complex instruction set

computer-компьютер со сложной системой команд).

2.

МП с RISC-архитектурой (RISC-reduced instruction set

computer-компьютер с сокращенной системой команд).

МП с CISC-архитектурой являются традиционными, а их система

команд включает большое количество команд для выполнения арифметических и

логических операций, команд управления, пересылки и ввода-вывода данных.

Система команд МП с RISC-архитектурой упрощена и сокращена

до такой степени, что каждая команда выполняется за единственный такт. Такой

подход упростить структуру МП и тем самым повысить его быстродействие.

Некоторые наиболее развитые МП обеспечивают совмещение нескольких

последовательно расположенных команд во времени,

организуя конвейерную

обработку. Эта архитектурная особенность оказывает заметное влияние

на скорость выполнения линейных участков программ.

МП поддерживает широкий спектр режимов работы,

среди которых:

1.

Однопрограммный режим.

2.

Многопрограммный режим.

3.

Система виртуальных машин.

В однопрограммном режиме в каждый момент времени может

находиться в ОЗУ и выполняться только одна пользовательская программа.

В многопрограммный режиме обеспечивается хранение в ОЗУ

несколько программ и попеременное их выполнение с той или иной дисциплиной

обслуживания, что целесообразно главным образом при возможности совмещения во

времени счета в МП и операций ввода-вывода. На основе многопрограммного режима

работы МП могут быть организованы однопользовательский многопрограммный, а при наличии соответствующих аппаратных

средств - и многопользовательский

многопрограммный режим работы ПК. Система виртуальных машин является

дальнейшим развитием мультипрограммирования, основной признак которого -

возможность одновременной работы нескольких ОС.

1.4. Структурная схема микропроцессора

Микропроцессор (МП) выполнен на одном кристалле кремния в

виде одной интегральной схемы, в которой реализованы все основные функции

процессора.

Входящие в его состав компоненты говорят о том, что он

является процессором с программным управлением. Некоторые компоненты,

программный счетчик (счетчик команд СК), стек (на схеме не указан), регистр

команд (РК), служат для обработки команд. Такие компоненты

арифметико-логическое устройство (АЛУ), триггер переноса (на схеме не указан),

регистры общего назначения (РОН) и регистр адреса данных (РА), служат для

обработки данных. Все остальные компоненты, а именно дешифратор команд

(дешифратор кода операции ДКОп) и блок управления и синхронизации (БУ),

управляют работой других компонентов. Взаимодействие компонентов осуществляется

по внутренней шине данных. Связь МП с другими блоками (ЗУ и устройствами

ввода/вывода) происходит по адресной шине, шине данных (внешней) и управляющей

шине.

МП работает со словами, состоящими из 8 битов (1 байт).

Адрес из 8 бит позволяет адресовать  ячеек

памяти. Для реальных задач этого, конечно, мало, поэтому для задания адреса

памяти обычно используется 16 разрядов (два байта), и это позволяет прямо

адресовать

ячеек

памяти. Для реальных задач этого, конечно, мало, поэтому для задания адреса

памяти обычно используется 16 разрядов (два байта), и это позволяет прямо

адресовать  ячеек.

Адресная шина однонаправленная, 16-ти разрядная.

ячеек.

Адресная шина однонаправленная, 16-ти разрядная.

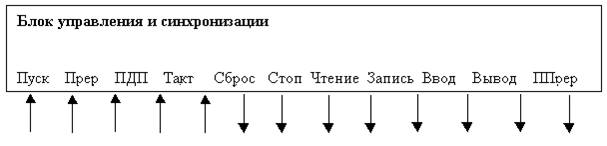

Рис 2. Структурная схема

гипотетического иллюстративного микропроцессора.

Информация к МП и от него передается по шине данных. Шина

данных двунаправленная, 8-ми разрядная. Управляющая шина состоит из 5 линий, ведущих

к блоку управления и синхронизации, и 8 выходящих из него линий. По этим линиям

передаются управляющие и тактирующие сигналы между компонентами МП и МП и

другими блоками ПК.

Счетчик

команд (СК) состоит из 16 битов и содержит адрес очередного байта команды,

считываемого из памяти. Содержимое СК автоматически увеличивается на единицу

после чтения каждого байта команды. Существует связь между СК и вершиной стека.

Одна из функций стека-сохранение адреса возврата из подпрограммы. В стеке могут

сохраняться данные из верхних трех регистров РОН и триггера переноса.

В то время как слово данных состоит из одного байта, команда

может состоять из одного, двух и трех байтов. Первый байт любой команды

поступает из ОЗУ по шине данных на регистр команд (РК). Этот первый байт

подается на вход дешифратора команд (ДКОп-дешифратор кода операции), который

определяет вид операции. В частности, дешифратор определяет является ли команда

однобайтовой, или она состоит из большего числа байтов. В последнем случае

дополнительные байты передаются по шинам данных из ОЗУ и принимаются или на

регистр адреса данных, или на один из регистров РОН

Регистр

адреса данных содержит адрес операнда для команд, обращающихся к

памяти, адрес порта для команд ввода/вывода. или адрес следующей команды для

команд перехода. Регистры РОН (регистры общего назначения) cодержат операнды

для всех команд, работающие с данными. Для указания этих регистров используются

4-битовые коды от 0000 до 1110. Регистр 0000 называется аккумулятором (АК) и

участвует во всех арифметических и логических операциях. В частности, он

содержит один из операндов перед выполнением операции и получает результат

после ее завершения. Обычно обращение к РОН осуществляется при помощи

R-селектора.

Все арифметические и логические операции выполняются в АЛУ.

Результаты из АЛУ передаются в аккумулятор по выходной 8-ми битовой шине.

Последний компонент МП - это блок управления и синхронизации. Он получает сигналы от дешифратора команд,

который анализирует команду. В БУ из АЛУ и от триггера переноса поступают

сигналы, по которым определяются условия для передачи управления. Все остальные

компоненты МП получают от БУ управляющие и синхронизирующие сигналы,

необходимые для выполнения команды. С помощью 13 внешних линий реализуется

интерфейс устройства управления с другими модулями ПК.

Рис 3. Шина управления

·

Указатель стека (УС) представляет собой

16-разрядный регистр, служащий для формирования адреса стековой памяти.

·

Регистр признаков (РП) используется для

фиксации определенных ситуаций, возникающих в результате выполнения операции.

Код ситуации называется признаком результата. Признак может принимать значение

0 или 1. Отметим некоторые из возможных признаков.

Признак переноса указывает на необходимость переноса единицы

при сложении двух восьмиразрядных чисел в младший значащий разряд следующего

байта. Признак нуля фиксирует появление нулевого результата операции, признак

знака - знак результата операции. Эти и другие признаки используются для

изменения хода обработки информации.

Буфер

данных (БД) служит для организации обмена

информацией между внутренней и внешней шинами данных.

1.5. Полный цикл работы МП при выполнении команды

Выборка каждого байта команды производится в два этапа.

1. На первом этапе адрес байта

команды, содержащийся в СК, передается в РА, а затем по адресным шинам в ОЗУ,

где происходит выбор адресуемого байта.

2. На втором этапе - передача

содержимого адресуемого байта по шинам данных в МП и увеличение содержимого СК

на 1. При этом, если выбирается не последний байт команды то новое новое

содержимое СК будет представлять адрес следующего байта текущей команды, а если

выбирается последний байт, то адрес первого байта следующей команды.

3. При выборке первого байта

команды его содержимое передается и фиксируется в РК.

4. Дешифратор кода операции по

содержимому РК, поступающему на его вход, определяет вид операции, число байтов

в команде, а также способ адресации, используемый в команде.

5. В соответствии с видом

операции БУ задает необходимую последовательность управляющих воздействий,

приводящих к выборке следующих байтов команды или к использованию команды.

Пример. Описать процесс выборки и

исполнения команды, по которой содержимое регистра РОН суммируется с содержимым

аккумулятора А. Результат операции фиксируется в аккумуляторе. Команда

однобайтовая с прямой регистровой адресацией. В коде команды  первые пять старших разрядов определяют код

операции; три последних - код адреса регистра C. Команда записана в ячейку ОЗУ

с адресом (номером)

первые пять старших разрядов определяют код

операции; три последних - код адреса регистра C. Команда записана в ячейку ОЗУ

с адресом (номером)  Число

Число  записано в

регистр C РОН. В аккумулятор A записано число

записано в

регистр C РОН. В аккумулятор A записано число

Процесс

выборки и исполнения команды можно условно разбить на несколько этапов:

1.

Адрес команды 017616 записывается в РА.

2.

Адрес команды из РА по шине адреса поступает ОЗУ.

3.

ОЗУ находит ячейку с указанным адресом и считывает

команду в буферный регистр ОЗУ.

4.

Команда из буферного регистра ОЗУ по внешней шине

данных, буфер данных (БД), внутренней шине данных поступает в РК.

5.

ДКОп распознает, что выборка команды закончена и над

содержимым аккумулятора и регистра С РОН необходимо произвести суммирование.

6.

Содержимое РА увеличивается на единицу и формируется

адрес следующей ячейки ОЗУ

7.

БУ вырабатывает последовательность сигналов, под

воздействием которых числа  из

аккумулятора и

из

аккумулятора и  из регистра C РОН поступают в АЛУ. АЛУ

производит операцию суммирования

из регистра C РОН поступают в АЛУ. АЛУ

производит операцию суммирования

8.

Результат операции записывается в аккумулятор, замещая

в нем прежнее число

9.

Выполнение

команды закончено. Начинается выборка следующей команды с адресом

1.6. Система команд МП

Микропроцессор имеет базовую систему команд, в состав

которой входят следующие группы:

·

команды пересылки данных:

·

команды пересылки данных внутри МП (MOV, PUSH, POP, XCHNG и

т.д.);

·

команда ввода-вывода (IN, OUT);

·

операции с флагами;

·

операция с адресами (LEA, LDS и т.д.);

·

арифметические команды:

·

основные (сложение, вычитание, умножение, деление);

·

дополнительные (INS, DEC и др.);

·

логические команды (сдвиг, дизъюнкция, конъюнкция, отрицание

равнозначности и др.);

·

команды обработки строковых данных (пересылка, сравнение,

сканирование, слияние/разделение и др.);

·

команды передачи управления (безусловный переход, условный

переход, прерывания, переход с возвратом);

·

команды управления ("нет операций", "внешняя

синхронизация" и т.д.).

каждая

команда имеет большое число модификаций, чаще всего определяемых режимом

адресации данных (операндов).

1.6.1. Команды обращения к памяти

Команда: LOAD REGISTR (загрузка регистра)

Символическая форма: LDR r

Описание: (М[< B2 > < B3 > ])r

Содержимое ячейки памяти передаётся в общий регистр r.

Старшие 8 разрядов адреса ячейки берутся из второго байта

команды, а младше 8 разрядов - из третьёго байта.

1.6.2. Программирование на машинном языке.

Программа должна быть представлена в той форме, в которой её

воспринимает машина. В частности, команды должны быть представлены в виде

последовательностей из нулей и единиц, поскольку это единственная понятная ЭВМ

форма. Однако выписывать длинные последовательности из нулей и единиц довольно

утомительно. Поэтому при записи команд применяется более удобная

шестнадцатеричная система.

Например, трёх битовая команда иллюстрированного процессора,

загружается в аккумулятор содержимое ячейки памяти с адресом 0110 1111 1101  имеет вид

имеет вид

01110000

01101111

11011011

в шестнадцатеричных обозначениях эта команда запишется так

70

6F

DB

Двоичное и шестнадцатеричное представление машинного языка

неудобно и ненаглядно для человека. Поэтому, как правило, команды

представляются в символической форме - используются легко запоминаемые

мнемонические обозначения команд. Например, предыдущую программу можно записать

в виде

LDR 0

6F

DB

Второй и третий байты по-прежнему записаны

шестнадцатеричными цифрами, и аккумулятор задан своим номером среди общих

регистров, равным 0. Однако операция обозначена трёхбуквенным мнемоническим

именем LDR.

Пример программы, в которой к числу, находящемуся в

ячейки  главной

памяти, прибавляется шестнадцатеричная константа 3С. программа приведена в

табл. 1. Она выполняется следующим образом.

главной

памяти, прибавляется шестнадцатеричная константа 3С. программа приведена в

табл. 1. Она выполняется следующим образом.

Таблица

1. Пример программы: "прибавить константу к числу в памяти и записать

результат снова в память"

Прежде всего, подаётся прежний импульс на линию

"сброс" БУ, по которому на программный счётчик устанавливается 0.

Затем подаётся импульс на линию "пуск" БУ, и начинается выполнение

программы. Выбираются 3 байта, составляющие первую команду, и программный

счётчик увеличивается на 1 после выборки каждого байта. Первая команда

пересылает содержимое ячейки памяти 000А в аккумулятор. Поскольку программный

счётчик подвинулся на 3 единицы, он теперь содержит 0003. Это адрес следующей

команды - загрузки регистра с непосредственным адресом. Команда содержит в себе

операнд и удобна для задания константы. Её выполнение приводит к засылке

значения 3С, содержащегося во втором байте команды, в общий регистр 1. Теперь

программный счётчик содержит 0005, т.е. адрес третьей команды. Её выборка и

выполнение приводит к прибавлению содержимого регистра 1 к содержимому аккумулятора

и занесению суммы в аккумулятор. Следующая команда передаёт содержимое

аккумулятора в ячейку памяти 000В. последняя команда останавливает

микропроцессор.

1.6.3. Структурная схема базовой модели

микропроцессора фирмы Intel

Условно МП можно разделить на две части : исполнительный

блок (Еxecution Unit- EU) и устройство сопряжения с системной магистралью (Bus

Interface Unit-BIU).

Арифметический блок включает арифметико-логическое

устройство, вспомогательные регистры для хранения операндов и регистр флагов.

Восемь регистров исполнительного блока МП

(AX,BX,CX,DX,SP,BP,SI,DI), имеющих длину, равную машинному слову, делятся на

две группы. Первую группу составляют регистры общего назначения: AX,BX,CX и DX,

каждый из которых представляет собой регистровую пару, составленную из двух

регистров длинной в 1 байт: аккумулятор, или регистр AX состоит из регистров AH

и Al. Регистр базы (Base Register) BX состоит из регистров BH и BL. Счетчик

(Count RegiSter) CX включает регистры CH и CL. Регистры данных (Data Register) DX

содержит регистры DH и DL. Каждый регистров может использоваться самостоятельно

или в составе регистровой пары.

Вторую группу составляют адресные регистры SP,BP,SI и DI (в

старших моделях количество адресных регистров увеличено).

Устройство сопряжения с системной магистралью содержит

управляющие регистры, конвейер команд, АЛУ команд, устройство управление

исполнительным блоком МП и интерфейс памяти (соединяющий внутреннюю магистраль

МП с системной магистралью ПК).

Управляющие регистры BIU: CS (указатель командного сегмента

), DS (указатель сегмента данных), SS (указатель сегмента стека), ES(указатель

дополнительного сегмента) и др. служат для определения физических ОП-операндов

и команд.

Регистр IP (Instruction Point) является указателем адреса

команды, которая будет выбираться в конвейер команд в качестве очередной

команды. Конвейер команд хранит несколько команд, что позволяет при выполнении

линейных программ совместить подготовку очередной команды с выполнением

текущей.

К управляющим регистрам МП относится и регистр флагов,

разряд которого имеет строго определенное назначение.

2. Организация прерываний в микроЭВМ

Одной из разновидностей программно-управляемого обмена

данными с ВУ в микроЭВМ является обмен с прерыванием программы, отличающийся от

асинхронного программно-управляемого обмена тем, что переход к выполнению

команд, физически реализующих обмен данными, осуществляется с помощью

специальных аппаратных средств. Команды обмена данными в этом случае выделяют в

отдельный программный модуль - подпрограмму обработки прерывания. Задачей

аппаратных средств обработки прерывания в процессоре микроЭВМ как раз и

является приостановка выполнения одной программы (ее еще называют основной

программой) и передача управления подпрограмме обработки прерывания. Действия,

выполняемые при этом процессором, как правило, те же, что и при обращении к

подпрограмме. Только при обращении к подпрограмме они инициируются командой, а

при обработке прерывания - управляющим сигналом от ВУ, который называют

"Запрос на прерывание" или "Требование прерывания".

Эта важная особенность обмена с прерыванием программы

позволяет организовать обмен данными с ВУ в произвольные моменты времени, не

зависящие от программы, выполняемой в микроЭВМ. Таким образом, появляется

возможность обмена данными с ВУ в реальном масштабе времени, определяемом

внешней по отношению к микроЭВМ средой. Обмен с прерыванием программы

существенным образом экономит время процессора, затрачиваемое на обмен. Это

происходит за счет того, что исчезает необходимость в организации программных

циклов ожидания готовности ВУ, на выполнение которых тратится значительное

время, особенно при обмене с медленными ВУ.

Прерывание программы по требованию ВУ не должно оказывать на

прерванную программу никакого влияния кроме увеличения времени ее выполнения за

счет приостановки на время выполнения подпрограммы обработки прерывания.

Поскольку для выполнения подпрограммы обработки прерывания используются

различные регистры процессора (счетчик команд, регистр состояния и т.д.), то

информацию, содержащуюся в них в момент прерывания, необходимо сохранить для

последующего возврата в прерванную программу.

Обычно задача сохранения содержимого счетчика команд и

регистра состояния процессора возлагается на аппаратные средства обработки

прерывания. Сохранение содержимого других регистров процессора, используемых в

подпрограмме обработки прерывания, производится непосредственно в подпрограмме.

Отсюда следует достаточно очевидный факт: чем больший объем информации о

прерванной программе сохраняется программным путем, тем больше время реакции

микроЭВМ на сигнал прерывания, и наоборот. Предпочтительными с точки зрения

повышения производительности микроЭВМ (сокращения времени выполнения

подпрограмм обработки, а, следовательно, и основной программы) являются

уменьшение числа команд, обеспечивающих сохранение информации о прерванной

программе, и реализация этих функций аппаратными средствами.

Формирование сигналов прерываний - запросов ВУ на

обслуживание происходит в контроллерах соответствующих ВУ. В простейших случаях

в качестве сигнала прерывания может использоваться сигнал "Готовность

ВУ", поступающий из контроллера ВУ в системный интерфейс микроЭВМ. Однако

такое простое решение обладает существенным недостатком - процессор не имеет

возможности управлять прерываниями, т. е. разрешать или запрещать их для

отдельных ВУ. В результате организация обмена данными в режиме прерывания с

несколькими ВУ существенно усложняется.

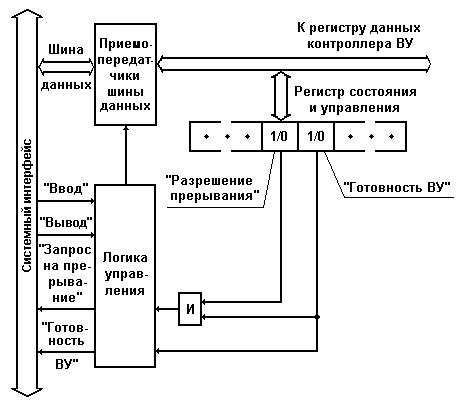

Рис.

4. Фрагмент блок-схемы контроллера ВУ с разрядом.

Для решения этой проблемы регистр состояния и управления

контроллера ВУ (рис. 4) дополняют еще одним разрядом - "Разрешение

прерывания". Запись 1 или 0 в разряд "Разрешение прерывания" производится

программным путем по одной из линий шины данных системного интерфейса.

Управляющий сигнал системного интерфейса "Запрос на прерывание"

формируется с помощью схемы совпадения только при наличии единиц в разрядах

"Готовность ВУ" и "Разрешение прерывания" регистра

состояния и управления контроллера.

Аналогичным путем решается проблемам управления прерываниями

в микроЭВМ, в целом. Для этого в регистре состояния процессора выделяется

разряд, содержимое которого определяет, разрешены или запрещены прерывания от

внешних устройств. Значение этого разряда может устанавливаться программным

путем.

В микроЭВМ обычно используется одноуровневая система

прерываний, т. е. сигналы "Запрос на прерывание" от всех ВУ поступают

на один вход процессора. Поэтому возникает проблема идентификации ВУ,

запросившего обслуживание, и реализации заданной очередности (приоритета)

обслуживания ВУ при одновременном поступлении нескольких сигналов прерывания.

Существуют два основных способа идентификации ВУ, запросивших обслуживания:

·

программный опрос регистров состояния (разряд

"Готовность ВУ") контроллеров всех ВУ;

·

использование векторов прерывания.

Организация прерываний с программным опросом готовности

предполагает наличие в памяти микроЭВМ единой подпрограммы обслуживания прерываний

от всех внешних устройств. Структура такой подпрограммы приведена на рис. 5.

Рис.

5 Структура единой программы

прерываний и ее связь с основной программой.

Обслуживание ВУ с помощью единой подпрограммы обработки

прерываний производится следующим образом. В конце последнего машинного цикла

выполнения очередной команды основной программы процессор проверяет наличие

требования прерывания от ВУ. Если сигнал прерывания есть и в процессоре

прерывание разрешено, то процессор переключается на выполнение подпрограммы

обработки прерываний.

После сохранения содержимого регистров процессора,

используемых в подпрограмме, начинается последовательный опрос регистров

состояния контроллеров всех ВУ, работающих в режиме прерывания. Как только

подпрограмма обнаружит готовое к обмену ВУ, сразу выполняются действия по его

обслуживанию. Завершается подпрограмма обработки прерывания после опроса

готовности всех ВУ и восстановления содержимого регистров процессора.

Приоритет ВУ в микроЭВМ с программным опросом готовности

внешнего устройства однозначно определяется порядком их опроса в подпрограмме

обработки прерываний. Чем раньше в подпрограмме опрашивается готовность ВУ, тем

меньше время реакции на его запрос и выше приоритет. Необходимость проверки

готовности всех внешних устройств существенно увеличивает время обслуживания

тех ВУ, которые опрашиваются последними. Это является основным недостатком

рассматриваемого способа организации прерываний. Поэтому обслуживание

прерываний с опросом готовности ВУ используется только в тех случаях, когда

отсутствуют жесткие требования на время обработки сигналов прерывания внешних

устройств.

Организация системы прерываний в микроЭВМ с использованием

векторов прерываний позволяет устранить указанный недостаток. При такой

организации системы прерываний ВУ, запросившее обслуживания, само

идентифицирует себя с помощью вектора прерывания - адреса ячейки основной

памяти микроЭВМ, в которой хранится либо первая команда подпрограммы

обслуживания прерывания данного ВУ, либо адрес начала такой подпрограммы. Таким

образом, процессор, получив вектор прерывания, сразу переключается на

выполнение требуемой подпрограммы обработки прерывания. В микроЭВМ с векторной

системой прерывания каждое ВУ должно иметь собственную подпрограмму обработки

прерывания.

Различают векторные системы с интерфейсным и внеинтерфейсным

вектором. В первом случае вектор прерывания формирует контроллер ВУ,

запросившего обслуживания, во втором - контроллер прерываний, общий для всех

устройств, работающих в режиме прерываний (IBM-совместимые персональные

компьютеры).

Рассмотрим организацию векторной системы с интерфейсным

вектором. Вектор прерывания выдается контроллером не одновременно с запросом на

прерывание, а только по разрешению процессора, как это реализовано в схеме на

рис. 6. Это делается для того, чтобы исключить одновременную выдачу векторов

прерывания от нескольких ВУ. В ответ на сигнал контроллера ВУ "Запрос на

прерывание" процессор формирует управляющий сигнал "Предоставление

прерывания (вх.)", который разрешает контроллеру ВУ, запросившему

обслуживание, выдачу вектора прерывания в шину адреса системного интерфейса.

Для этого в контроллере используются регистр вектора прерывания и схема

совпадения И3. Регистр вектора прерывания обычно реализуется с помощью

перемычек или переключателей, что позволяет пользователю устанавливать для

конкретных ВУ требуемые значения векторов прерывания.

Рис. 6

Формирование векторов прерывания в контроллере ВУ.

Управляющий сигнал "Предоставление прерывания

(вых.)" формируется в контроллере ВУ с помощью схемы совпадения И2. Этот

сигнал используется для организации последовательного аппаратного опроса

готовности ВУ и реализации тем самым требуемых приоритетов ВУ. Процессор при

поступлении в него по общей линии системного интерфейса "Запрос на

прерывание" сигнала прерывания формирует управляющий сигнал

"Предоставление прерывания (вх.)", который поступает сначала в

контроллер ВУ с наивысшим приоритетом (рис. 3.14). Если это устройство не

требовало обслуживания, то его контроллер пропускает сигнал

"Предоставление прерывания" на следующий контроллер, иначе дальнейшее

распространение сигнала прекращается и контроллер выдает вектор прерывания на

адресно-информационную шину.

Рис.

7. Реализация приоритетов ВУ в микроЭВМ с векторной системой прерываний, с

интерфейсным вектором (ППР (вх.) - "Предоставление прерывания

(входной)"; "ППР (вых.) - Предоставление прерывания

(выходной)").

Аппаратный опрос готовности ВУ производится гораздо быстрее,

нежели программный. Но если обслуживания запросили одновременно два или более

ВУ, обслуживание менее приоритетных ВУ будет отложено на время обслуживания

более приоритетных, как и в системе прерывания с программным опросом.

Рассмотренная векторная система прерываний практически

полностью соответствует системе прерываний, реализованной в микроЭВМ

"Электроника-60". Восьмиразрядный вектор прерывания в

"Электронике-60" указывает одну из ячеек памяти с адресами от 0 до

(376)8, в которой размещается адрес начала подпрограммы обработки прерывания. В

следующей за указанной вектором прерывания ячейке памяти хранится новое

содержимое регистра состояния процессора, загружаемое в него при переключении

на подпрограмму обработки прерывания. Один из бит нового содержимого регистра

состояния процессора запрещает или разрешает прерывания от других ВУ, что

позволяет ВУ с более высоким приоритетом прерывать подпрограммы обслуживания ВУ

с меньшим приоритетом и наоборот.

Векторная система с внеинтерфейсным вектором прерывания

используется в IBM-совместимых персональных компьютерах. В этих компьютерах

контроллеры внешних устройств не имеют регистров для хранения векторов

прерывания, а для идентификации устройств, запросивших обслуживания,

используется общий для всех ВУ контроллер прерываний . Ниже приведен пример

контроллера прерываний INTEL 8559A.

БИС программируемого контроллера прерываний (ПКП)

представляет собой устройство, реализующее до восьми уровней запросов на

прерывания с возможностью программного маскирования и изменения порядка

обслуживания прерываний. За счет каскадного включения БИС ПКП число уровней

прерывания может быть расширено до 64 (в архитектуре персонального компьютера

IBM PC AT - 16).

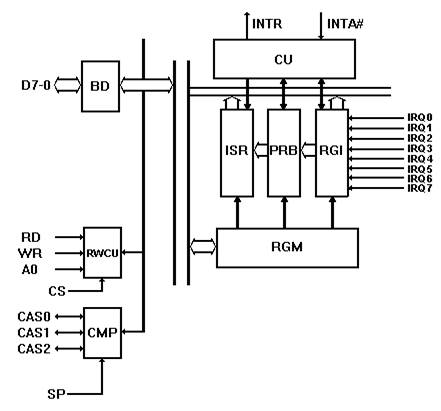

Структурная схема ПКП приведена на рисунке 8.

Рис. 8.

Контроллер прерываний Intel 8259A.

В состав БИС входят:

·

RGI - регистр запретов прерываний; хранит все

уровни, на которые поступают запросы IRQx;

·

PRB - схема принятия решений по приоритетам;

схема идентифицирует приоритет запросов и выбирает запрос с наивысшим

приоритетом;

·

ISR - регистр обслуживаемых прерываний;

сохраняет уровни запросов прерываний, находящиеся на обслуживании ПКП;

·

RGM - регистр маскирования прерываний; обеспечивает

запрещение одной или нескольких линий запросов прерывания;

·

BD - буфер данных; предназначен для сопряжения

ПКП с системной шиной данных;

·

RWCU - блок управления записью/чтением;

принимает управляющие сигналы от микропроцессора и задает режим функционирования

ПКП;

·

CMP - схема каскадного буфера-компаратора;

используется для включения в систему нескольких ПКП;

·

CU - схема управления; вырабатывает сигналы

прерывания и формирует трехбайтовую команду CALL для выдачи на шину данных.

Установка ПКП в исходное состояние и "настройка"

его на определенный режим обслуживания прерываний происходит с помощью двух

типов команд: команд инициализации (ICW) и команд управления операциями (OCW).

Программируемый контроллер прерываний (ПКП) имеет 16 входов

запросов прерываний (IRQ 0 - IRQ 15). Контроллер состоит из двух каскадно-включенных

контроллеров - выход INTR (запрос на прерывание) второго контроллера подключен

ко входу IRQ 2 первого контроллера. В качестве примера отметим, что к линии IRQ

0 подключен системный таймер, к линии IRQ 1 - клавиатура, к линии IRQ 8 - часы

реального времени и т.д.

Упрощенная схема взаимодействия контроллера прерываний с

процессором и контроллером шины имеет следующий вид.

Рис. 9 Упрощенная

схема взаимодействия контроллера прерываний с процессором и контроллером шины в

IBM-совместимых персональных компьютерах класса AT.

Эта схема функционирует следующим образом. Пусть в некоторый

момент времени контроллер клавиатуры с помощью единичного сигнала по линии IRQ

1 известил контроллер прерываний о своей готовности к обмену. В ответ на запрос

контроллер прерываний генерирует сигнал INTR (запрос на прерывание) и посылает

его на соответствующий вход процессора. Процессор, если маскируемые прерывания

разрешены (т.е. установлен флаг прерываний IF в регистре флагов процессора),

посылает на контроллер шины сигналы R# - чтение, C# - управление и IO# -

ввод/вывод, определяющие тип цикла шины. Контроллер шины, в свою очередь,

генерирует два сигнала подтверждения прерывания INTA# и направляет их на

контроллер прерываний. По второму импульсу контроллер прерываний выставляет на

шину данных восьмибитный номер вектора прерывания, соответствующий данной линии

IRQ.

В режиме реального адреса ("реальном" режиме)

векторы прерываний хранятся в таблице векторов прерываний, которая находится в

первом килобайте оперативной памяти. Под каждый вектор отведено 4 байта (2

байта под адрес сегмента и 2 байта под смещение), т.е. в таблице может

содержаться 256 векторов. Адрес вектора в таблице - номер вектора - 4.

Далее процессор считывает номер вектора прерывания.

Сохраняет в стеке содержимое регистра флагов, сбрасывает флаг прерываний IF и

помещает в стек адрес возврата в прерванную программу (регистры CS и IP). После

этого процессор извлекает из таблицы векторов прерываний адрес подпрограммы

обработки прерываний для данного устройства и приступает к ее выполнению.

Процедура обработки аппаратного прерывания должна

завершаться командой конца прерывания EOI (End of Interruption), посылаемой

контроллеру прерываний. Для этого необходимо записать байт 20h в порт 20h (для

первого контроллера) и в порт A0h (для второго).

В IBM PC/XT/AT используется режим прерываний с

фиксированными приоритетами. Высшим приоритетом обладает запрос по линии IRQ 0,

низшим - IRQ 7. Так как второй контроллер подключен к линии IRQ 2 первого

контроллера, то приоритеты линий IRQ в порядке убывания приоритета

располагаются следующим образом: IRQ 0, IRQ 1, IRQ 8 - IRQ 15, IRQ 3 - IRQ 7.

Если запрос на обслуживание посылают одновременно два

устройства с разными приоритетами, то контроллер обслуживает запрос с большим

приоритетом, а запрос с меньшим приоритетом блокирует.

Блокировка сохраняется до получения команды EOI.

Заключение

В данной работе были рассмотрены такие основные компоненты

электронно-вычислительных машин (ЭВМ) и их функции, как: оперативная память, стековая память, микропроцессоры, а также

организация прерываний в ЭВМ.

По оперативной памяти

было рассмотрено её устройство, правила доступа, организация, связь с системной

магистралью, способы хранения информации, время доступа, емкость,

производительность, пропускная способность.

Была описана стековая

память, а также кэш-память

первого и второго уровня. Также правила доступа к стековой памяти.

Относительно микропроцессоров, были рассмотрены такие их

характеристики, как тактовая частота,

разрядность, архитектура, система команд, режимы работы, структурная схема

и цикл работы при выполнении команды.

Подробно рассмотрена организация прерываний в ЭВМ. Здесь

рассматривался процесс переключения между командами при помощи прерываний,

выполнение прерываний, по требованию внешних устройств, сохранение состояния

регистров процессора при прерывании команды, для возможности возврата к ней для

продолжения выполнения.

Рассматривался процесс разрешения прерывания. Если в данный

момент прерывание выполняемой команды процессором допустимо, то выставляется

соответствующий флаг допустимости прерывания. Если данный флаг сброшен, то в

настоящий момент переход на выполнение другой команды недопустим.

Для обработки прерываний рассматривались два основных

способа: программный опрос регистров

состояния контроллеров всех внешних устройств и использование векторов прерывания.

Описывалась установка приоритета работы с внешними

устройствами при обращении к ним процессора.