6 Описание

структурной схемы микропроцессорного блока.

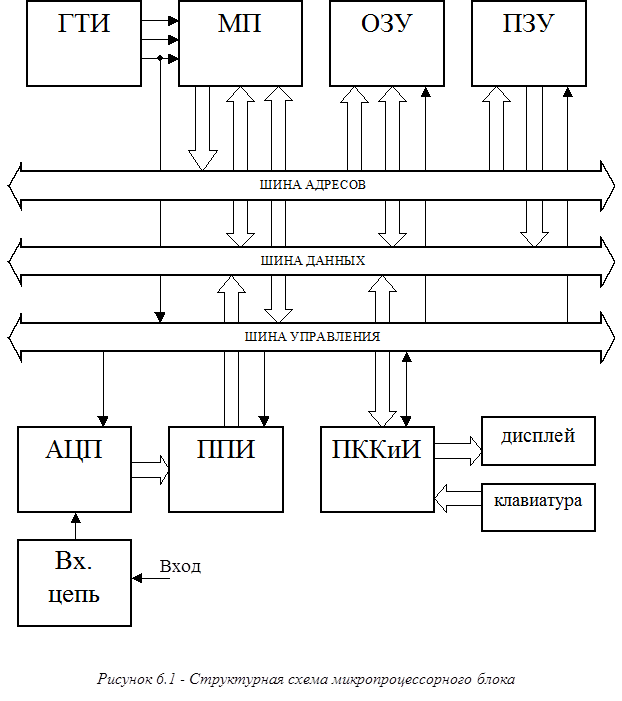

Структурная схема микропроцессорного

блока приведена на рисунке 6.1. Основными элементами микропроцессорного блока

являются:

·

микропроцессор

КР580ВМ80;

·

тактовый

генератор;

·

шинный

формирователь КР580ВК28;

·

оперативно

запоминающее устройство (ОЗУ);

·

постоянно

запоминающее устройство (ПЗУ);

·

входная цепь на

базе ОУ К140УД6;

·

аналого-цифровой

преобразователь (АЦП);

·

программируемый

параллельный адаптер;

·

программируемый

контроллер клавиатуры и индикации (ПККиИ);

·

клавиатура;

·

индикатор;

·

шина адресов;

·

шина данных;

·

шина управления.

Разработка ЭВМ на базе

микропроцессорного комплекта КР580 требует решения следующих основных задач:

определения состава интерфейсных устройств ввода-вывода; определение состава

памяти; разработка системы прерываний и

прямого доступа к памяти; разработка системы адресации и внутреннего интерфейса

микроЭВМ; обеспечение допустимой нагрузочной способности компонентов и

микроЭВМ.

При создании микроЭВМ на базе

микропроцессорного комплекта КР580ВМ80 могут использоваться различные

оперативные, постоянные и полупостоянные устройства памяти. Эти ЗУ могут

отличаться емкостью, способом организации, временными характеристиками, числом

входов выборки кристалла, составом управляющих входов и некоторыми другими

параметрами. Одни из них непосредственно сопрягаются с шиной данных микроЭВМ,

другие требуют дополнительных буферных элементов. Поэтому задача выбора БИС ЗУ

для микроЭВМ требует учета всех перечисленных факторов.

Разработка

системы адресации и внутреннего интерфейса микроЭВМ сводится главным

образом к решению задачи выбора способа обращения к устройства памяти и

ввода-вывода и к присвоению адресов. Возможны два способа обращения: с

использованием признаков текущего машинного цикла и с разделением адресов между

запоминающими устройствами и устройствами ввода-вывода. В первом случае ячейка

памяти ячейка памяти и устройство ввода-вывода могут иметь одинаковые адреса, а

выбор устройства памяти или устройства ввода-вывода осуществляется с помощью

определённых разрядов слова признака машинного цикла. Это слово должно быть

выделено с шины данных в начале каждого машинного цикла и записано в

специальный регистр. Во втором случае одна из адресных линий выделяется для

указания типа адресации (обращение к памяти или ввод-вывод). Этот способ

уменьшает объем адресуемой памяти в два раза, однако позволяет исключить

регистр слова признаков текущего цикла. Если рассматривать внутренний

интерфейс, микроЭВМ, как совокупность шин данных, адресной и управления, то

использование слова признаков увеличивает число управляющих сигналов, это

упрощает системную организацию микроЭВМ. Второй способ обращения можно

представить, как перевод одной (или более) адресной линии из адресной шины в

шину управления.

Разработка

системы адресации и внутреннего интерфейса микроЭВМ сводится главным

образом к решению задачи выбора способа обращения к устройства памяти и

ввода-вывода и к присвоению адресов. Возможны два способа обращения: с

использованием признаков текущего машинного цикла и с разделением адресов между

запоминающими устройствами и устройствами ввода-вывода. В первом случае ячейка

памяти ячейка памяти и устройство ввода-вывода могут иметь одинаковые адреса, а

выбор устройства памяти или устройства ввода-вывода осуществляется с помощью

определённых разрядов слова признака машинного цикла. Это слово должно быть

выделено с шины данных в начале каждого машинного цикла и записано в

специальный регистр. Во втором случае одна из адресных линий выделяется для

указания типа адресации (обращение к памяти или ввод-вывод). Этот способ

уменьшает объем адресуемой памяти в два раза, однако позволяет исключить

регистр слова признаков текущего цикла. Если рассматривать внутренний

интерфейс, микроЭВМ, как совокупность шин данных, адресной и управления, то

использование слова признаков увеличивает число управляющих сигналов, это

упрощает системную организацию микроЭВМ. Второй способ обращения можно

представить, как перевод одной (или более) адресной линии из адресной шины в

шину управления.

Вопрос присвоения адресов должен

решаться с учетом разрядности адресных шин устройств и числа входов выборки

кристаллов., в том числе прямых и

инверсных. Лишь в простейших случаях решение этой задачи не связано с

введением дополнительных логических элементов. Электрическое сопряжение

компонентов микроЭВМ должно производиться исходя из их нагрузочной способности.

Основную нагрузку обычно несет шина данных МП.

6.1 Генератор тактовых импульсов

Генератор тактовых импульсов выполнен

на микросхеме КР580ГФ24 и предназначен для синхронизации микропроцессорной системы.

Генератор тактовых импульсов (ГТИ) формирует тактовые импульсы с частотой до

2,5 МГц и амплитудой 12 В, а так же некоторые управляющие сигналы для

микропроцессорной системы.

Структурная схема ГТИ представлена на

рисунке 6.2, а подключение ГТИ к МП показано на рисунке 6.3. ГТИ состоит из

задающего генератора, (SGN), генератора тактовых импульсов (GLG), порогового

элемента, формирователей и логических схем. Для работы ГТИ необходимо подключение

внешнего кварцевого резонатора с частотой в 9 раз большей, чем частота выходных

тактовых импульсов ГТИ.

Основные временные характеристики

тактовых импульсов следующие:

Время переднего и заднего фронтов (tLH, tHL), нс 0÷50

Ширина импульса CLK1 (tCLK1), нс ≥60

Ширина импульса CLK2 (tCLK2), нс ≥220

Временной интервал между задним

фронтом

CLK1 и передним фронтом CLK2 (tD1), нс ≥0

Временной интервал между задним

фронтом CLK2

и

передним фронтом CLK1 (tD2), нс ≥70

Задержка CLK2 по отношению к CLK1,

tD3,нс ≥80

Основные электрические параметры

микросхемы КР580ГФ24 следующие:

Входное напряжение L-уровня UIL, В 0,8

Входное напряжение H-уровня UIH, В 0,2

Напряжение RESIN, UIH-UIL, В 0,25

Выходное напряжение L-уровня UOL, В 0,45

Выходное напряжение H-уровня UOH, В:

на

выходах CLK1, CLK2 9,4

на

выходах READY, RESET 3,6

на

всех других выходах 2,4

Ток источника питания ICC, мА 115

Ток источника питания IDD, мА 12

Назначение входных и выходных сигналов:

XTAL1, XTAL2 – входы для подключения

кварцевого резонатора.

TANK – вход для подключения

параллельного LC-контура.

SYNC – вход синхронизации.

RESIN – входной сигнал «СБРОС».

RDYIN – вход сигнала «ГОТОВ», для

подачи сигналов о готовности внешних устройств к работе с МП.

OSC – выход генератора,

используемый для тактирования периферийных устройств.

CLK1, CLK2 – выходы тактовых

импульсов.

STSTB – строб состояния – сигнал

L-уровня, используемый для фиксации слова состояния МП.

RESET – выходной сигнал «СБРОС».

READY– выходной сигнал «ГОТОВ».

Питание генератора тактовых импульсов

осуществляется источником напряжения +5В.

6.2 Системный контроллер и шинный формирователь КР580ВК28.

Системный контроллер и шинный

формирователь КР580ВК28 предназначен для фиксации слова состояния МП, выработки

системных управляющих сигналов, буферизации шины данных МП и управления направлением

передачи данных.

Структурная схема системного

контроллера и шинного формирователя (СКФ) приведена на рисунке 6.4. В состав

СКФ входят: шинный формирователь-усилитель (BF), обеспечивающий увеличение

нагрузочной способности системной информационной шины; регистр (RG) для записи

и хранения слова состояния МП; комбинационная схема (PLA) для формирования

выходных управляющих сигналов.

Назначение входных, выходных и

управляющих сигналов:

D0…D7 – входы – выходы данных со

стороны МП.

STSTB – строб состояния от ГТИ.

DBIN – вход сигнала «ПРИЁМ» от МП.

WR – вход сигнала «ВЫДАЧА» от МП.

HLDA – вход сигнала «ПОДТВЕРЖДЕНИЕ

ЗАХВАТА» от МП.

DB0…DB7 – входы-выходы системной

шины данных.

MEMR – чтение памяти.

MEMW – запись в память.

I/OR – чтение с ВУ.

I/OW – запись в ВУ.

BUSEN – разрешение работы шин – сигнал H-уровня, устанавливающий

все выходы в высокоимпендансное состояние

INTA – подтверждение прерывания –

сигнал L-уровня, используемый для стробирования ввода адреса подпрограммы

обслуживания прерывания.

Основные электрические параметры

микросхемы КР580ВК28.

Выходное напряжение L-уровня UOL, В:

На

шине D0…D7 ≤0,45

На

всех других выходах ≤0,45

Выходное напряжение H-уровня UOH, В:

На

шине D0…D7 ≥3,6

На

всех других выходах ≥2,4

Ток потребления от источника питания ICC, мА ≤190

Прямой входной ток IB, мкА:

На

входе STSTB ≤500

На

других входах ≤250

Обратный входной ток II, мкА:

На

входе STSTB ≤100

На

других входах ≤100

По сигналу STSTB, который

вырабатывается ГТИ, происходит запись слова-состояния в регистр хранения, а

затем выдача его на комбинационную схему, формирующую управляющие сигналы.

6.3 Программируемый параллельный интерфейс (ППИ)

БИС программируемого параллельного

интерфейса КР580ВВ55 предназначена для организации ввода/вывода параллельной

информации различного формата и позволяет реализовать большинство известных протоколов

по параллельным каналам. БИС программируемого параллельного интерфейса (ППИ)

может использоваться для сопряжения микропроцессора со стандартным интерфейсным

оборудованием (дисплеем, телетайпом, накопителем). В нашем случае ППИ

используется для сопряжения аналого-цифрового преобразователя с

микропроцессорной системой. Структурная схема ППИ приведена на рисунке 6.6. В

состав БИС входят: Двунаправленный 8-разрядный буфер данных (BD), связывающий

ППИ с системной шиной данных; блок управления записью/чтением (RWCU),

обеспечивающий управление внешними и внутренними передачами данных, управляющих

слов и информации о состоянии ППИ; три 8-разрядных канала ввода/вывода (PORT A,

B и C) для обмена информацией с внешними устройствами; схема управления группой

A (CUA), вырабатывающая сигналы управления каналом A и старшими разрядами

канала C [PC(7-4)]; схема управления группой B (CUB), вырабатывающая сигналы

управления каналом B и младшими разрядами канала C [PC(3-0)].

Назначение входных, выходных и

управляющих сигналов ППИ:

D(7-0) – ввод/вывод данных;

RD – чтение; L-уровень сигнала

разрешает считывание информации из регистра, адресуемого по входам A0, A1 на

шину D(7-0).

WR – запись; L-уровень сигнала

разрешает запись информации с шины D(7-0) в регистр ППИ, адресуемый по входам

A0, A1.

A0, A1 – входы для адресации

внутренних регистров ППИ.

RESET – сброс; H – уровень сигнала

обнуляет регистр управляющего слова и устанавливает все порты в режим ввода.

CS – выбор микросхемы; L-уровень

сигнала подключает ППИ к системной шине.

PA(7-0) – ввод/вывод канала А.

PB(7-0) – ввод/вывод канала B.

PC(7-0) – ввод/вывод канала C.

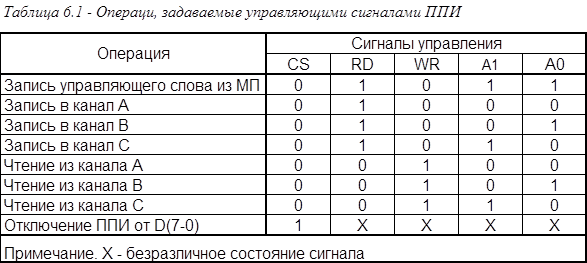

Сигналы управления работой ППИ подаются на блок

RWCU и вместе с адресными входами A0, A1 задают вид операции, выполняемой БИС

как указано в таблице 6.1.

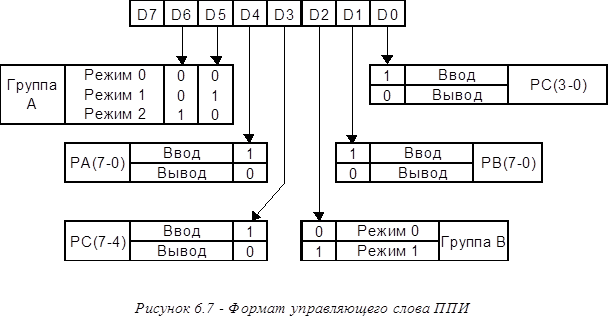

Режим работы каждого из каналов ППИ

программируется с помощью управляющего слова. Управляющее слово может задать

один из трех режимов: основной режим ввода/вывода (режим 0), стробируемый

ввод/вывод (режим 1), режим двунаправленной передачи информации (режим 2).

Одним управляющим словом можно установить различные режимы работы для каждого

из каналов. Формат управляющего слова представлен на рисунке 6.7.

Канал A может работать в одном из трех режимов, канал B – в

режимах 0 и 1. Канал C может быть использован для передачи данных только в

режиме 0, а в остальных режимах он служит для передачи управляющих сигналов,

сопровождающих процесс обмена по каналам A и B.

Канал A может работать в одном из трех режимов, канал B – в

режимах 0 и 1. Канал C может быть использован для передачи данных только в

режиме 0, а в остальных режимах он служит для передачи управляющих сигналов,

сопровождающих процесс обмена по каналам A и B.

Разряд D7 управляющего слова

определяет либо установку режимов работы каналов (D7=1), либо работу ППИ в

режиме сброса/установки отдельных разрядов канала C (D7=0). При поразрядном

управлении каналом C разряды D3-D1 определяют номер модифицируемого разряда;

разряд D0 задает сброс (D0=0) или установку (D0=1) модифицируемого разряда;

разряды D6-D4 не используются.

Сброс/установку разрядов канала С

можно использовать для выработки сигналов запроса прерывания от ППИ. Для

каждого из каналов A и B в ППИ имеется триггер разрешения прерывания,

установка/сброс которого осуществляется управляющим словом установки/сброса

отдельного разряда канала C. Если триггер разрешения прерывания

соответствующего канала установлен (INTE=1), то ППИ может сформировать сигнал

запроса прерывания при готовности внешнего устройства к вводу или выводу.

Режим 0 применяется при синхронном

обмене или при программной организации асинхронного обмена. Микросхема может

рассматриваться в этом режиме, как устройство, состоящее из четырех портов (два

8-разрядных и два 4-разрядных), независимо настраиваемых на ввод или вывод.

Вывод информации осуществляется по команде OUT микропроцессора с фиксацией

выводимой информации в регистрах каналов, а ввод – по команде IN без

запоминания информации.

Режим 1 обеспечивает стробируемый

однонаправленный обмен информацией с внешним устройством. Передача данных

производится по каналам A и B, а линии канала C управляют передачей. Работу

канала в режиме 1 сопровождают три управляющих сигнала. Если один из каналов запрограммировать

на режим 1, то остальные 13 интерфейсных линий можно использовать в режиме 0.

Если оба канала запрограммированы на режим 1, то оставшиеся две интерфейсные

линии канала C могут быть настроены на ввод или вывод.

В режиме 1 для ввода информации

используются следующие управляющие сигналы:

·

строб приема (STB)

– входной сигнал, формируемый внешним устройством; указывает на готовность ВУ к

вводу информации;

·

подтверждение

приема (IBF) – выходной сигнал ППИ, сообщающий ВУ об окончании приема данных в

канал; формируется по спаду STB;

·

запрос прерывания

(INTR) – выходной сигнал ППИ, информирующий МП о завершении приема информации в

канале; H-уровень сигнала устанавливается при STB=1, IBF=1 и INTE=1;

сбрасывается спадом сигнала RD.

Для операции ввода управления

сигналом INTE канала A осуществляется по линии PC4, а канала B – по линии PC2.

Для вывода информации в режиме 1 используется

следующие управляющие сигналы:

·

строб записи (OBF)

– выходной сигнал, указывающий внешнему устройству о готовности к выводу;

формируется по фронту сигнала WR;

·

подтверждение

записи (ACK) – входной сигнал от внешнего устройства, подтверждающий прием информации

из ППИ;

·

запрос прерывания

(INTR) – выходной сигнал ППИ, информирующий МП о завершении операции вывода

информации; H-уровень сигнала устанавливается по фронту сигнала ACK при OBF=1 и

INTR=1; сбрасывается спадом сигнала WR;

Для операции вывода управление

сигналом INTE канала A осуществляется по линии PC6, а канала B – по линии PC2.

Режим 2

обеспечивает двунаправленную передачу информации по каналу A к внешнему

устройству и обратно. Процесс обмена сопровождают пять управляющих сигналов,

подаваемых по линиям PC7-PC3. Оставшиеся 11 интерфейсных линий могут

настраиваться на режим 0 или режим 1.

В условиях

данной разработки применять режим 1 для обмена информацией между АЦП и ППИ

нецелесообразно, так как он усложняет схему и процесс обмена данными и занимает

свободные (резервные) интерфейсные линии порта C, не улучшая динамических и

метрологических характеристик устройства. Режим 2 также применять

нецелесообразно, так как он применяется для двунаправленного обмена данными.

Из вышесказанного можно сделать вывод, что для передачи данных из

АЦП в ППИ наиболее оптимальным было бы использование режима 0, при подключении

АЦП к порту A. При этом остаются свободными порты B и C, которые могут в

дальнейшем использоваться при модификации микропроцессорного блока.

6.4 Программируемый контроллер клавиатуры и индикатора.

Для облегчения построения интерфейса

пользователя микропроцессорный комплект КР580 включает в себя БИС КР580ВВ79,

которая представляет собой программируемое интерфейсное устройство, предназначенное

для ввода данных с клавиатуры и вывода информации на дисплей. Микросхема

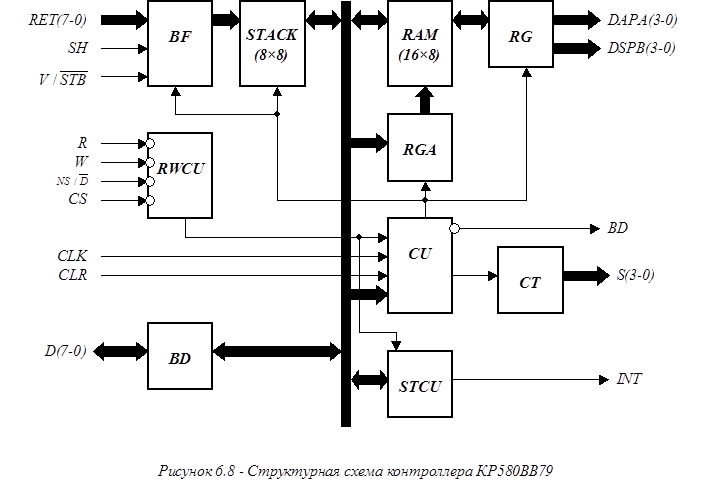

программируемого контроллера клавиатуры и индикации (ПККИ) состоит из двух

основных функционально разделимых частей: клавиатурной и дисплейной.

Клавиатурная часть предназначена для сопряжения с клавиатурой печатающих

устройств и с произвольными наборами переключателей. Дисплейная часть ПККИ

позволяет отображать информацию с помощью индикаторов различных типов

(дисплеев). Упрощенная структурная схема ПККИ приведена на рисунке 6.8.В состав

БИС входят:

·

буферы клавиатуры

и датчиков (BF), включающие также схему управления и устранения дребезга

клавиатуры, предназначенные для хранения входной информации в режимах

сканирования клавиатуры, наборов датчиков и ввода по стробу;

·

схема управления вводом/выводом (RWCU),

вырабатывающая сигналы управления обмена с МП и внутренними пересылками данных

и команд;

схема управления вводом/выводом (RWCU),

вырабатывающая сигналы управления обмена с МП и внутренними пересылками данных

и команд;

·

буферы канала

данных (BD), предназначенные для обмена информацией между ПККИ и МП;

·

ОЗУ клавиатуры

(STACK), работающие по принципу FIFO и предназначенная для хранения кодов

позиций клавиш и состояний ключей датчиков;

·

ОЗУ отображения

(RAM), сохраняющее информацию, отображаемую на дисплее;

·

регистр адреса ОЗУ

отображения (RGA), предназначенный для хранения адреса данных, записываемых или

считываемых микропроцессором;

·

схема управления и

синхронизации (CU), состоящая из регистров хранения команд и счетчика

синхронизации и осуществляющая управление работой всей микросхемы;

·

схема анализа

состояния ОЗУ-датчиков (STCU), контролирующая число символов в ОЗУ и формирующая

сигнал прерывания INT;

·

регистры ОЗУ

отображения (RG), предназначенные для хранения данных, отображаемых на выходах

каналов A и B;

·

счетчик

сканирования (CT), вырабатывающий сигналы сканирования клавиатуры, датчиков и

дисплея.

Назначение входных, выходных и

управляющих сигналов:

RET (7-0) –

входы линии возврата, служащие для подачи сигналов от датчиков через контакты

клавиш или ключа.

SH – вход

сигнала сдвига, используемого для сканирования клавиатуры.

- вход сигнала

управления для режима сканирования клавиатуры или стробирующего сигнала для

режима ввода по стробу.

- вход сигнала

управления для режима сканирования клавиатуры или стробирующего сигнала для

режима ввода по стробу.

R – вход сигнала чтения L-уровня, разрешающего передачу

информацию из ПККИ в канал данных МП.

W – вход

сигнала запись L-уровня, разрешающего передачу информации из канала данных МП в

ПККИ.

- вход для управления

записью/чтением данных или команд; при сигнале H-уровня происходит запись

команды или чтения состояния ПККИ, при сигнале L-уровня – запись или чтение

данных.

- вход для управления

записью/чтением данных или команд; при сигнале H-уровня происходит запись

команды или чтения состояния ПККИ, при сигнале L-уровня – запись или чтение

данных.

CS – вход

сигнала выбора микросхемы; L-уровень сигнала разрешает работу схемы.

CLK – вход

сигнала синхронизации микросхемы.

CLR – вход

сигнала установки ПККИ в исходное состояние.

D(7-0) –

входы/выходы канала данных.

DSPA(3-0) –

выходы канала A.

DSPB(3-0) –

выходы канала B.

BD – выход сигнала

гашения отображения L-уровня.

S(3-0) –

выходы сигналов сканирования клавиш клавиатуры или набора датчиков и дисплея.

INT – выход

сигнала прерывания.

На рисунке 6.9 показано включение

микросхемы в микропроцессорную систему, управляющую работой клавиатуры и

дисплея.

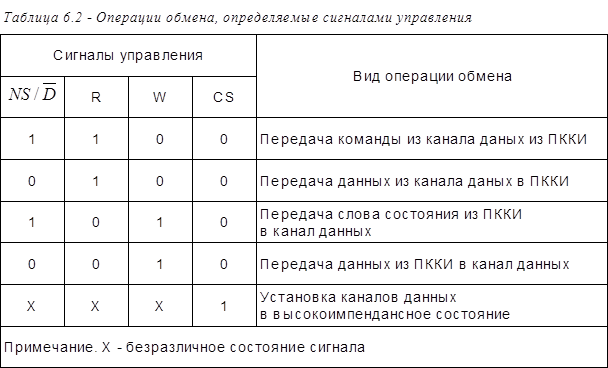

Направление и вид операции обмена между

микропроцессором и ПККИ представлены в таблице 6.2.

Клавиатурная часть ПККИ имеет три

режима работы: режим сканирования клавиатуры, режим определения состояния

набора датчиков и режим ввода по стробу.

В режиме сканирования клавиатуры байт

информации, вводимой в STACK,

содержит код позиции нажатой клавиши и два бита сигналов управления. Разряду D7

соответствует состояние сигнала  , а разряду D6 – сигнала SH. Разряды D3-D5 определяют номер

строки нажатой клавиши, разряды D0-D2 – номер столбца. После записи кода

позиции клавиши в STACK на выходе INT устанавливается напряжение H-уровня.

В этом режиме с помощью схемы управления и устранения дребезга клавиатуры

осуществляется также отработка ситуаций, возникающих при одновременном нажатии

клавиш.

, а разряду D6 – сигнала SH. Разряды D3-D5 определяют номер

строки нажатой клавиши, разряды D0-D2 – номер столбца. После записи кода

позиции клавиши в STACK на выходе INT устанавливается напряжение H-уровня.

В этом режиме с помощью схемы управления и устранения дребезга клавиатуры

осуществляется также отработка ситуаций, возникающих при одновременном нажатии

клавиш.

Режим сканирования клавиатуры может

выполняться с обнаружением двух нажатых клавиш. В этой разновидности режима

вводится код только одной нажатой клавиши. Одновременное нажатие двух клавиш не

воспринимается до тех пор, пока одна из них не будет отпущена. Другая

разновидность режима разрешает одновременное нажатие N клавиш (не более 8),

распознает их и вводит коды позиции в STACK

в соответствии с порядком обнаружения. В последнем варианте с помощью

специальной команды можно задать режим обнаружения ошибок, в котором наличие

двух нажатых клавиш рассматривается как одновременное нажатие и вызывает

установку в слове состояния ПККИ флага ошибки.

В режиме определения состояния набора

датчиков по входам RET(7-0) производится

построчный ввод в STACK состояния ключей датчиков. При этом STACK работает, как обычное ОЗУ, каждая ячейка которого загружается

состоянием соответствующей строки набора датчиков. В этом режиме не используются

входы  и SH и схема устранения дребезга клавиатуры. При обнаружении

изменения состояний датчиков на выходе INT

в конце интервала сканирования устанавливается, как правило, напряжение

H-уровня.

и SH и схема устранения дребезга клавиатуры. При обнаружении

изменения состояний датчиков на выходе INT

в конце интервала сканирования устанавливается, как правило, напряжение

H-уровня.

В режиме ввода по стробу ввод в STACK со входов RET(7-0) происходит при переходе стробирующего сигнала на входе  из состояния L-уровня

в состояние H-уровня. Вход SH и схема

устранения дребезга клавиатуры в этом режиме не используются, а длительность

стробирующего сигнала должна быть не меньше периода частоты синхронизации микросхемы.

из состояния L-уровня

в состояние H-уровня. Вход SH и схема

устранения дребезга клавиатуры в этом режиме не используются, а длительность

стробирующего сигнала должна быть не меньше периода частоты синхронизации микросхемы.

Дисплейная часть ПККИ имеет два

режима работы: режим ввода слева и режим ввода справа со сдвигом.

В режиме ввода слева каждой позиции

дисплея соответствует определенная строка в ОЗУ отображения (RAM). Нулевому

адресу в RAM соответствует крайний левый символ. Ввод символов, начиная с

нулевого адреса, вызывает построчное отображение информации слева направо. Ввод

справа со сдвигом используется в электронных калькуляторах. Здесь ввод первого

символа производится в крайнюю правую позицию дисплея. Следующий ввод также

производится в крайнюю правую позицию, а все отображение сдвигается на один

символ влево. В этом режиме нет прямого соответствия между позицией

отображаемого символа и адресом строки RAM, поэтому лучше использовать

последовательный ввод, начиная с нулевого адреса.

Информация на выходах DSPA(3-0) канала A соответствует разрядам

D7-D4 канала данных, а на выходах DSPB(3-0)

– разряда D3-D0.

Сигналы сканированные на выходах S(3-0) вырабатываются счетчиком

сканирования (CT), обеспечивающим два вида сигналов сканирования: кодированные

сигналы и дешифрированные. Кодированные сигналы сканирования являются выходами

четырех последних разрядов счетчика синхронизации и должны дешифрироваться

внешним дешифратором для получения сигналов сканирования клавиатуры и

индикаторов.

Режимы работы ПККИ устанавливаются

программно с помощью записи в него команд по каналу данных. Перед

программированием режима микросхема должна быть установлена в исходное состояние

подачей на вход CLR напряжения H – уровня длительностью не менее 6 тактовых импульсов.

Команды ПККИ занимают один байт и код операции определяется тремя старшими

разрядами D7-D5.

Для контроля состояния ПККИ

микропроцессор может считывать слово состояния БИС из внутреннего 8-разрядного

регистра слова состояния.

Разряды D3-D0 слова состояния

определяют число символов в ОЗУ клавиатуры и датчиков. Разряды D4 и D5

представляют флаги ошибок и используются в клавиатурном режиме и режиме ввода

по стробу. Разряд D4 устанавливается при чтении символа из пустого ОЗУ, а

разряд D6 – при записи в заполненное ОЗУ. Разряд D6 в режиме набора датчиков

устанавливается в том случае, если происходит замыкание хотя бы одного ключа

датчика. В режиме сканирования клавиатуры при записи команды «Сброс прерывания,

установка режима обнаружения ошибок» разряд D6 выполняет функцию флага ошибки.

Он устанавливается при обнаружении одновременного нажатия нескольких клавиш.

Разряд D7 слова состояния информирует о прекращении доступа к ОЗУ отображения.

6.5 Блок индикации и клавиатуры

Блок индикации и клавиатуры является

средством общения пользователя с микроЭВМ и разделяется соответственно на две

части: индикатор и клавиатуру.

Индикатор представляет собой набор

восьмиразрядных светодиодных индикаторов типа АЛС 334, которые содержат в себе

восемь светодиодов, соединенных, как показано на рисунке 6.10.

Блок клавиатуры включает в себя 16

клавиш типа ПКМ 1Б со следующими обозначениями: «1», «2», «3», «4», «5», «6»,

«7», «8», «9», «0», «ПУСК», «МЕНЮ», «ОК», «▼», «▲», «•».

Клавиши и индикаторы впаяны в плату

блока индикации и клавиатуры, которая соединена с микропроцессорным блоком

соединительным 26-проводным шлейфом.