2 Обоснование применения и выбор

микропроцессорного комплекта (МПК)

Выбор оптимального МПК для

конкретного применения является наименее решаемой из многочисленных проблем

развития микропроцессорной техники. Это определяется постоянным ростом

количества МПК, расширением области их применения, а так же отсутствием четкой

методики, позволяющей сделать однозначный выбор МПК.

Микропроцессор является функционально

сложным программно управляемым устройством, выполненным в виде БИС, и

характеризуется большим количеством параметров. Поэтому задача выбора

оптимального с технической и экономической точек зрения МПК БИС для конкретной

задачи является многокритериальной.

При выборе МПК БИС важным является

формирование основных требований, предъявляемых к проектируемой аппаратуре.

Аппаратура со встроенными микропроцессорами, как правило, должна удовлетворять

следующим требованиям:

·

работа в режиме

реального времени;

·

повышенная

надежность, помехозащищенность, простота обслуживания;

·

наличие

фиксированного набора задач, многократно решаемых на протяжении всего срока

службы аппаратуры.

Выбор МПК БИС обычно производится с

трех основных позиций:

1) с точки зрения разработки

математического обеспечения следует анализировать: разрядность, число и

использование регистров общего назначения, набор команд и способы адресации,

наличие и организацию стека;

2) с точки зрения системного

проектирования нужно анализировать следующие характеристики МПК БИС: тип

архитектуры МП (секционные или однокристальные) и, как следствие этого, тип

организации управления (микропрограммное или с жесткой логикой), наличие логически

совместимых БИС из других комплектов, быстродействие МП, возможность прерывания

и прямого доступа к память, наличие системы автоматизированного проектирования

МПС;

3) с точки зрения разработки

аппаратных средств МПС необходимо учитывать: электрическую совместимость БИС,

число источников питания и рассеиваемую мощность, размер, тип корпуса и число

выводов, диапазон рабочих температур и др.

Комплексный учет всех характеристик

МПК БИС весьма затруднителен, так, как одни характеристики относятся к МП как к

интегральной схеме, а другие – как к устройству ЭВМ или системы обработки

информации.

Одной из основных характеристик,

отражающих функциональные возможности МП, может служить его разрядность.

Диапазон требуемой разрядности в микропроцессорных системах довольно широк. Так

при построении контрольно-измерительных систем и систем сбора данных довольно

часто используются 8-разрядные МП, а при построении цифровых фильтров и

спектральных анализаторов требуемая разрядность МП возрастает до 32.

Таким образом, исходя из

сравнительных характеристик микропроцессорных комплектов приведенных в [11] и

учитывая необходимую разрядность микропроцессора, остановим свой выбор на

микропроцессорном комплекте КР580.

В микропроцессорном комплекте КР580

центральный процессор вместе с устройством управления реализован в виде

отдельной БИС и имеет фиксированную разрядность и встроенную систему команд.

Микропроцессорный комплект серии

КР580 включает в себя: микропроцессорную БИС КР580ВМ80; программируемое

устройство ввода-вывода параллельной информации различного формата КР580ВВ55;

программируемый блок приоритетного прерывания КР580ВН59; программируемое

устройство прямого доступа к памяти КР580ВТ57; интервальный таймер КР580ВИ53;

универсальный синхронно-асинхронный программируемый приемопередатчик КР580ВВ51;

программируемый контроллер электронно-лучевой трубки КР580ВГ75; программируемый

контроллер клавиатуры КР580ВВ79; системный контроллер КР580ВК28; тактовый генератор

КР580ВК28; тактовый генератор КР580ГФ24; шинные формирователи КР580ВА86, 87;

буферные регистры КР580ИР82, 83.

Схемы выполнены по n-МОП технологии,

входные и выходные сигналы соответствуют уровням работы ТТЛ-схем. Микро-ЭВМ,

построенная на базе комплекта, работает с тактовой частотой до 2 МГц. Схемы программируются

с помощью фиксированного набора команд микропроцессорных БИС КР580ВМ80.

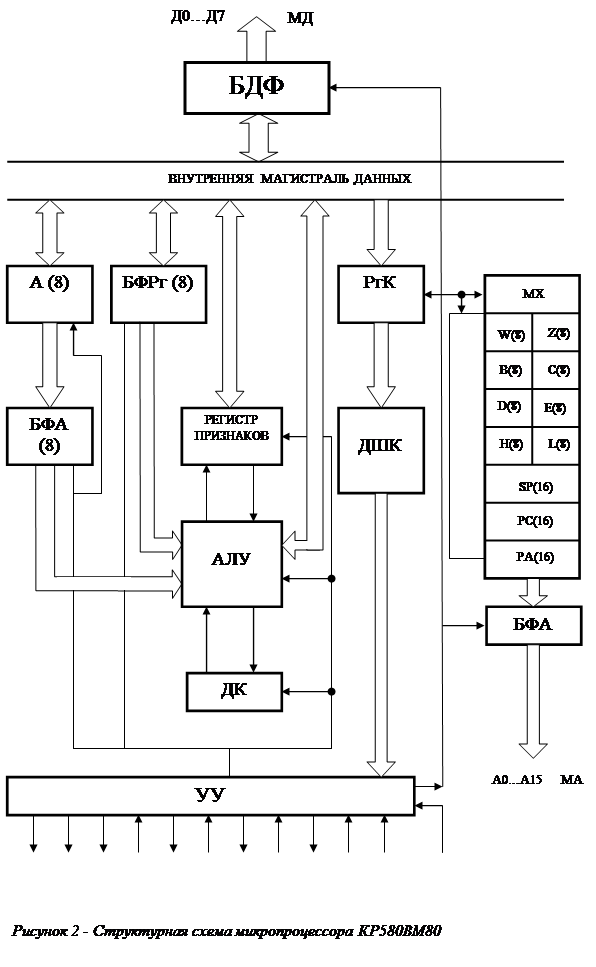

Микропроцессорная БИС КР580ВМ80

представляет собой однокристальный 8-разрядный микропроцессор с двумя

магистралями: однонаправленной 16-разрядной адресной магистралью (МА),

двунаправленной 8-разрядной магистралью данных (МД) и 12 сигналами управления

(шесть входных и шесть выходных). Структурная схема микропроцессора показана на

рисунке 2. Микропроцессорная БИС рассчитана на выполнение логических и

арифметических операций с 8-разрядными числами в двоичной и двоично-десятичной

системах счисления, а так же операций с двойной разрядностью (с 16-разрядными

числами).

Функциональное назначение внешних

выводов БИС КР580ВМ80 следующее:

А0…А15 – адресная магистраль (выходы

с тремя состояниями), обеспечивающая адресацию к любой из 216 восьмиразрядной

ячейки памяти или внешнего устройства (ВУ);

Д0…Д7 – двунаправленная магистраль

данных, используемая для обмена информацией с памятью или ВУ;

СИНХР – на этом выходе БИС

формируется сигнал СИНХРОНИЗАЦИЯ в начале каждого машинного цикла;

П – сигнал ПРИЕМ на этом выходе

указывает на готовность БИС к приему данных;

ОЖД – сигнал ОЖИДАНИЕ на этом выходе

указывает, что микропроцессор находится в процессе ожидания;

Зп – на этом выходе МП БИС сигнал ЗАПИСЬ указывает, что

данные выданы микропроцессорной БИС и установлены на МД, т.е. могут быть

записаны в ВУ;

ЗХ – вход, используемый для подачи

сигнала ЗАПРОС ЗАХВАТА на МП БИС. Обеспечивает переход микропроцессора в

состояние ЗАХВАТ, при котором МА и МД переходят в третье (высокоимпендансное)

состояние. Обычно это состояние используется для организации обмена информацией

по каналу прямого доступа к памяти, а также в многопроцессорных системах;

Р.Пр – на этом выходе сигнал РАЗРЕШЕНИЕ ПРЕРЫВАНИЯ

указывает на состояние внутреннего триггера разрешения прерывания МП БИС.

Состояние триггера может быть установлено программно. При уровне «0» на выходе Р.Пр прием запросов прерывания МП БИС невозможен;

Г – сигнал ГОТОВ на этом входе

информирует о готовности ВУ к обмену информацией с МП БИС. При уровне «0» МП

БИС будет находиться в состоянии ОЖИДАНИЕ;

П.ЗХ – На этом выходе МП БИС сигнал

ПОДТВЕРЖДЕНИЕ ЗАХВАТА появляется в ответ на сигнал ЗХ и указывает, что МД и МА

находятся в высокоимпендансном состоянии. Пока действует сигнал ЗХ процессор

приостанавливает выполнение своих операций после окончания текущего машинного

цикла;

З.Пр – вход, используемы для подачи сигнала ЗАПРОС ПРЕРЫВАНИЯ.

Сигнал поступает от внешнего устройства и требует прерывания выполнения

основной программы, перехода на выполнение подпрограмм обслуживания прерывания.

Сигнал запроса прерывания не воспринимается МП БИС при работе его в режимах

ЗАХВАТ, ОЖИДАНИЕ или нулевом состоянии внутреннего триггера разрешения

прерывания;

УСТ – вход, по которому поступает

сигнал на начальную установку МП, при этом обнуляются его программный счетчик,

внутренние триггеры, формирующие сигналы Р.Пр и П.ЗХ;

Ф1 и Ф2 – вход, для подачи тактовых

сигналов Ф1 и Ф2, которые являются непересекающимися во времени сигналами с

амплитудой 12 В и определяют тактовую частоту работы МП. Для формирования этих

сигналов используется микросхема КР580ГФ24.

Входы источников питания МП БИС – нулевой потенциал (земля),

+5В, -5В, +12В.

Микропроцессорная БИС состоит из

следующих функциональных блоков (рисунок 2): блока регистров общего назначения;

арифметико-логического блока; регистра команд РгК и

устройства управления УУ; буферов МД

(БФД) и МА (БФА).

Блок регистров общего назначения

(РОН) включает в сея шесть

программно-доступных регистров, которые составлены в пары: B, C; D, E; H, L. Их

можно использовать в программах как отдельные 8-разрядные регистры, а также как

три 16-разрядных регистра (B,D,H). Регистры W и Z не являются

программно-доступными и используются для выполнения команд внутри МП.

Программный счетчик PC содержит

текущий адрес памяти, к которому обращается программа. Содержание PC

автоматически изменяется в течение каждого цикла команды. Указатель стека SP

содержит адрес памяти, начиная с которого её можно применять для хранения и

восстановления содержимого программно-доступных регистров микропроцессора.

Двунаправленный шинный мультиплексор MX предназначен для связи РОНов с шиной данных МП; РА – это регистр для хранения

адреса памяти.

Арифметико-логический блок (АЛБ)

выполняет арифметические и логические операции под воздействием устройства

управления МП. Он включает в себя 8-разрядное АЛУ, схему десятичной коррекции

ДК, построенную на базе ПЗУ, 5-разрядный регистр признаков, аккумулятор А,

буфер аккумулятора БФА и буферный регистр БФРг.

Арифметико-логический блок позволяет осуществлять арифметические операции сложения,

вычитания, а так же основные логические операции (И, ИЛИ, исключающее ИЛИ) и

сдвиг. При проведении операций одно число всегда берется из буфера

аккумулятора, а другое из буферного регистра. По результату выполнения

арифметико-логических операций АЛБ устанавливает в регистре признаков пять

разрядов.

1. Бит переноса устанавливается (равен

«1») и сбрасывается (равен «0») при выполнении команд сложения, вычитания,

сдвига и логических команд и может быть программно проанализирован. Если в

результате выполнения операции появляется единица переноса из старшего разряда,

то бит переноса устанавливается, если же переноса не возникает, то бит переноса

сбрасывается.

2. Дополнительный признак переноса

устанавливается в единицу, если при выполнении команд возникает единица

переноса из третьего разряда числа. Состояние разряда может быть проанализировано

лишь командой десятичной коррекции числа.

3. Бит знака обеспечивает

представление в дополнительном двоичном коде числа от –12810 до +12710. При этом седьмой бит представляет

знак числа. Если он содержит единицу, байтом можно представить числа от –12810 до –110, если 0, то от 0 до +12710. В конце выполнения некоторых операций бит знака

устанавливается по седьмому биту результата.

4. Бит нулевого признака

устанавливается, если результат определенных операций равен 0. Бит нулевого

признака сбрасывается, если результат не нулевой. Если операция дает нулевой

байт результата и единицу переноса, то бит нуля так же устанавливается.

5. Разряд признака четности, в него

записывается единица, если при выполнении команды количество единиц в разрядах

результата будет четным.

Регистр команд РгК

и дешифратор команд ДШК используются в микропроцессоре для получения и

дешифрации команды. При извлечении команды, первый байт, содержащий ее код,

помещается в регистр команды и поступает на дешифратор команд.

Устройство управления совместно с

дешифратором формирует управляющие сигналы для всех внутренних блоков

микропроцессора, а так же его выходные сигналы управления и состояния.

Буферы МД и МА обеспечивают

хранение соответственно данных и адресов на время, необходимое для их обработки.

Выполнение каждой команды

производится микропроцессором в строгой последовательности, определяемой кодом

команды и синхронизируется во времени сигналами Ф1 и Ф2 тактового генератора.

Период синхросигналов Ф1 и Ф2

называется машинным тактом. Длительность машинного такта Т можно установить

произвольно в диапазоне 0,4…2 мкс.

Машинный цикл – время, требуемое

для извлечения одного байта информации из памяти или выполнения команды,

определяемой одним машинным словом. Машинный цикл может состоять из 3…5 машинных

тактов.

Время выполнения команды – время

получения, декодирования и выполнения команды. В зависимости от вида команды

это время может состоять из 1…5 машинных циклов. Для МП КР580ВМ80 существует десять

различных типов машинных циклов: извлечение кода команды; чтение данных из

памяти; запись данных в память; чтение данных из стека; запись данных в стек;

ввод данных из внешнего устройства; запись данных во внешнее устройство; цикл

обслуживания прерывания; останов; обслуживание прерывания при работе прерывания

в режиме останова.

Первым машинным циклом при выполнении

любой команды всегда является цикл извлечения кода команды. В первом такте

каждого машинного цикла МП указывает тип выполняемого цикла с помощью

8-разрядного слова состояния процессора, выдаваемого на МД.

Отдельные разряды слова состояния

задействуются в микроЭВМ для формирования сигналов в линиях магистрали

управления. Слово состояния выдается на МД лишь на короткий промежуток времени,

а используется на протяжении всего машинного цикла, поэтому его записывают в

специальный регистр слова состояния (РгСС).

Внешние устройства выдают сигналы

запроса на прерывания асинхронно по отношению к работе микропроцессора, путем

подачи уровня «1» на вход З.Пр. Запрос может быть

удовлетворён только в том случае, если микропроцессор находится в состоянии

разрешения прерывания. Микропроцессор автоматически устанавливается в состояние

запрета прерывания после выполнения начальной установки, у так же после начала

обслуживания запроса прерывания. Управление состоянием восприятия прерываний

может осуществляться программным путем, с помощью команд «запрет прерываний» и

«разрешение прерываний».

Микропроцессор указывает на

возможность восприятия прерываний сигналами на выходе Р.Пр.

Если на этом выходе присутствует уровень «1», то запросы прерываний могут быть

восприняты, в противном случае (уровень «0» на выходе Р.Пр)

запросы восприниматься не будут.

Обмен информацией между

микропроцессором и и внешними устройствами

организуется с помощью трех шин: адресов, данных и управления.

Шина адресов является

однонаправленной, выдача адресов на неё осуществляется лишь МП БИС.

Шина данных организует

двунаправленный обмен данными между МП БИС и памятью или внешними устройствами.

Максимальная нагрузочная способность её невелика, что не позволяет

непосредственно к ней подключать системы с большой емкостью памяти и широким

набором периферийных устройств. Для увеличения нагрузочной способности шины

данных применяют контроллер КР580ВК28.

Шина управления состоит из пяти

линий, сигналы на которых формируются из записанного слова состояния МП БИС и

его выходных сигналов ПРИЕМ и ЗАПИСЬ.

Восьмиразрядное машинное слово

микропроцессора КР580ВМ80 используется для сообщения МП БИС как кода команд,

так и данных. Набор команд микропроцессора фиксирован и состоит из 246

различных команд.

Команды МП можно разделить на пять

различных групп:

1. Команды пересылки данных,

осуществляющие пересылку данных между регистрами или между регистрами и

памятью.

2. Арифметические команды, включающие в себя команды сложения,

вычитания, увеличения или уменьшения на единицу данных.

3. Логические команды, позволяющие

осуществить логические операции И, ИЛИ, исключающее ИЛИ, сравнение, сдвиг или

взятие дополнения числа.

4. Команды передачи управления,

обеспечивающие безусловную передачу или передачу управления по условию, а так

же вызов или возврат из подпрограмм.

5. Команды управления или работы со

стеком, организующие ввод-вывод данных из микроЭВМ, доступ к стеку и

внутреннему регистру признаков МП БИС, а так же её применение.

Память микроЭВМ на базе МП КР580ВМ80

организована в виде 8-разрядных ячеек, каждая из которых имеет свой

16-разрядный адрес. Таким образом МП БИС может работать с памятью емкостью до

65536 байт. Многобайтовые команды записываются в последовательные ячейки памяти.

Первый байт команды всегда содержит код команды. При трехбайтовых командах во

втором и третьем байтах содержатся данные (адрес), причем во втором байте

записывается младший байт данных, а в

третьем – старший байт данных (адреса).

Микропроцессорная БИС имеет четыре

типа адресации к памяти или регистрам:

1. Прямая адресация – второй и третий

байты команды содержат указание адреса памяти: младший байт адреса во втором

байте команды, а старший – в третьем.

2. Адресация к регистру – команда

указывает на регистр или пару регистров, в которых записаны данные.

3. Косвенная адресация с помощью

регистров – команда указывает на пару регистров, в которых записан адрес

памяти, содержащей данные.

4. Непосредственная адресация –

команда сама содержит данные. При двухбайтовых данных во втором байте команды

записывается младший байт, а в третьем – старший.

За исключением режимов обслуживания

прерываний и выполнения команд передачи управления МП БИМ выполняет программы,

считывая команды непосредственно из памяти.

В командах передачи управления адрес,

к которому будет обращаться МП БИС, может указываться с помощью прямой или

косвенной адресации. При выполнении команд передачи управления по условию МП

БИС проверяет наличие этого условия и в случае его подтверждения осуществляет

передачу управления. При невыполнении условия программа будет продолжаться с

команды, записанной в ячейке памяти, следующей после команды передачи

управления по условию.