Изучение характеристик логических элементов комплементарной логики на транзисторах металл-оксид-полупроводниках

Контрольная

работа по ЦУиМП:

«Изучение

характеристик

логических

элементов КМОП»

Ключ на

основе КМОП

Рассмотрим

схему

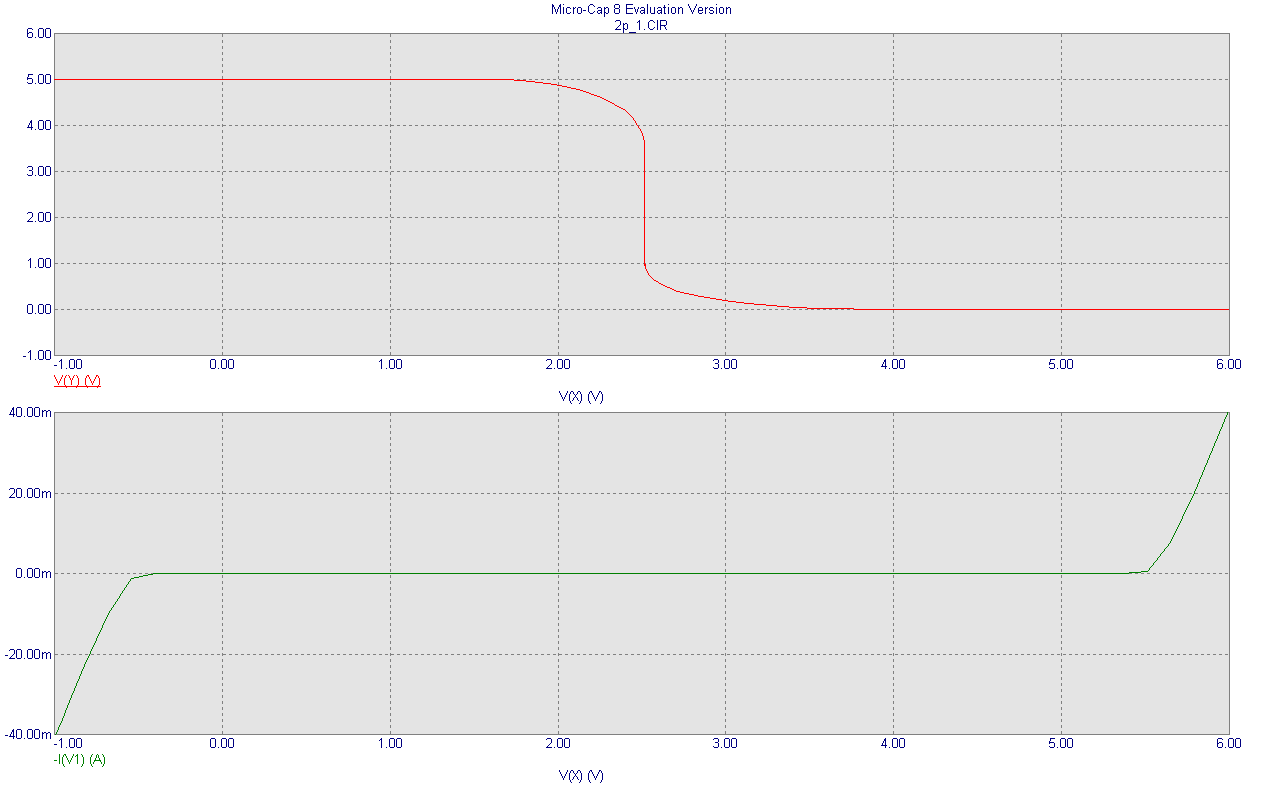

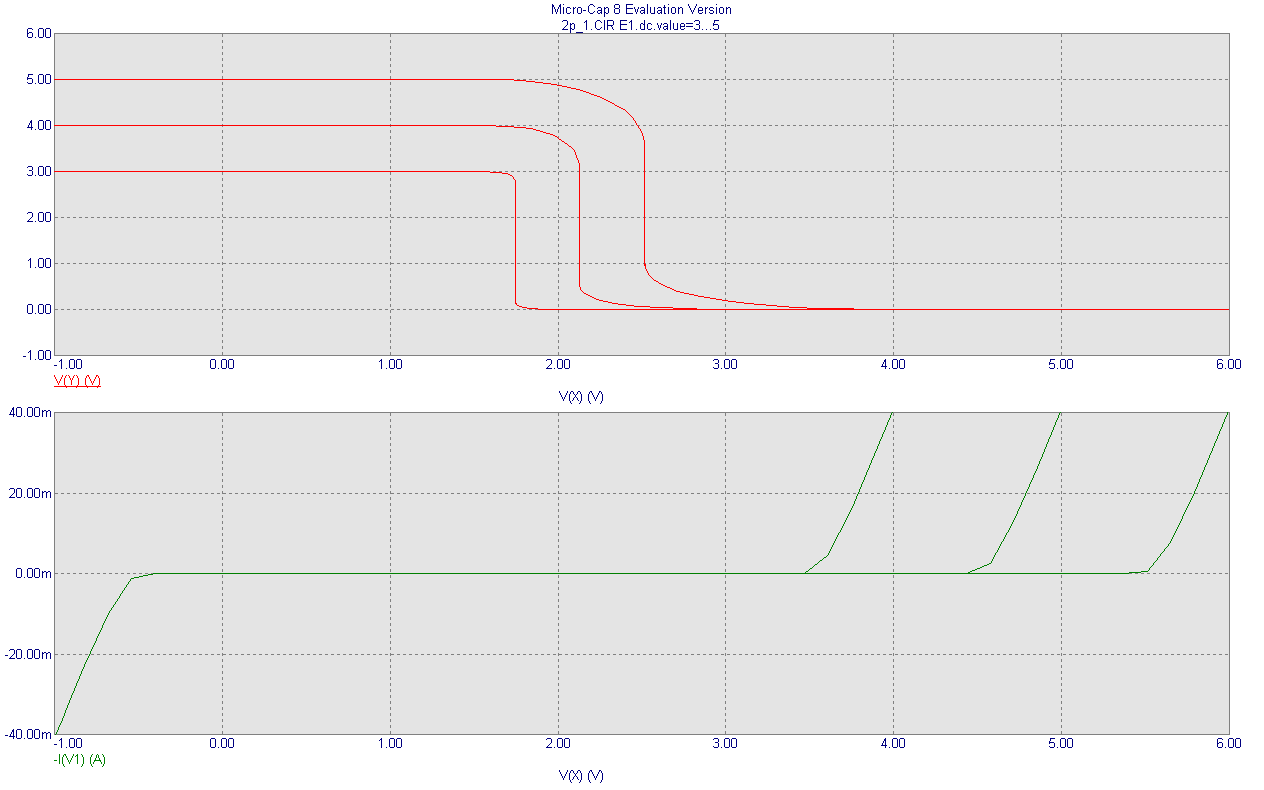

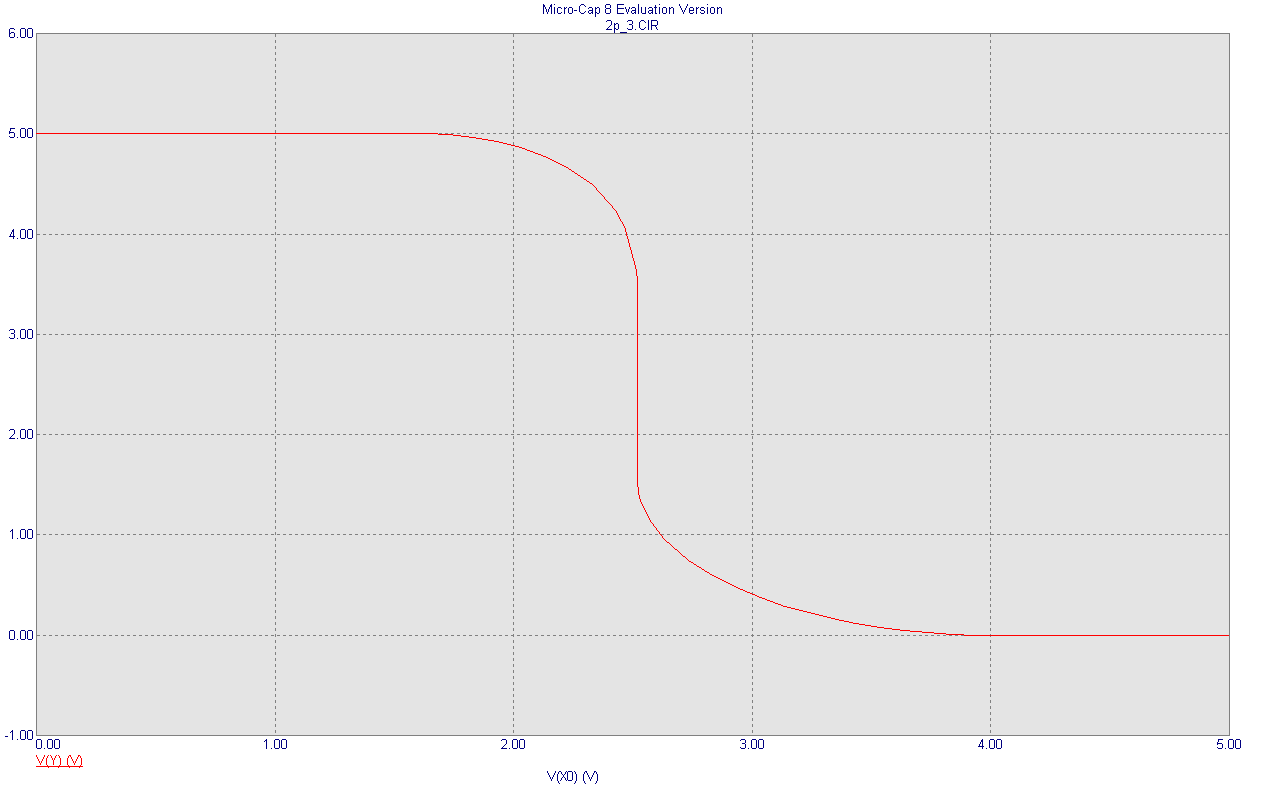

1) Получим

ПХ и определим

по ним значения

входного напряжения,

при которых

открываются

транзисторы

Т1, Т2 и защитные

диоды.

Определим

напряжения

открывания

(переключения)

транзисторов:

,

то

,

то

(по

графику 2.497 В)

(по

графику 2.497 В)

Определим

напряжение

открывания

защитных диодов:

т. к.

,

то входное

напряжение

открытия диодов

D1,2,3,4

(напряжение

открытия диодов

равно 0.6 В) равно

,

то входное

напряжение

открытия диодов

D1,2,3,4

(напряжение

открытия диодов

равно 0.6 В) равно

2)

Получить статические

характеристики

схемы при вариации

напряжения

питания

При

уменьшении

напряжения

питания происходит

уменьшение

напряжения

открытия транзисторов

в соответствии

с формулой

Еп/2.

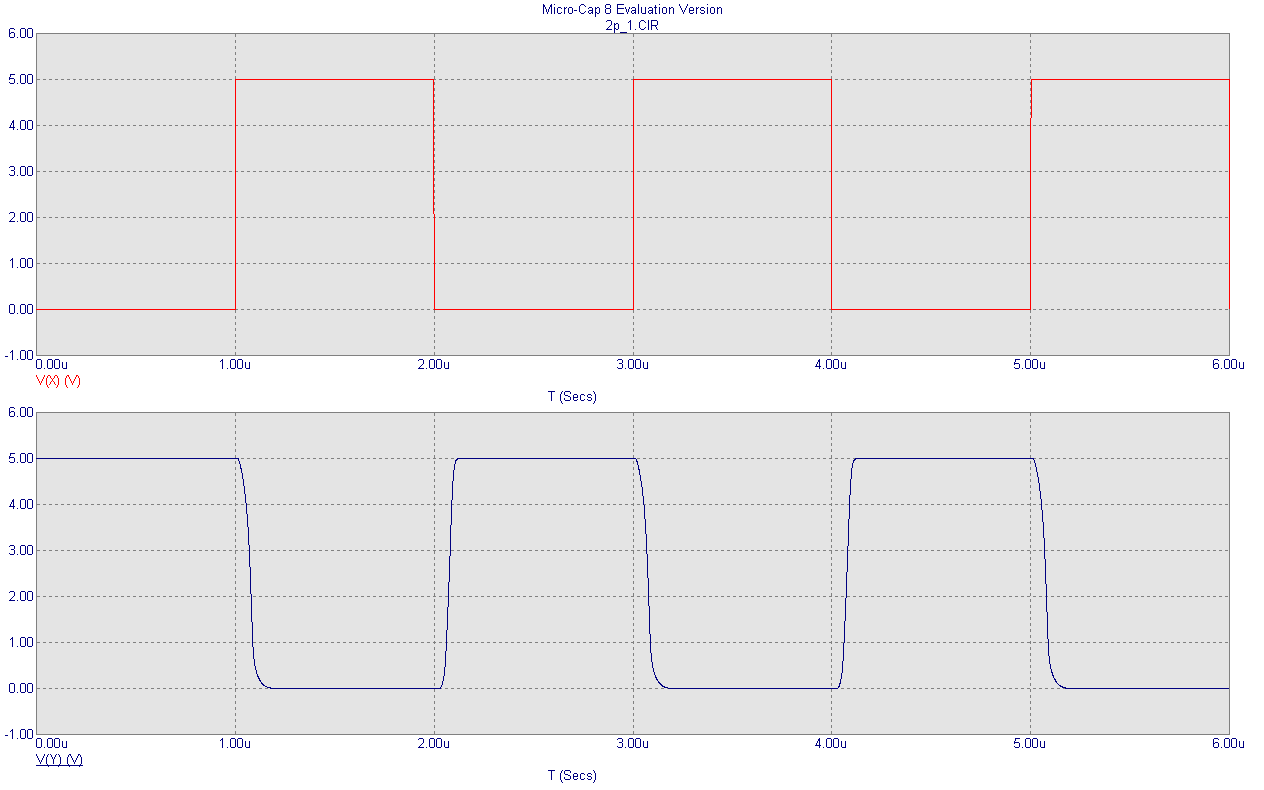

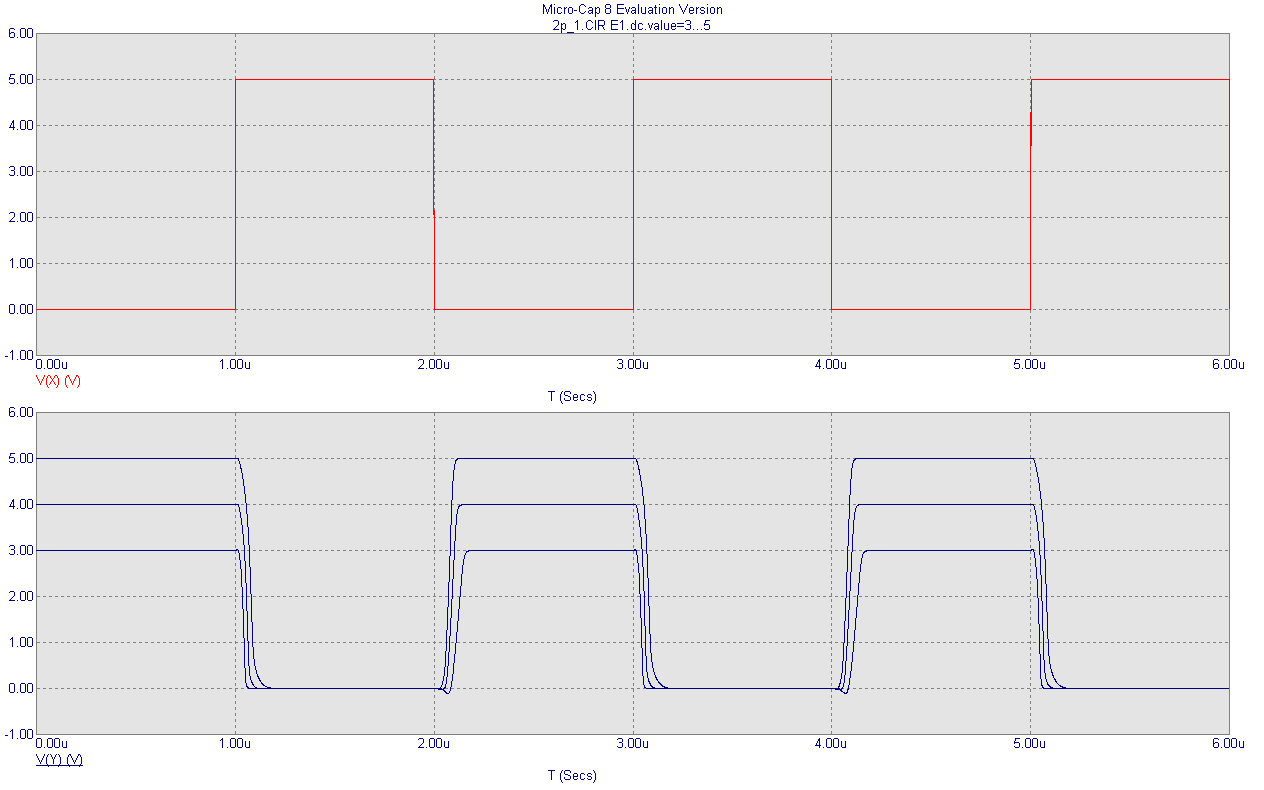

3)

Получить переходные

характеристики

Определим

длительность

переходных

процессов при

включении и

выключении

ключа и среднее

время задержки:

-

при переходе

выходного

сигнала с высокого

уровня на низкий

-

при переходе

выходного

сигнала с высокого

уровня на низкий

-

при переходе

выходного

сигнала с низкого

уровня на высокий

-

при переходе

выходного

сигнала с низкого

уровня на высокий

– среднее

время задержки

ЛЭ.

– среднее

время задержки

ЛЭ.

Тогда

4)

Получить переходные

характеристики

при вариации

напряжения

питания

Время

задержки при

переходе выходного

сигнала с высокого

уровня на низкий

( )

с уменьшением

напряжения

питания уменьшается,

а время при

переходе выходного

сигнала с низкого

уровня на высокий

(

)

с уменьшением

напряжения

питания уменьшается,

а время при

переходе выходного

сигнала с низкого

уровня на высокий

( )

при уменьшении

напряжения

питания растет.

)

при уменьшении

напряжения

питания растет.

ЛЭ КМОП

(ИЛИ-НЕ)

Рассмотрим

схему

1)

Получить статическую

характеристику

выходного

напряжения

от значения

статического

напряжения

на одном из

входов ключа

При

подаче на х1

напряжения

меньшего 2.5 В

(логический

ноль), в то время

как на два других

входа подано

напряжение

0 В, что соответствует

уровню логического

нуля, транзисторы

Т1, Т3 и Т5 закрыты,

а Т6, Т4 и Т2 открыты,

на выходе фиксируется

сигнал высокого

уровня соответствующий

логической

единице. При

подаче же на

х1

напряжения

высокого уровня

соответствующего

логической

единице транзисторы

Т3, Т2 и Т6 открыты,

а Т1, Т5 и Т4 закрыты.

На выходе схемы

напряжение

низкого уровня,

что соответствует

логическому

нулю.

2)

Получить таблицу

истинности

ЛЭ

Заменим

постоянные

источники

напряжения

Х2,1,0 на импульсные

источники, тем

самым задав

входные уровни

(0В – лог. нуль,

5В – лог. единица).

Тогда получим

след. График

анализа. По

нему составим

таблицу истинности:

| X0 |

X1 |

X2 |

Y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

0 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

0 |

Таким

образом, таблица

истинности

соответствует

стандартному

ЛЭ ИЛИ-НЕ, т.е.

если на одном

из входов есть

хотя бы одна

логическая

единица, то на

выходе Y

находится

логический

нуль, значит

можно утверждать,

что единица

это активное

значение логической

переменной,

при этом один

из транзисторов

Т2, Т4, Т6 заперт,

а один из транзисторов

Т1, Т3, Т5 открыт.

Если на всех

входах лог.

нули, то транзисторы

Т1, Т3, Т5 заперты,

а Т2, Т4, Т6 – открыты.

ЛЭ КМОП

(И-НЕ)

Рассмотрим

схему

Получить

статическую

характеристику

выходного

напряжения

от значения

статического

напряжения

на одном из

входов ключа

Когда

напряжение

на входе х0

соответствует

уровню логического

нуля, а напряжения

на двух других

входах при этом

соответствуют

уровню логической

единицы, можно

отметить. Транзисторы

Т1, Т4 и Т6 закрыты,

а Т2, Т3 и Т5 открыты,

причем сигнал

с транзисторов

Т3 и Т5 идет на

корпус, а с Т2

на выход, и уровень

этого выходного

сигнала соответствует

логической

единице.

Когда

напряжение

на входе х0

соответствует

уровню логической

единицы, а напряжения

на двух других

входах при этом

тоже соответствуют

уровню логической

единицы, можно

отметить. Транзисторы

Т2, Т4 и Т6 закрыты,

а Т1, Т3 и Т5 открыты,

причем сигнал

с транзисторов

Т1, Т3 и Т5 идет на

корпус, а на

выход поступает

сигнал очень

малого уровня,

соответствующего

логическому

нулю.

2) Получить

таблицу истинности

ЛЭ

Заменим

постоянные

источники

напряжения

Х2,1,0 на импульсные

источники, тем

самым задав

входные уровни

(0В – лог. ноль,

5В – лог. единица).

Тогда получим

след. график

анализа. По

нему составим

таблицу истинности:

| X0 |

X1 |

X2 |

Y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

0 |

Таким

образом, таблица

истинности

соответствует

стандартному

ЛЭ И-НЕ, т.е. если

на одном из

входов есть

хотя бы один

логический

нуль, то на выходе

Y

находится

логическая

единица, значит

можно утверждать,

что нуль это

активное значение

логической

переменной.

Если на всех

входах лог.

единицы, то

транзисторы

Т1, Т3, Т5 открыты,

а Т2, Т4, Т6 – заперты

– на выходе

лог. нуль.

Формирователь

коротких импульсов

(КМОП)

Рассмотрим

схему

Получить

статические

передаточные

характеристики

Согласно

передаточной

характеристики

при любом изменении

сигнала Х напряжение

на выходе Y

равно 5В (лог.

единица), а на

выходе Y1

0 В (логический

нуль).

Пусть

на Х=0, тогда на

А4=1, А5=0, А6=1, А2=1, А3=0

Y=1,

Y1=0

Y=1,

Y1=0

Пусть

на Х=1, тогда на

А4=0, А5=1, А6=0, А2=1, А3=0

Y=1,

Y1=0

Y=1,

Y1=0

Таким

образом на

нижнем входе

А2 всегда подается

сигнал

.

.

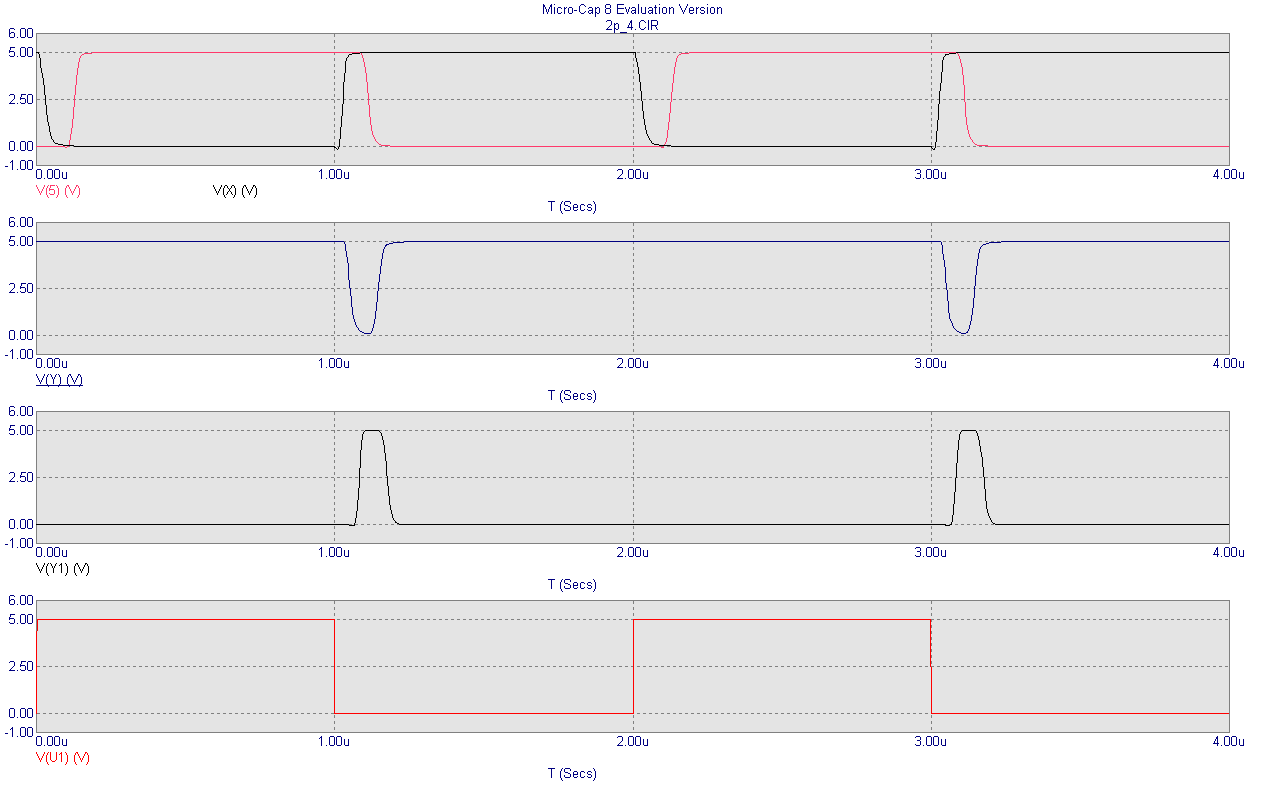

Получить

временные

диаграммы

сигналов Y

и Y1

По временной

диаграмме

видно, что значения

напряжения

на нижнем входе

А2 всегда инверсно

напряжению

в точке Х, однакоY1

не всегда равно

0, что казалось

бы не соответствует

полученным

ранее выводам.

Но это не так,

поскольку ЛЭ

А4, А5 и А6 содержат

в себе инерционные

элементы, такие

как транзистор,

сигналы идущие

на вход ЛЭ А2

придут на него

с разной задержкой,

таким образом

возможен подбор

ЛЭ, так что бы

на выходе Y1

мы получили

импульсы с

необходимым

периодом и

длительностью.

Найдем

длительность

импульсов Y1:

.

Время задержки

относительно

входного сигнала

.

Время задержки

относительно

входного сигнала

,

время задержки

сигнала Y

,

время задержки

сигнала Y

меньше

чем, время задержки

сигнала Y1,

что сказывается

наличием

дополнительного

элемента И-НЕ,

вносящего

дополнительную

задержку.

меньше

чем, время задержки

сигнала Y1,

что сказывается

наличием

дополнительного

элемента И-НЕ,

вносящего

дополнительную

задержку.

Формирователь

коротких импульсов

(интегрирующая

RC-цепь)

Рассмотрим

схему

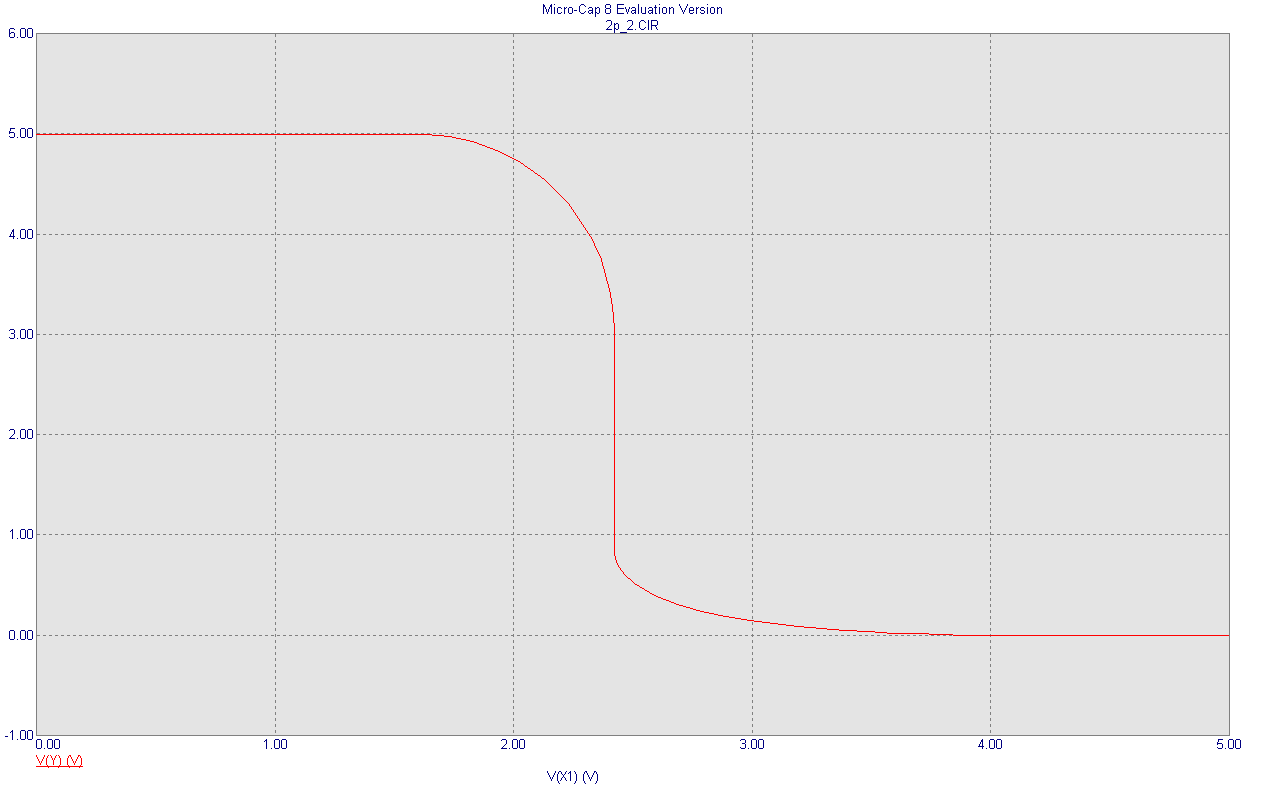

Получить

статические

передаточные

характеристики

Согласно

передаточной

характеристики

при любом изменении

сигнала Х напряжение

на выходе Y

равно 5В (лог.

единица), а на

выходе Y1

0 В (логический

нуль).

Пусть

Х=0, тогда А4=1, А2=1,

А3=0

Y=1,

Y1=0

Y=1,

Y1=0

Пусть

Х=1, тогда А4=0, А2=1,

А3=0

Y=1,

Y1=0

Y=1,

Y1=0

Получить

временные

диаграммы

сигналов Y

и Y1

Поскольку

в схеме 5 присутствует

RC

цепь интегрирующего

типа с постоянной

времени

,

то увеличивается

длительность

импульсов.

Следовательно

появляется

возможность

регулировать

длительностью

импульсов

изменяя постоянную

времени τ.

,

то увеличивается

длительность

импульсов.

Следовательно

появляется

возможность

регулировать

длительностью

импульсов

изменяя постоянную

времени τ.

Параметры

импульсов на

выходе:

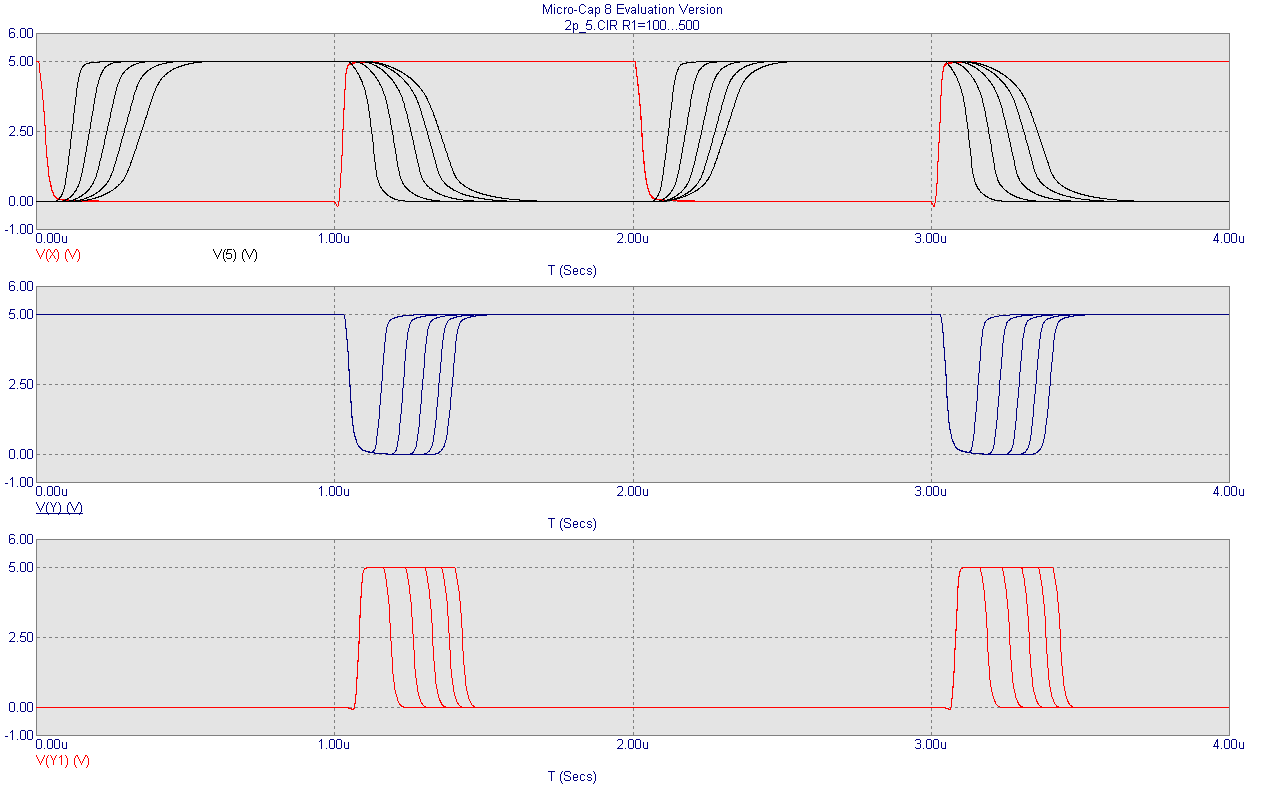

Получить

временные

диаграммы

сигналов Y

и Y1 при различных

значениях

резистора R1

При изменении

величины резистора

R1

происходит

изменение

постоянной

времени цепи.

При увеличении

величины

сопротивления

согласно формуле

постоянная

времени растет,

следовательно,

увеличивается

время импульса.

постоянная

времени растет,

следовательно,

увеличивается

время импульса.