Логические элементы интегральных микросхем

БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИНФОРМАТИКИ И

РАДИОЭЛЕКТРОНИКИ

КАФЕДРА РЭС

РЕФЕРАТ

НА ТЕМУ:

«Логические элементы интегральных микросхем»

МИНСК, 2009

Наиболее

распространены ЛЭ и схемы потенциального типа. Среди существующих логических элементов

(потенциальные, импульсные, импульсно-потенциальные) потенциальные ЛЭ и схемы

представляют наиболее распространенный класс. Основным отличительным признаком

ЛЭ и схем потенциального типа от импульсных и импульсно-потенциальных является

наличие связи по постоянному току между их входами и выходами. Другим

отличительным признаком является то, что они могут управляться и управлять

другими схемами с помощью сигналов как ограниченной (импульсные сигналы), так и

не ограниченной (потенциальные сигналы) длительности.

В

общем случае не исключается возможность применения в таких схемах реактивных

компонентов, т.е. индуктивностей и емкостей. Последние, как правило, играют

вспомогательную роль. Однако именно принципиальная возможность построения ИМС

различной сложности без реактивных компонентов выгодно отличает этот класс

устройств от остальных, поскольку процесс их изготовления наилучшим образом

соответствует возможностям микроэлектронной технологии.

Непрерывно

возрастает степень интеграции ИМС потенциального типа и сложность выполняемых

ими функций. Схемотехническая реализация ИМС потенциального типа осуществляется

на основе ряда типовых, базовых функциональных элементов.

Система

параметров

К

параметрам, характеризующим логические и схемотехнические возможности ЛЭ

микросхем и больших интегральных схем (БИС), относятся:

1.

реализуемая

логическая функция;

2.

нагрузочная

способность n, характеризующая возможность

подключения определенного числа идентичных ЛЭ (коэффициент разветвления по

выходу);

3.

коэффициент объединения

по выходу m (mи — для реализации логической функции И; mили — для реализации логической функции

ИЛИ) (коэффициент объединения по входу);

4.

средняя задержка

передачи сигнала τср (полусумма времени задержек передачи

сигналов 1 и 0 со входа ЛЭ на его выход);

5.

предельная

рабочая частота fр (частота переключения триггера,

составленного из рассматриваемых ЛЭ);

6.

помехоустойчивость;

7.

потребляемая

мощность.

По

виду реализуемой логической функции ЛЭ условно могут быть разбиты на два класса. К первому классу

относятся функциональные элементы одноступенчатой логики. Это простейшие

ЛЭ, реализующие функции И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ. Ко второму классу относятся

функциональные элементы двухступенчатой логики, реализующие более

сложные функции: И-ИЛИ, ИЛИ-И, НЕ-И-ИЛИ, И-ИЛИ-НЕ, И-ИЛИ-И и др.

Нагрузочная

способность ЛЭ n определяет число входов идентичных

элементов, которое может быть подключено к выходу каждого из них. При этом

обеспечиваются неискаженная передача двоичных символов 0 и 1 в цифровом

устройстве по цепи из произвольного числа последовательно включенных элементов

при наихудших сочетаниях дестабилизирующих факторов. Дестабилизирующими

факторами могут быть: изменение питающих напряжений, разброс параметров

компонентов, изменение температуры и т.п.

Часто

нагрузочная способность n

называется коэффициентом разветвления по выходу (Краз) и

выражается целым положительным числом (n=4, 5, 7, 10 и т. д.).

Чем

выше нагрузочная способность ЛЭ, тем шире их логические возможности и тем

меньше затраты при проектировании и построении цифрового устройства. Однако

увеличение параметра n

возможно до определенных пределов, поскольку при этом ухудшаются другие

параметры ЛЭ: снижается быстродействие, ухудшается помехоустойчивость и

увеличивается потребляемая мощность. Обычно в состав одной серии ИМС часто

входят ЛЭ с различной нагрузочной способностью: основные ЛЭ с n=4…10 и буферные элементы — так

называемые усилители мощности с n=20…50.

Это позволяет более гибко проектировать цифровые устройства, достигая

оптимальных показателей по потребляемой мощности и числу ЛЭ.

В

зависимости от частотного диапазона работы логических МДП-микросхем

(металл-диэлектрик-полупроводник) их нагрузочная способность может изменяться в

широких пределах (n=10…100).

Коэффициент

объединения по входу m (Коб)

характеризует максимальное число логических входов функционального элемента. С

увеличением параметра m

расширяются логические возможности микросхемы за счет выполнения функций с

большим числом аргументов на одном типовом элементе И-НЕ, ИЛИ-НЕ и т. п. Однако

при увеличении числа входов, как правило, ухудшаются другие параметры

функционального элемента, такие как быстродействие, помехоустойчивость и

нагрузочная способность.

С

точки зрения возможности увеличения коэффициента объединения по входу И или по

входу ИЛИ логические схемы существенно отличаются друг от друга. Например, в

ИМС где функция первой логической ступени выполняется на диодах или эмиттерных

переходах многоэмиттерного транзистора, увеличение числа входов не требует

существенных дополнительных затрат площади кристалла. В ИМС, где функция первой

логической ступени выполняется на транзисторах, увеличение параметра m требует значительного увеличения

числа компонентов ЛЭ и роста площади кристалла ИМС.

В

существующих сериях интегральных микросхем основные логические элементы

выполняются, как правило, с небольшим числом входов  . Увеличение числа входов m обеспечивается за счет введения в серию ЛЭ специального

расширителя, подключение которого к основной ИМС дает возможность увеличить mили и mи до 10 и более.

. Увеличение числа входов m обеспечивается за счет введения в серию ЛЭ специального

расширителя, подключение которого к основной ИМС дает возможность увеличить mили и mи до 10 и более.

К

основным динамическим параметрам логического элемента относятся:

tф1 — фронт формирования уровня

логической 1;

tф0 — фронт формирования уровня логического

0;

τ10

— задержка переключения из состояния 1 в состояние 0;

τ01

— задержка переключения из состояния 0 в состояние 1;

— длительность импульса;

— длительность импульса;

fp —

рабочая частота.

Определение

этих параметров обеспечивается при сравнении сигналов на входе и выходе ЛЭ, т.е.

при рассмотрении процесса передачи информации через ЛЭ.

На

рис. 1 приведены характеристики сигналов на входе и выходе инвертора и показаны

уровни отчета, относительно которых определяются динамические параметры ЛЭ.

Рис. 1. К определению

динамических параметров логического элемента (инвертора)

Уровням

отcчета динамических параметров ЛЭ

являются (рассматривается положительная логика, при которой высокий уровень

выходного сигнала соответствует 1, а низкий — 0) максимальный уровень

логического 0 и минимальный уровень логической 1. Задержка переключения τ10

определяется как временной интервал между уровнем 1 фронта нарастания входного

импульса (положительный импульс) и уровнем 0 фронта спада выходного импульса

(отрицательный импульс).

Задержка

переключения τ01 определяется как временной интервал между

уровнем 0 фронта спада входного импульса и уровнем 1 фронта нарастания

выходного импульса.

Фронты

импульса, определяемые между уровнями 1 и 0 спада импульса, обозначаются tф0, между уровнями 0 и 1 нарастания

импульса — tф1.

Средняя

задержка τср ЛЭ определяется как полусумма задержек τ10

и τ01 и служит усредненным параметром быстродействия,

используемым при расчете временных характеристик многоэлементных

последовательно включенных логических микросхем.

Произведение

средней задержки на число последовательно соединенных ЛЭ в устройстве дает наибольшую

задержку сигнала в этом устройстве. Параметр τср приводится в

технических условиях на ИМС. Для упрощения процесса расчета временных

характеристик сложных логических цепей часто считают сигналы прямоугольными, т.

е. tф0= tф1=0.

Помехоустойчивость. Базовый элемент ИМС в статическом

режиме может находиться в одном из двух устойчивых состояний (0 или 1). По этой

причине различают статическую помехоустойчивость ЛЭ по уровню 0 (Uno)и по уровню 1 (Un1). Статическая помехоустойчивость базовых элементов

ИМС определяется значением напряжения, которое может быть подано на вход ИМС

относительно уровня 0 или 1, не вызывая её ложного срабатывания (например,

переход из состояния 1 в состояние 0 или наоборот).

Напряжение

помехи либо повышает, либо понижает входное напряжение. Если на входе действует

напряжение логического 0 (U0), то опасны помехи, имеющие

положительную полярность, так как они повышают входное напряжение, что может

привести к сбою в работе, т. е. ложному изменению выходных напряжений в

цифровом устройстве. При поступлении на вход напряжения логической 1 (U1) и напряжения помехи отрицательной полярности также

возможно ложное переключение. Максимально допустимые постоянные напряжения

помехи положительной полярности (при напряжении логического 0 на входе) и

отрицательной полярности (при напряжении логической 1 на входе) определяют

помехоустойчивость ЛЭ по отношению к статическим (длительно действующим)

помехам.

Внутренние

помехи в цифровом устройстве возникают при переключении ЛЭ, поэтому их

амплитуда пропорциональна логическому перепаду Uл.

Логическим

перепадом называется

разность напряжений логической 1 и логического 0:

.

.

Для

оценки помехоустойчивости ЛЭ помимо напряжений Uп1 и Uп0 используют относительные величины:

;

;  ,

,

называемые

коэффициентом помехоустойчивости.

Для

повышения помехоустойчивости необходимо увеличивать логический перепад и

уменьшать время переключения ЛЭ из состояния 1 в состояние 0 и наоборот.

Потребляемая

мощность ЛЭ

(мощность, потребляемая ЛЭ от источника питания) зависит от его логического

состояния, так как изменяется ток Iи.п. в цепи

питания. ЛЭ потребляет ток

при

при  ;

;

при

при  .

.

Поэтому

средняя потребляемая мощность в статическом режиме.

.

.

Зная

среднюю мощность и число ЛЭ в цифровом устройстве Nл.э., можно вычислить среднюю мощность, потребляемую устройством;

она равна  . Уменьшить

потребляемую мощность можно, снизив напряжение или ток питания. Однако при этом

понизятся помехоустойчивость, а для многих типов ЛЭ и быстродействие. Наиболее

эффективный способ уменьшения мощности Pср реализован в ЛЭ на КМДП-транзисторах (комплементарный

металл-диэлектрик-полупроводник). В этих элементах токи в статическом режиме

малы, а мощность потребляется только при переключении. Мощность,

потребляемую дополнительно в процессе переключения, называют динамической.

Она пропорциональна частоте переключения ЛЭ. Поэтому динамическую мощность

определяют при заданной рабочей частоте, близкой к максимальной.

. Уменьшить

потребляемую мощность можно, снизив напряжение или ток питания. Однако при этом

понизятся помехоустойчивость, а для многих типов ЛЭ и быстродействие. Наиболее

эффективный способ уменьшения мощности Pср реализован в ЛЭ на КМДП-транзисторах (комплементарный

металл-диэлектрик-полупроводник). В этих элементах токи в статическом режиме

малы, а мощность потребляется только при переключении. Мощность,

потребляемую дополнительно в процессе переключения, называют динамической.

Она пропорциональна частоте переключения ЛЭ. Поэтому динамическую мощность

определяют при заданной рабочей частоте, близкой к максимальной.

Интегральные

элементы одноступенчатой логики

Логические

элементы микросхем потенциального типа с одноступенчатой логикой по

схемотехнической реализации и организации межэлементных связей делятся на

следующие типы:

·

резисторно-транзисторные

(RTL[*]);

·

транзисторные с

непосредственной связью (DCTL);

·

транзисторные с

резистивными связями (TRL);

·

транзисторные с

резистивно-конденсаторными связями (RCTL);

·

комплементарные с

транзисторно-резистивной логикой (CRTL);

·

диодно-транзисторные

(DTL);

·

транзисторные с

эмиттерными связями (ECL);

·

транзисторные с

инжекционной логикой (И2Л).

Резистивно-транзисторные

ИМС (RTL)

На

рис. 2 показаны электрическая и функциональная схемы ЛЭ ИС типа RTL, реализующего функцию ИЛИ-НЕ.

Операция ИЛИ осуществляется на резистивной сборке, а транзистор исполняет роль

усилителя-инвертора.

Рис. 2. Элемент двухступенчатой логики(DTL_-2)

а) схема элемента И-ИЛИ-НЕ;б) функциональное обозначение

Необходимо

отметить, что ЛЭ может работать в двух логических режимах. При высоком уровне

сигнала, принятом за логическую единицу (1), осуществляется так называемая

положительная логика работы элемента. Если за логическую 1 принять низкий

уровень, то имеет место отрицательная логика. В этом случае ЛЭ реализует

операцию И-НЕ. Такое преобразование логики работы элементов в зависимости от

принятой полярности сигнала логической 1 характерно и для всех других типов

потенциальных микросхем.

Транзисторные

ИМС с непосредственной, резистивной и резистивно-емкостной связью (DCTL, TRL, RCTL)

Транзисторные

ИМС с непосредственной связью являются одним из основных схемотехнических

направлений. Наиболее широко эта схемотехника применяется в ИМС на основе

МДП-структур. Возможна также реализация транзисторных ИМС с непосредственными

связями на основе биполярных транзисторов (Рис. 3).

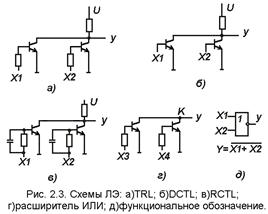

Рис 3. Схемы ЛЭ: а)TRL; б)DCTL; в)RCTL;

г) расширитель ИЛИ; д) функциональное обозначение

Включение

компенсирующих резисторов в базовые цепи транзисторов ЛЭ (рис.

3,

а) позволило значительно снизить рабочие токи и потребляемую мощность в TRL-ИМС. На основе элементов TRL были разработаны серии микромощных

ИМС с  . Однако включение

компенсирующих резисторов существенно снизило предельное быстродействие

микросхем до 1 МГЦ, но в тоже время обеспечило высокое значение параметров

n и m (n>4 и m>8). Для повышения быстродействия

элементов TRL параллельно базовому резистору были

включены форсирующие конденсаторы (рис. 3, в). Микросхемы такого типа получили

название транзисторных ИМС с резистивно-конденсаторными связями (RCTL). Предельное быстродействие

элементов такого типа повысилось до 5 МГц при сохранении значений

параметров n и m.

. Однако включение

компенсирующих резисторов существенно снизило предельное быстродействие

микросхем до 1 МГЦ, но в тоже время обеспечило высокое значение параметров

n и m (n>4 и m>8). Для повышения быстродействия

элементов TRL параллельно базовому резистору были

включены форсирующие конденсаторы (рис. 3, в). Микросхемы такого типа получили

название транзисторных ИМС с резистивно-конденсаторными связями (RCTL). Предельное быстродействие

элементов такого типа повысилось до 5 МГц при сохранении значений

параметров n и m.

Несмотря

на очевидные преимущества RCTL-ИМС

не получили распространения из-за сложности их изготовления, так как создание

идентичных и стабильных емкостей методами интегральной технологии является

сложной задачей. Конденсаторы, выполненные на основе короткозамкнутых p-n переходов, занимают большую площадь и имеют значительный

разброс характеристик, что снижает степень интеграции и процент выхода годных

ИМС в производстве.

Расширение

функциональных возможностей ИМС

Функциональные

возможности ИМС определяются:

1.

выполняемой

логической функцией;

2.

коэффициентом

объединения;

3.

нагрузочной

способностью элемента.

Для

транзисторной логики наиболее высокая нагрузочная способность достигается у TRL-ИМС (m=8…12 и n=4…5).

Однако часто при синтезе конкретных цифровых устройств требуется увеличение

параметра n у отдельных ИМС до 16…20, а параметр

m может изменяться в пределах 1…12.

Подключение

к основной логической схеме расширителей позволяет увеличивать емкость нагрузки

ИМС (точка К на рис. 3, г), но приводит к снижению их быстродействия.

Для

увеличения нагрузочной способности в состав серии микросхем включаются буферные

ИМС, представляющие собой усилители мощности. Для обеспечения высокого

быстродействия буферного усилителя, соответствующего быстродействию основных

микросхем серии, применяется симметричный транзисторный выход.

Буферные

усилители обеспечивают нагрузочную способность n>20 и работают при нагрузках Cн>100 пФ (допустимая емкостная нагрузка на основную

вентильную схему обычно не превышает 30 пФ). Буферная ИМС может выполнять

не только усилительные, но и логические функции за счет параллельного включения

m-транзисторов на входе и выходе.

Диодно-транзисторные

ИМС (DTL)

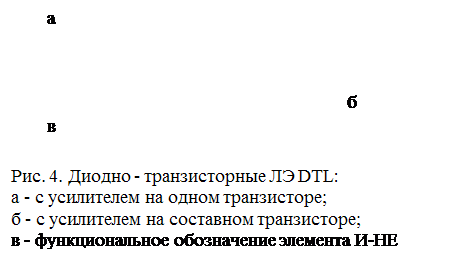

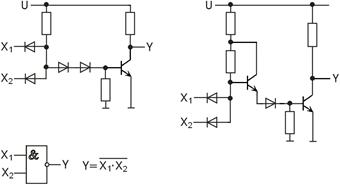

Базовые

функциональные элементы (рис. 4) диодно-транзисторных ИМС реализуют типовую

логическую функцию И-НЕ (для положительной логики). При этом функцию И

выполняют диодные группы, а функцию усилителя-инвертора-транзисторные схемы.

Известны

две наиболее распространенные разновидности DTL-ИМС:

1.

ИМС с

однотранзисторным усилителем на выходе;

2.

ИМС с усилителем

на составном транзисторе (усилитель Дарлингтона).

Базовые

элементы И-НЕ для двух указанных групп DTL-ИМС приведены на рис. 4, а, б соответственно.

Применение

усилителя на составном транзисторе позволяет снизить требования к коэффициенту

усиления интегральных транзисторов, а также расширить температурный диапазон

работы DTL-ИМС.

Модифицированные

DTL-ИМС со свободным коллектором

позволяют простым способом реализовать двухступенчатую логическую функцию

И-ИЛИ-НЕ за счет объединения коллекторов выходных транзисторов.

Общим

свойством описанных микросхем является использование нелинейного режима работы

активных элементов. Усилители логических схем характеризуются надежным

запиранием транзисторов в одном логическом состоянии и насыщением транзисторов

в другом.

Режим

насыщения не позволяет полностью использовать высокие частотные свойства

транзисторов в микросхеме, так как основная задержка определяется длительным

рассасыванием заряда при включении насыщенного транзистора.

В

связи с разработкой новых поколений ЭВМ встал вопрос о создании ИМС с

быстродействием более 50 МГц. Этим требованиям удовлетворяют ИМС с

эмиттерными связями (ECL-ИМС),

имеющие высокие динамические параметры.

ИМС

с эмиттерными связями (ECL)

В

базовом ECL-элементе ИЛИ, ИЛИ-НЕ обе логические

операции (ИЛИ, НЕ) выполняются эмиттерно-связанными транзисторами, чем и

обусловлено название типа логики. Элемент имеет два выхода, на одном из которых

фиксируется результат операции ИЛИ, а на другом — операции ИЛИ-НЕ. Обозначают

такой элемент ИЛИ, ИЛИ-НЕ.

Особенностью

микросхем транзисторной логики с эмиттерными связями (ECL) является ненасыщенный режим работы транзисторов,

что обеспечивает их высокое быстродействие. Вентильная ECL-ИМС выполняется на двух переключателях тока (рис. 5).

Один из них, нормально открытый, реализован на транзисторе, на базу которого

подано отпирающее напряжение U0. Уровень U0 ниже минимального уровня логической 1. Второй переключатель

тока состоит из m (по числу

логических входов) транзисторов, имеющих общие коллекторы и эмиттеры, что

обеспечивает реализацию функции ИЛИ. При отпирании любого транзистора второго

переключателя тока, повышается уровень напряжения на общем эмиттерном резисторе

R0 и обеспечивается запирание первого переключателя

тока, что приводит к формированию на выходе Y высокого уровня (логическая 1), в то время как на выходе  формируется низкий уровень

(логический 0). Следовательно, по выходу

формируется низкий уровень

(логический 0). Следовательно, по выходу  реализуется функция ИЛИ-НЕ, а по входу Y — логическая функция ИЛИ.

реализуется функция ИЛИ-НЕ, а по входу Y — логическая функция ИЛИ.