Министерство Образования и науки Республики Казахстан

Южно-Казахстанский политехнический колледж

Специальность: 3703 "Вычислительные машины, комплексы, системы и сети"

Курсовой проект

Учащийся: Марин С.

Группа: 472

Руководитель курсового

проектирования: Элиадзе Ю.А.

Содержание

Введение

1. Мониторы на основе ЭЛТ

1.1 Цифровые (TTL) мониторы

1.2 Монохромные цифровые мониторы

1.3 Цветные (RGB) цифровые мониторы

1.4 Аналоговые мониторы

1.5 Мультичастотные мониторы

2. Общая характеристика и описание монитора VIEWS0NIC-17GA/GL

2.1 Технические характеристики

3. Особенности конструкции

3.1 Схема разборки и сборки монитора VIEWSONIC 17GAA5L

4. Структурная схема монитора VIEWSONIC 17GAJGL

4.1 Структурная схема

4.2 Функциональная схема

4.3 Принципиальная схема

4.4 Тракт обработки видеосигналов

4.5 Система управления

4.6 Процессор разверток

4.7 Выходной каскад кадровой развертки

4.8 Выходной каскад строчной развертки

4.9 Источник высокого напряжения

4.10 Блок формирования напряжения динамической фокусировки

4.11 Схема поворота растра

4.12 Схема размагничивания кинескопа

4.13 Источник питания

4.14 Блок обработки аудиосигналов

5. Спецчасть. Одноплатный логический анализатор для устройства сопряжения (УС)

Заключение

Литература

С точки зрения принципа действия все мониторы для PC можно разделить на две большие группы.

Мониторы на основе электронно-лучевой трубки (ЭЛТ), называемой также кинескопом.

Плоскопанельные мониторы, выполненные, как правило, на основе жидких кристаллов, т.е. иначе жидкокристаллические (ЖК) или иначе LCD-мониторы (LiquidCrystalDisplay).

В данной дипломной работе производится исследование и анализ конструктивных особенностей, технического обслуживания и ремонта ЭЛТ мониторов PANASYNCSM70.

Наиболее распространенными устройствами отображения информации являются мониторы на основе ЭЛТ. Принцип действия таких мониторов мало отличается от принципа действия обычного телевизора и заключается в том, что испускаемый электронной пушкой пучок электронов, попадая на экран, покрытый люминофором, вызывает его свечение. На пути пучка электронов обычно находятся дополнительные электроды: модулятор, регулирующий интенсивность пучка электронов и связанную с ней яркость изображения, фокусирующий электрод, определяющий размер светового пятна, а также размещенные на горловине ЭЛТ катушки отклоняющей системы, позволяющие изменять направление пучка.

Любое текстовое или графическое изображение на экране монитора компьютера (так же как и телевизора) состоит из множества дискретных точек люминофора, представляющих собой минимальный элемент изображения (растра), называемых пикселами.

Такие мониторы называются растровыми.

Электронный луч в этом случае периодически сканирует весь экран, образуя на нем близко расположенные строки развертки.

По мере движения луча по строкам видеосигнал, подаваемый на модулятор, изменяет яркость светового пятна и образует видимое на экране изображение.

Разрешающая способность монитора определяется числом элементов изображения, которые он способен воспроизводить по горизонтали и вертикали, например, 640x480 или 1024x768 пикселов.

Если в телевизоре видеосигнал, управляющий яркостью (интенсивностью электронного пучка), является аналоговым, т.е. непрерывным по времени и уровню, то в мониторах PC может использоваться как аналоговый, так и цифровой видеосигнал.

В зависимости от этого мониторы на основе ЭЛТ принято разделять на аналоговые

и цифровые.

Исторически первыми устройствами отображения информации - мониторами для PC - были именно цифровые мониторы (TTL).

Управление цифровыми мониторами осуществляется двоичными сигналами, которые имеют только два значения: логическую единицу - "1" и логический ноль - "О" ("да" и "нет"). Уровню логической единицы соответствует напряжение около 5 В, уровню логического нуля - не более 0,4 В. Поскольку такие же уровни логической "1" (2,4-5 В) и логического "0" (0-0,4 В) используются в широко распространенной стандартной серии микросхем на основе транзисторно-транзисторной логики, или TTL (Transistor

Transistor

Logic

-

транзисторно-транзисторная логика), цифровые мониторы часто называют TTL-мониторами. Первые TTL-мониторы были монохромными, более поздние модели - цветными.

К этой группе относятся монохромные мониторы, сигналы управления которыми формируются графическими картами стандартов MDA (Monochrome

Display

Adapter

)

или Hercules, изредка - EGA (Enhanced

Graphics

Adapter

).

Уже из самого названия "монохромный" ясно, что точка на экране может быть только светлой или темной. В лучшем случае точки могут различаться еще и своей яркостью.

Монитор Hercules формирует изображение только в виде светлых и темных точек с разрешением 720x350; растр на его экране появляется только при подключении к PC. Это происходит потому, что блок развертки монитора генерирует сигналы для отклоняющей системы только при наличии внешних синхроимпульсов от видеоадаптера.

Поскольку ЭЛТ монохромного монитора имеет только одну электронную пушку, она меньше цветных ЭЛТ, благодаря чему мониторы Hercules компактнее и легче других мониторов. Кроме того, монохромный монитор работает с более низким анодным напряжением, чем цветной (15 кВ против 21-25 кВ), поэтому потребляемая им мощность значительно ниже (30 Вт вместо 80-90 Вт у цветных). Эти значения приводятся на обратной стороне корпуса монитора.

TTL-мониторы можно отличить от аналоговых также по количеству контактов на разъеме для подключения к PC: все они имеют двухрядный 9-контактный штекер типа в (вилка), тогда как аналоговые (VGA и выше) - трехрядный 15-контактный.

Поскольку кинескоп цветного монитора имеет не одну, а три электронные пушки для красного (Red

),

зеленого (Green

)

и синего (Blue

)

цветов с раздельным управлением, его также называют RGB

-монитором.

Заметим, что современные аналоговые мониторы также являются RGB-мониторами, поскольку термин "RGB-монитор" обозначает только тот факт, что сигналы основных цветов подаются на монитор независимо, по трем отдельным проводам, при этом характер сигнала (цифровой или аналоговый) значения не имеет.д.анный термин был введен для того, чтобы отличать такие мониторы от более ранних моделей цветных мониторов, управление которыми, подобно телевизору, осуществлялось композитным видеосигналом, несущим информацию о яркости и цветности и передававшимся по одному проводу. В частности, такой композитный видеосигнал может формировать видеоадаптер CGA (Color

Graphic

Adapter

),

для чего на нем имеется специальный коаксиальный разъем типа RCA, также известный под названием "тюльпан".

Цифровые RGB-мониторы предназначены для подключения к видеокартам стандарта CGA и EGA. Размер палитры (максимально возможное количество отображаемых цветов) каждого из мониторов определяется количеством двоичных сигналов, используемых для управления электронными пушками.

Видеосигнал на монитор CGA подается по четырем проводам: трем основным (R, G, В) и одному дополнительному (Intensity, или I). Сигнал I изменяет интенсивность электронных пучков, излучаемых всеми тремя пушками одновременно. В этом случае говорят о цветовой модели IRGB, позволяющей отобразить 24

= 16 цветов.

На монитор EGA видеосигнал подается уже по шести проводам: сигналы трех основных (R, G, В) и трех дополнительных (г, g, b) цветов, позволяющие индивидуально регулировать интенсивность электронного пучка каждой пушки. Такая модель называется RrGgBg. Она позволяет отобразить 26

= 64 оттенка цвета, однако ее возможности использованы в видеосистеме EGA лишь частично - из-за ограниченного объема видеопамяти для кодирования цвета пиксела используется не более 4 бит, поэтому одновременно можно отобразить только 16 цветов.

Помимо цветного, цифровые RGB-мониторы поддерживают и монохромный режим работы с отображением до 16 градаций серого (в этом случае сигналы трех цветов имеют одинаковую интенсивность). Цифровые RGB-мониторы (в частности, CGA) по сравнению с мониторами Hercules имеют меньшее разрешение. Назначение контактов разъемов мониторов CGA и EGA приведено в табл.1 и 2 соответственно.

Таблица.1.

Назначение контактов разъема

CGA

| Номер контакта |

Сигнал |

| 1 |

Корпус |

| 2 |

Корпус |

| 3 |

Красный |

| 4 |

Зеленый |

| 5 |

Синий |

| 6 |

Интенсивность |

| 7 |

Спецификация изготовителя |

| 8 |

Строчный синхросигнал |

| 9 |

Кадровый синхросигнал |

Таблица 2.

Назначение контактов разъема

EGA

| Номер контакта |

Сигнал |

| 1 |

Корпус |

| 2 |

Интенсивность (красный) |

| 3 |

Красный |

| 4 |

Зеленый |

| 5 |

Синий |

| 6 |

Интенсивность (зеленый) |

| 7 |

Интенсивность (синий) |

| 8 |

Строчный синхросигнал |

| 9 |

Кадровый синхросигнал |

В настоящее время цифровые мониторы являются большой редкостью, поскольку по современным меркам качество формируемого ими изображения, а также их эргономические свойства не выдерживают никакой критики. Можно смело утверждать, что они вредны для здоровья в целом и для зрения - в особенности.

Аналоговые мониторы это мониторах, которые работают с видеокартами стандарта VGA (Video

Graphics

Array

)

и выше. Они способны поддерживать разрешение 640x480 пикселов и более высокое.

Главная причина перехода к аналоговому видеосигналу состоит в ограниченности палитры цифрового монитора. При использовании двоичных видеосигналов расширение палитры возможно только за счет увеличения количества цветов, однако это тупиковый путь: если количество проводов в кабеле еще можно увеличить, то количество управляющих электродов (модуляторов) электронной пушки увеличить нельзя.

Если, к примеру, задаться целью получить режим TrueColor (24 бита на пиксел) на цифровом мониторе, то придется сконструировать ЭЛТ с тремя электронными пушками, каждая из которых должна иметь 8 (!) модуляторов. Совершенно очевидно, что это нереально.

В результате разработчики стали использовать не цифровой (двоичный), а аналоговый видеосигнал, который может принимать любое значение в диапазоне от 0 до 0,7 В. Поскольку этих значений бесконечно много, то палитра аналогового монитора не ограничена. Другое дело, что видеоадаптер может обеспечить только конечное количество градаций уровня видеосигнала, что в итоге ограничивает палитру всей видеосистемы в целом.

Аналоговые мониторы так же, как и цифровые, бывают цветными и монохромными, при этом цветной монитор может работать в монохромном режиме. Наиболее распространены, естественно, цветные мониторы, однако и монохромные аналоговые мониторы пользуются спросом, поскольку имеют ряд преимуществ по сравнению с цветными: меньшие габариты и энергопотребление, более низкую стоимость, лучшую резкость изображения (в них отсутствует зернистая структура люминофора, свойственная цветным мониторам).

Максимальное количество градаций серого, которое может отображать видеосистема с монохромным монитором, определяется видеоадаптером (точнее, разрядностью его цифроаналогового преобразователя и объемом видеопамяти). При использовании стандартного видеоадаптера VGA можно получить 64 оттенка серого, при использовании более современных адаптеров SVGA - 256.

Видеосигнал на аналоговый монитор подается через 15-контактный трехрядный D-образный разъем (стандартный разъем VGA, табл. .3). Поскольку полоса частот видеосигнала аналогового монитора значительно шире, чем у цифрового, для передачи RGB-сигналов используются витые пары (1-6, 2-7, 3-8). Наличие специальных битов идентификации позволяет видеоадаптеру автоматически определить, какой монитор подключен: цветной или монохромный. В последнем случае для передачи видеосигнала задействуется только одна пара контактов 2-7.

Таблица 3.

Назначение контактов разъема

VGA

Номер

контакта

|

Сигнал

|

Номер

контакта

|

Сигнал

|

| 1 |

Красный |

9

|

Ключ (контакт отсутствует)

|

| 2 |

Зеленый |

10

|

Нулевой (синхроимпульсы)

|

| 3 |

Синий |

11

|

Бит идентификации 0

|

4

|

Бит идентификации 2

|

12

|

Бит идентификации 1

|

5

|

Земля (общий провод)

|

13

|

Строчные синхроимпульсы

|

6

|

Нулевой (красный)

|

14

|

Кадровые синхроимп ульсы

|

7

|

Нулевой (зеленый)

|

15

|

Не используется

|

8

|

Нулевой (синий)

|

Синхронизация означает не что иное, как временное согласование двух или более элементов. Она необходима также для согласования работы видеоадаптера и монитора. С этой точки зрения видеоадаптер формирует два сигнала синхронизации: строчной частоты (сигнал синхронизации по горизонтали, или строкам; измеряется в килогерцах) и кадровой частоты (сигнал синхронизации по вертикали, или кадрам; измеряется в герцах). В различных режимах и, соответственно, при различных разрешениях частоты этих сигналов могут различаться.

Все современные мониторы в первом приближении можно разделить на три большие группы:

с фиксированной частотой;

с несколькими фиксированными частотами;

многочастотные (их также называют мультичастотными).

Мониторы с фиксированной частотой воспринимают синхросигналы какой-либо одной частоты, например, для кадровой развертки 60 Гц, для строчной - 31,5 кГц. Мониторы с несколькими фиксированными частотами менее критичны к значениям частот синхроимпульсов и могут работать с набором из двух или более сочетаний частот кадровых и строчных синхроимпульсов. Мультичастотные мониторы, называемые иногда Multisync (по названию мониторов, выпускаемых фирмой NEC), обладают способностью настраиваться на произвольные значения частот синхросигналов из некоторого заданного диапазона, например, 30-64 кГц для строчной и 50 - 100 Гц для кадровой развертки.

МОДЕЛЬ

VS1769-GA-1

Монитор VIEWSONIC 17GA/GL

модели VS1769-GA-1 производства фирмы MATSUSHITA ELECTRIC (PANASONIC) предназначен для работы в стационарных условиях. В нем применена цветная электронно-лучевая трубка с повышенными эксплуатационными характеристиками, в которой использованы электронная пушка с двойной системой излучателей, маска с антистатическим тонирующем покрытием из инвара, а также дополнительная зашита от излучений.

Схема и конструкция монитора VIEWSONIC 17

GA

/

GL

обеспечивают выполнение следующих функций:

обработку и отображение текстовой и графической информации, поступающей в стандартах обмена VGA, SVGA;

поддержку стандарта VESADDC;

вывод на экран перечня меню;

самотестирование;

оптимизацию задач OSD;

обеспечение высокого качества изображения в широком диапазоне цветовых оттенков;

минимизацию искажений растра;

динамическую фокусировку лучей;

обеспечение цифровой технологии мультиразвертки (8 режимов) с настройкой и отслеживанием заданных параметров;

поддержку микропроцессора системной шины 1%;

хранение в памяти 13 градаций оперативных настроек;

контроль и блокировку смещения (вращения) растра;

высокое качество воспроизведения звука за счет использования встроенных динамических головок;

возможность использования встроенного или внешнего микрофона, а также выносных динамических головок;

подавление помех типа "муар";

адаптацию к колебаниям напряжения питания в диапазонах 90-132 В, 198-264 В.

Монитор VIEWSONIC 17GAA3L имеет следующие технические характеристики:

| Тип кинескопа |

М41КХН140Х |

| Диагональ кинескопа |

17" (43см) |

| Угол отклонения луча |

90е

|

| Размер зерна экрана |

не более 0,27 мм |

| Частотный диапазон разверток: по горизонтали по вертикали |

30-70 кГц 50-180 Гц |

| Максимальная разрешающая способность |

1280x1024 |

| Входной видеосигнал |

аналоговый |

| Амплитуда сигнала на комплексной нагрузке |

75 Ом 0,7 В |

| Входной синхросигнал |

дискретный, однопол ярный, ТТЛ уровень |

| Смешанный синхросигнал |

дискретный, биполярный, ТТЛ уровень |

| Динамический диапазон входного видеосигнала |

0-0.7 8 |

| Полоса видеочастот |

не менее 100 МГц |

| Номинальная выходная мощность аудиосигнала |

3x3 Вт |

| Напряжение питания |

-90-132 В, - 198-264 В; 50У60 Гц |

| Потребляемая мощность |

100 Вт |

| Размеры |

418x438x438 мм |

| Вес |

18,5 кг |

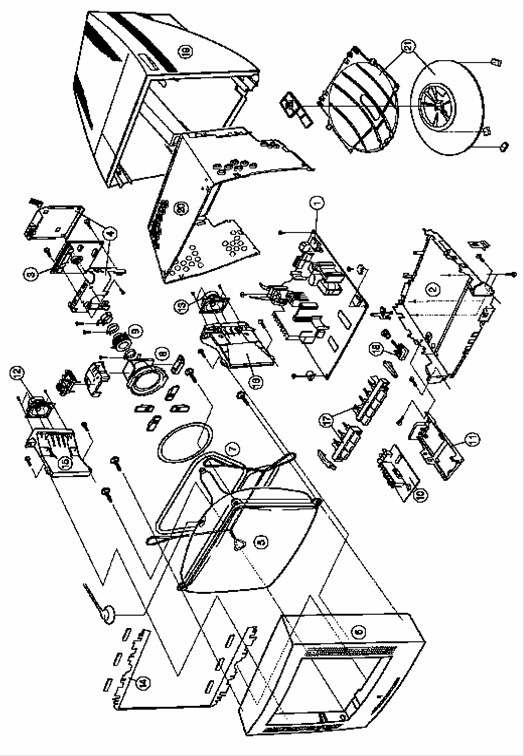

Конструктивно все электронные компоненты монитора VIEWSONIC 17

GA

/

GL

расположены на платах, которые имеют следующее обозначения:

основная плата (MAINPCB);

плата обработки видеосигналов (CRT);

плата обработки аудиосигналов (AUDIOPCB).

В состав монитора VIEWSONIC 17GA/GL также входят:

кинескоп (CRT);

петля размагничивания кинескопа;

отклоняющая система;

маска кинескопа;

корпус;

подставка;

сегмент поворотного механизма;

держатель динамической системы.

На основной плате (1), которая является сложным конструктивным элементом, смонтированы главные функциональные узлы монитора.

С целью зашиты от механических повреждений основная плата (1) установлена в специальный пластмассовый каркас (2) сложной конфигурации с несколькими ребрами жесткости и пружинящими замками. В каркасе имеются направляющее плоскости, позволяющее фиксировать основную плату в корпусе монитора, а также отверстия для винтов, которыми она крепится к ребрам жесткости. В каркасе (2) сделаны сквозные отверстия для обеспечения циркуляции воздуха.

Блок обработки видеосигналов собран на отдельной плате (3) в экранирующем кожухе (4) и закреплен на горловине кинескопа (5).

Экран кинескопа защищен от механических повреждений маской (14), которая вместе с электронно-лучевой трубкой (5) и петлей размагничивания (7) жестко крепится винтами к передней панели (6) монитора.

На горловине кинескопа размешаются катушки отклоняющей системы (8) и магниты (9). Плата обработки аудиосигналов (10) установлена на пластмассовом каркасе (11), который крепится винтом к каркасу основной платы. Динамические головки (12,13) расположены на кронштейнах (15,16), закрепленных на передней панели.

Для кнопок клавиатуры управления (17) и клавиши включения (18) в нижней части передней панели монитора предусмотрены соответствующее отверстия.

Все основные узлы и блоки монитора помешаны в корпус (19) с металлическим экраном (20), который помимо функции зашиты обеспечивает необходимую жесткость изделия.

Предусмотрена возможность вращения монитора в разных плоскостях и вокруг собственной оси, что достигается благодаря специальной подставке (21), оборудованной шарнирным механизмом.

Рис.1. Схема разборки и сборки монитора VIEWSONIC 17GAA5L

В состав монитора VIEWSONIC 17

GA

/

GL

входят следующее основные узлы и блоки:

тракт обработки видеосигналов;

блок обработки аудиосигналов;

система управления;

процессор разверток;

выходной каскад кадровой развертки;

выходной каскад строчной развертки;

блок питания;

источник высокого напряжения;

схема поворота растра;

схемы коррекции;

схема размагничивания кинескопа;

блок формирования напряжения динамической фокусировки.

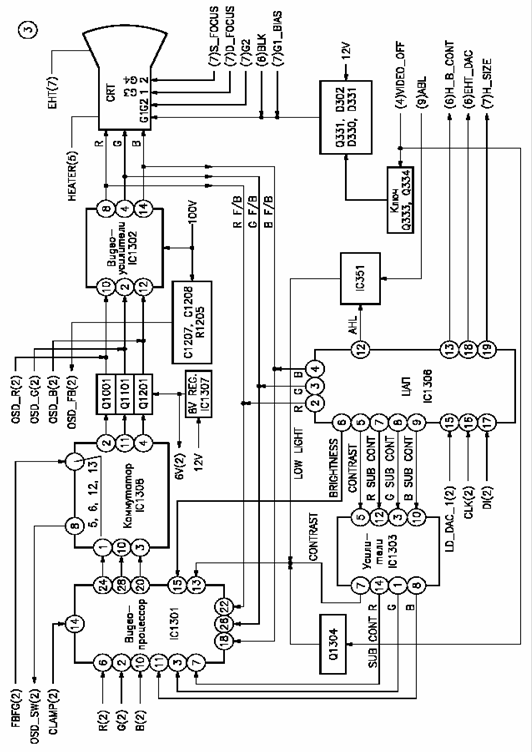

Входные сигналы R, G, В через 15-контактный разъем и диодный ограничитель, предотвращающей повреждение монитора при отсоединении компьютера, поступают на видеоусилители, расположенные в видеопроцессоре IC1301.

Каскады микросхемы IC1301 помимо усиления обеспечивают регулировку уровня усиления и яркости, а также гашение при обратном ходе лучей. Регулировка уровня усиления может производиться как одновременно для всех каналов, так и раздельно для каждого цвета.

С выходов предварительных видеоусилителей сигналы R, G, В через переключатели (IC308), осуществляющие коммутацию входных сигналов и сигналов служебной информации системы OSD, подаются на оконечные видеоусилители (IC1302). Выходные сигналы оконечных усилителей проходят на катоды кинескопа.

Сигналы синхронизации могут быть раздельными (VS, HS), комбинированными (CS), а также подмешанными в видеосигнал зеленого цвета. Эти сигналы с контактов 15-контактного разъема подаются на селектор синхроимпульсов, выполненный на микросхеме IC201. Выделенные синхроимпульсы поступают на процессор управления IC901.

Процессор IC901 вместе с микросхемой энергонезависимой памяти IC902, микросхемами ЦАП (IC1306, IC502, IC751) и клавиатурой образует систему управления. Система управления производит анализ синхроимпульсов и выбор режима работы, обработку сигналов, поступающих от других узлов монитора, от схем развертки и от блока питания при возникновении аварийных режимов, а также обеспечивает доступ оператора через экранное меню к оперативным регулировкам.

Экранное меню и сигналы системы OSD формируются микросхемой IC1305, управляемой по цифровой шине.

При выборе режима происходит установка частот развертки и их привязка к синхроимпульсам, а также формирование необходимых сигналов коррекции растра в соответствии с установленным режимом.

Синхроимпульсы VS и HS запускают генераторы строчной и кадровой разверток, выполненные на микросхеме IC501.

Импульсы запуска строчной развертки с соответствующего выхода процессора разверток IC501 поступают на выходной каскад строчной развертки, выполненный на транзисторах 0549. Q550. Выходной каскад строчной развертки вырабатывает пилообразный ток отклонения лучей в строчных отклоняющих катушках, напряжение питания схемы размагничивания, ускоряющее и фокусирующее напряжения, а также высокое напряжение для питания первого анода кинескопа.

На соответствующем выводе процессора разверток IC501 формируются пилообразные импульсы, которые поступают на выходной каскад кадровой развертки (IC490), нагруженный на кадровые отклоняющие катушки.

Процессор управления IC901 посредством дискретных команд и аналоговых сигналов воздействует на выходные каскады строчной и кадровой разверток, блок управления питанием строчной развертки, а также на схему поворота растра (IC101,0101 - 0104) с целью коррекции параметров растра в соответствии с выбранным режимом и установленными значениями оперативных регулировок. Аналоговые сигналы управления формируются с помощью ЦАП (IC1306, IC502, IC751).

Блок формирования напряжения динамической фокусировки (IC302, IC303,1С313) вырабатывает импульсное напряжение параболической формы, которое складывается с постоянным напряжением и позволяет производить фокусировку растра по всему полю сверхплоского экрана кинескопа.

Источник питания обеспечивает преобразование напряжения сети 220 В переменного тока в постоянные напряжения +5 В, +12 В, +24 В, +33 В, +100 В, +183 В, а также +17 В для блока обработки аудиосигналов и нити накала кинескопа.

В мониторе имеется блок обработки аудиосигналов, на груженный на малогабаритные громкоговорители или головные телефоны, который усиливает звуковые сигналы левого и правого каналов, поступающее от компьютера.

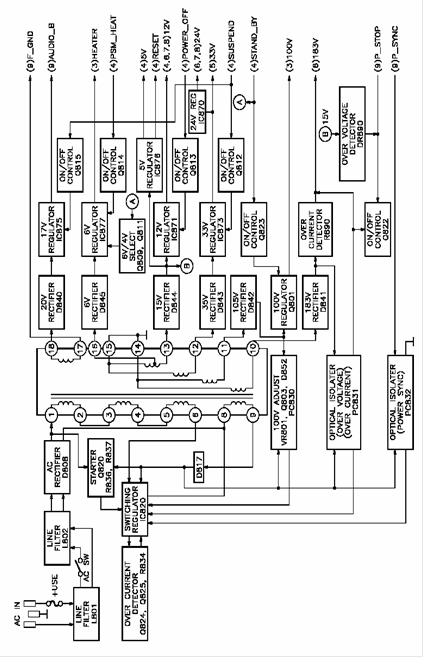

Рис.2. Структурная схема монитора VIEWSONIC 17GAJGL

Общая функциональная схема монитора VIEWSONIC 17GAA5L

Функциональные схемы, поясняющие работу отдельных блоков, узлов и каскадов монитора, приведены ниже:

Функциональная схема селектора видеосигналов и Формирователя сигналов системы OSD

Функциональная схема выходных каскадов тракта обработки видеосигналов

Функциональная схема системы управления

Функциональная схема процессора разверток и выходного каскада кадровой развертки

Функциональная схема выходного каскада строчной развертки и источника высокого напряжения

Функциональная схема узла поворота растра

Функциональная схема источника питания

Функциональная схема блока обработки аудиосигналов

Во избежание повторов рассмотрение функциональных схем будет осуществляться одновременно с описанием принципиальных схем соответствующих блоков, узлов и каскадов монитора.

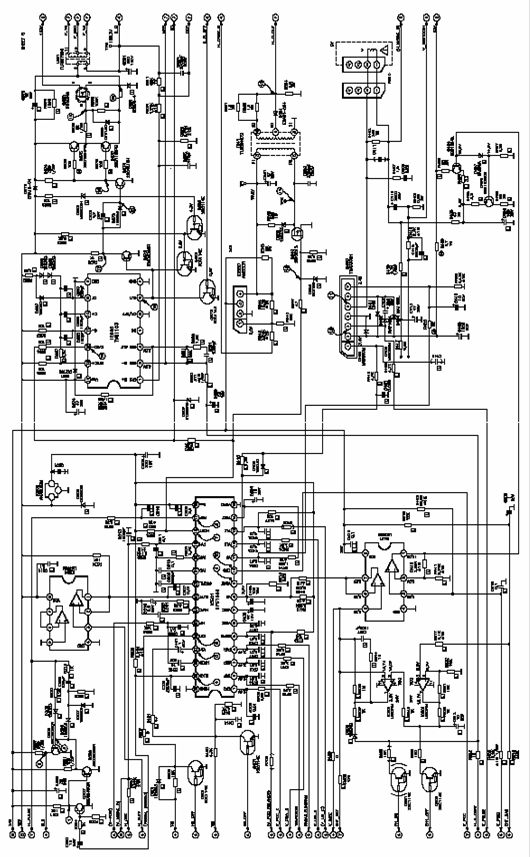

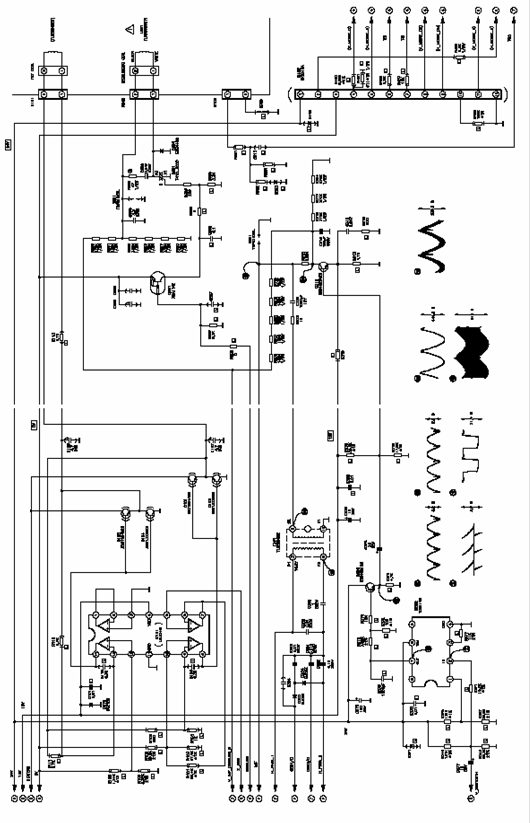

Принципиальные схемы блоков и узлов монитора VIEWSONIC 17GA/GL приведены ниже:

Принципиальная схема тракта обработки видеосигналов

Принципиальная схема системы управления

Принципиальная схема процессора разверток и выходного каскада кадровой развертки

Принципиальная схема выходного каскада строчной развертки и источника высокого напряжения

Принципиальная схема блока Формирования напряжения динамической Фокусировки кинескопа

Принципиальная схема источника питания

Принципиальная схема усилителя сигналов емкостного датчика

Принципиальная схема блока обработки аудиосигналов.

Функциональная схема селектора видеосигналов и формирователя сигналов системы OSD

Функциональная схема выходных каскадов тракта обработки видеосигналов

Принципиальная схема тракта обработки видеосигналов

Каскады тракта обработки видеосигналов расположены на двух платах, заключенных в экранирующей кожух и закрепленных на горловине кинескопа.

В состав тракта входят видеопроцессор IC1301 и выходной усилитель видеосигналов, выполненный на микросхеме IC1302. Управление параметрами видеоусилителей осуществляется выходными сигналами цифро-аналогового преобразователя IC1306.

На плате кинескопа расположены формирователь сигналов системы OSD, выполненный на микросхеме IC1305, а также микросхема IC201, содержащая селектор синхроимпульсов, детектор режимов и генератор импульсов CLAMP.

Видеосигналы основных цветов поступают через соединительный кабель на 15-контактный разъем N103 монитора. На этот же разъем приходят импульсы синхронизации горизонтальной и вертикальной разверток или комплексный синхросигнал.

С контактов разъема N103 видеосигналы основных цветов через согласующее индуктивности L1003, L1103, L1203, расположенные на основной плате, и контакты разъема N7 поступают на плату кинескопа.

Через согласующее индуктивности L1001, L1101, L1201 и разделительные конденсаторы С1001, С1101, С1201 видеосигналы проходят на цепи схемы защиты, состоящее из двух диодов и токоограничивающего резистора (D1001, D1002, R1004; D1101, D1102, R1104; D1201, D1202, R1204). Затем сигналы основных цветов подаются на соответствующее входы видеопроцессора IC1301 (M52326SP).

Микросхема M52326SP содержит три линейных широкополосных усилителя видеосигналов. При этом усиление каналов может регулироваться как независимо (выводы 101301/2,6,10), так и одновременно (вывод IC1301 /13). Сигналом CLAMP (вывод IC1301 /14) осуществляется гашение обратного хода лучей.

Выходные сигналы с выводов IC1301 /24,28,20 через аналоговый переключатель, выполненный на микросхеме IC1308 (74НС4066М), передаются на каскады оконечных видеоусилителей. Микросхема 74НС4066М является переключателем аналоговых и цифровых сигналов и выполнена по КМОП технологии. Ее полный аналог - микросхема К561КТЗ.

Коммутация видеосигналов происходит при поступлении сигнала FBKG на входы управления коммутацией входных видеосигналов и сигналов OSD (выводы 101308.15,6,12,13).

С выходов коммутатора (выводы 101308/2,4,11) видеосигналы через эмиттерные повторители, выполненные на транзисторах 01001,01101,01201, подаются на частотно зависимые делители (R1006, R1010, R1011, R1024, С1006, С1013 - для сигнала красного цвета; R1106, R1110, R1111, R1124, С1106, СП 13 - для сигнала зеленого цвета; R1206, R1210, R1211, R1224, С1206, С1213 - для сигнала синего цвета). На входы этих делителей приходят также сигналы основных цветов системы OSD. С выходов частотно-зависимых фильтров видеосигналы основных цветов подаются на выводы 10,2 и 12 микросхемы IC1302 (EY07PV2).

В составе микросхемы EY07PV2 имеются три идентичных высоковольтных усилительных каскада. Усиленные сигналы через цепи коррекции и защиты поступают на соответствующее катоды кинескопа.

Устойчивость работы выходных усилителей микросхемы IC1302 обеспечивается отрицательными обратными связями с выхода каждого усилителя на его вход (резисторы R1019,R1119,R1219).

Часть выходного сигнала снимается с соответствующего делителя напряжения (R1013, R1014; R1113, R1114; R1213, R1214) и в качестве сигнала обратной связи используется совместно с выходными сигналами микросхемы IC1306 для стабилизации уровня черного. Эти сигналы поступают на входы обратной связи видеопроцессора (выводы 101301/22,26, 20).

Цепи коррекции в каждом канале обеспечивают подъем в области верхних частот (R1023, С1010; R1123, С1110; R1223, С1210), а также компенсируют вредное влияние входной емкости катодов (L1002, R1012; L1102, R1112; L1202, R1212).

Зашита выходных каскадов от повреждения при пробоях внутри кинескопа осуществляется диодами D1006, D1007, D1106, D1107, D1206, D1207 и разрядниками S1001, S1101, S1201.

Питание выходных каскадов видеоусилителей производится от источника напряжения +100 В.

Управление изменением коэффициента усиления предварительных видеоусилителей (регулировка контрастности) и регулировка цветового баланса происходят по сигналам, которые в виде цифрового кода поступают с выводов IC901 /18,19 процессора управления на выводы 16 и 17 микросхемы IC1306 (МВ88346В). На вывод IC1306/18 от процессора управления приходит также сигнал идентификации.

Микросхема МВ88346В является цифро-аналоговым преобразователем. Выходные сигналы этого ЦАП используются для регулировки яркости, контрастности, цветового баланса, в системах стабилизации уровня черного и ограничения тока луча, а также для регулировки размера изображения по горизонтали, стабилизации высокого напряжения питания кинескопа и контроля величины управляющего напряжения источника питания выходного каскада горизонтальной развертки (H_B_CONT). Выходной сигнал ЦАП используется также в системе контроля ограничения тока луча.

Напряжение регулировки яркости с вывода 1С1306Д5 поступает на вывод IC1301/15 видеопроцессора непосредственно, а напряжения регулировки контрастности (вывод 1С1306У5) и регулировки цветового баланса (выводы IC1306/7,8,9) подаются на выводы 101301 /13,7,3,11 через согласующее усилители микросхемы IC1303.

Выходной сигнал регулировки контрастности используется также в схемах отключения видеосигнала и ограничения тока лучей кинескопа.

В схеме отключения видеосигнала цепь прохождения сигнала регулировки контрастности замыкается на общий провод ключом на транзисторе 01304 по команде VIDEO_OFF процессора управления IC901.

В схеме ограничения тока лучей кинескопа цепь прохождения сигнала регулировки контрастности шунтируется операционным усилителем, входящим в состав микросхемы IC351. Этот усилитель по сигналу ABL системы ОТ Л своим нижним открытым плечом замыкает на общий провод цепь регулировки контрастности через цепочку D1401, R1401, R1403.

Сигнал VIDEO_OFF отключения изображения с вывода IC901 /15 процессора управления кроме базы транзистора 01304 поступает также на схему переключения напряжения на модуляторе кинескопа (электрод G1), которая выполнена на транзисторах 0331,0333,0334. Ключевой каскад, реализованный на транзисторах 0333,0334, управляет режимом базы транзистора 0331. С делителя напряжения R305, R306, включенного в его коллекторную цепь, напряжение подается через резистор R381 и диод D383 в цепь электрода G1.

Когда транзистор 0331 заперт, в цепь электрода G1 из коллекторной цепи поступает запирающее напряжение порядка - 50 В, в этот момент кинескоп погашен. Если транзистор 0331 открыт, то на модуляторе имеется напряжение порядка - 20 В, и кинескоп включен. На модулятор G1 по цепи R380, С339 поступают также бланкирующие импульсы BLK, запирающиекинескоп на время обратного хода луча.

Импульсы горизонтальной и вертикальной либо комплексной синхронизации с 15-контактного разъема N103, расположенного на основной плате, проходят на выводы 6 и 8 микросхемы IC201 (M52346SP). Так как монитор может работать и с видеосигналом, в который подмешан синхросигнал, то сигнал зеленого цвета подается на вывод IC201/4 через цепочку R1005, С201.

В случае работы монитора с комплексным синхросигналом или с видеосигналом, в который подмешаны синхроимпульсы, микросхема IC201 функционирует как селектор синхроимпульсов.

Кроме того, микросхема IC201 определяет параметры A-F (период, длительность фронта, время задержки и т.д.) для импульсов горизонтальной и вертикальной разверток.

Выходными сигналами селектора являются импульсы запуска разверток (выводы 1С201Л3.14.15).

Сигналы идентификации режима формируются на выводах IC201Л 8,19 и поступают соответственно на выводы IC901 /47,48 процессора управления. Выделенные из видеосигнала бланкирующиe (маркирующее) импульсы используются для формирования импульсов гашения обратного хода луча, которые с вывода IC201 /17 подаются на вывод IC1301/14 видеопроцессора.

Управление режимом разделения комплексного синхросигнала на кадровые и строчные синхроимпульсы осуществляется подачей импульсов запуска вертикальной развертки с вывода IC201 /13 через инверторы на транзисторах Q250 - Q252 на вывод IC201 /10.

Питание микросхемы IC201 подается от цепи источника напряжения +15 В через стабилизатор с выходным напряжением +12 В, выполненный на микросхеме IC1304 (LM293ICM).

На плате кинескопа находится микросхема IC1305 (LSC4330), являющаяся формирователем сигналов служебной информации системы OSD.

Микросхема IC1305 преобразует код, поступающей на выводы IC1305/7,8, при наличии сигнала идентификации на выводе IC1305/6. Информационные и идентификационный сигналы подаются на выводы микросхемы IC1305 с соответствующих выводов процессора управления IC901.

Для синхронизации функционирования формирователя сигналов системы OSD используются импульсы обратного хода строчной (H_PULSE) и кадровой (V_PULSE) разверток, приходящие на выводы IC1305/5,10 через буферные каскады на транзисторах Q1302 и Q1301. Выходные сигналы системы OSD с выводов IC1305/15,14,13 через соответствующее диодные переключатели D1008, D1108, D1208 проходят на буферные каскады на транзисторах Q1002, Q1102. Q1202. На базу транзистора 01202 поступает также бланкирующий импульс OSDFB.

Сигналы основных цветов системы OSD с эмиттеров транзисторов Q1002,Q1102,Q1202 подаются далее на соответствующее входы оконечных усилителей видеосигналов, в ходящее в состав микросхемы IC1302.

Сигнал управления диодными переключателями D1008,01108. D1208 (OSD_SW) формируется на выводе IC1308/8 коммутатора.

Сигнал управления коммутатором (FBKG) подается с вывода IC1305/12 через буферный каскад на транзисторе Q1303 на выводы 101308/5,6,12,13.

Рис.3. Функциональная схема селектора видеосигналов и формирователя сигналов системы OSD

Рис. 4. Функциональная схема выходных каскадов тракта обработки видеосигналов.

Рис.5. Принципиальная схема тракта обработки видеосигналов

Функциональная схема системы управления. Принципиальная схема системы управления.

Основу узла управления составляет процессор IC901 (TVC80219-1E), который анализирует информацию, поступающую от компьютера и от кнопок, расположенных на передней панели монитора.

Процессор управления IC901 формирует сигналы запуска задающих генераторов вертикальной и горизонтальной развертки с привязкой их к синхроимпульсам, сигналы коррекции параметров растра, сигналы отключения при аварийных ситуациях и сигналы управления оперативными регулировками.

Процессор IC901 функционирует совместно с микросхемой памяти IC902 (X24LC08BTISN), с которой связан цифровой шиной (выводы IC901/62,64).

Синхронизация работы процессора IC901 осуществляется внутренним генератором, кварцевый резонатор которого Х901 подключен к выводам IC901/41,42.

При включении источника питания монитора формируется импульс RESET, который поступает на вывод IC901 /35.

Импульсы вертикальной и горизонтальной синхронизации (VS и HS) подаются на систему управления (выводы IC901/4.37) с соответствующих выходов селектора синхроимпульсов. Импульсы вертикальной синхронизации поступают на вывод IC901/37 через инвертор на транзисторе Q903, а импульсы горизонтальной синхронизации приходят на вывод IC901/4 через ограничительную цепь R908, С901, D902.

На выводы IC901 /47,48 процессора управления с детектора режима (выводы 1С201/18, 19) поступают сигналы выбора режима.

Если какой-либо параметр синхроимпульсов не соответствует определенному режиму, то процессор управления IC901 формирует на выводах IC901/10,11 сигналы HS_OFF и VS_OFF отключения синхроимпульсов, которые подаются на выводы IC501 /26.27 процессора разверток. Сигналы отключения воздействуют на ключи, выполненные на транзисторах О401, ©501 и шунтирующие цепи прохождения синхроимпульсов HS и VS. На выводах 10901/6,7,8 процессора управления формируются сигналы управления блоком питания.

Если параметры синхроимпульсов соответствуют выбранному режиму и видеосигнал активен, то процессор управления выдает сигнал ON включения блока питания.

Если горизонтальные синхроимпульсы отсутствуют или частота их следования меньше 6 кГц, то формируется сигнал STANDBV, переводящей блок питания в дежурный режим.

Если частота следования горизонтальных синхроимпульсов больше 10 кГц, но при этом вертикальные синхроимпульсы отсутствуют или их частота меньше 20 Гц, то процессор управления IC901 переводит блок питания в режим SUSPEND (временной приостановки функционирования).

В том случае, если синхроимпульсы отсутствуют или частота следования горизонтальных синхроимпульсов меньше 6 кГц, а вертикальных - меньше 20 Гц, процессор управления переводит блок питания в положение OFF (выключено).

При включении блока питания на выводе IC901/25 вырабатывается сигнал высокого логического уровня, который через ключ на транзисторе Q901 зажигает светодиод D940, светящейся зеленым светом. Во всех остальных режимах блока питания (STANDBV, SUSPEND, OFF) цвет свечения диода D940 желтый.

Выводы IC901 /27-30 процессора управления подключены к контактам клавиатуры управления. Если клавиши не нажаты, на контактах присутствует напряжение высокого логического уровня.

Нажатие одной из клавиш приводит к появлению на соответствующем выводе процессора управляющего сигнала низкого логического уровня.

При включении монитора на выводе IC901/1 формируется команда включения накала кинескопа (PSMJHEAT), а на выводе 10901/17 - команда выключения напряжения питания выходного каскада строчной развертки (H_B_OFF). После прогрева катодов команда H_B_OFF отключается.

С выводов 10901/49,50 снимаются команды переключения конденсаторов S-коррекции (C_SEL1 и C_SEL2).

На выводе 10901/53 процессора управления вырабатывается команда FH_SW переключения режима стабилизации напряжения Н. В при изменении частоты развертки. С выводов IC901Л 3,14 команды включения режима компенсации искажений типа "муар" поступают на выводы 1С462Л3.9 Синхронизация формирования этих команд осуществляется импульсами запуска строчной развертки HD, приходящими на вывод IC90115

процессора управления.

Для преобразования цифровых сигналов управления, снимаемых с выводов IC901/18-22, используются три микросхемы ЦАП (IC502, IC751 и IC1306), у которых тактовая линия CLC и линия данных DI являются общими. Идентификация сигналов осуществляется по адресной линии отдельно для каждой микросхемы ЦАП (LD-DAC1. LD-DAC2, LD-DAC3).

Отдельные порты процессора (выводы IC901/31-33) используются для передачи сигналов управления режимами работы тракта обработки аудиосигналов.

Рис.6. Функциональная схема системы управления

Рис.7. Принципиальная схема системы управления

Функциональная схема процессора разверток и выходного каскада кадровой развертки.

Принципиальная схема процессора разверток и выходного каскада кадровой развертки.

Осциллограммы сигналов в контрольных точках процессора разверток и выходного каскада кадровой развертки.

Формирование импульсов запуска горизонтальной и вертикальной разверток, а также сигналов коррекции растра в соответствии с установленным режимом обеспечивает процессор разверток, который выполнен на микросхеме IC501 (UPC1883).

Импульсы синхронизации VS и HS поступают на выводы IC501 /27,26 процессора разверток.

Сформированный пилообразный импульс запуска кадровой развертки с вывода 1С501Й процессора разверток через интегрирующую цепь R416, С421, D405, R415, С416 поступает на вход усилителя мощности (вывод 1С490Л), выполненного на микросхеме TDA9302H.

Коррекция временной задержки импульса запуска строчной развертки относительно синхроимпульса осуществляется аналоговым сигналом H_DU-TY, который с вывода IC502/3 через согласующий усилитель на микросхеме IC504 проходит на вывод IC501/23 микросхемы

Сигнал запуска строчной развертки с вывода IC501 /18 через защитный резистор R547 подается на затвор транзистора Q549. Нагрузкой транзистора Q549 является первичная обмотка трансформатора Т541.

Для улучшения формы импульса первичная обмотка трансформатора Т541 за шунтирована демпфирующей цепью D550, R549, а между стоком транзистора Q549 и общим проводом включен конденсатор С552.

Усиленный сигнал с делителя напряжения на резисторах R551, R552, R554, подключенного к вторичной обмотке трансформатора Т541, поступает на базу транзистора Q550. Для уменьшения выбросов между выходом делителя и выводом T541J9 вторичной обмотки включен демпфирующей диод D551.

Стабилизация амплитуды импульсов строчной развертки обеспечивается за счет питания каскада от источника напряжения +24 В через управляемый стабилизатор напряжения, выполненный на микросхеме IC550 (AN6531). Управляющий сигнал H_DRIVE_B приходит на микросхему IC550 с ЦАП системы управления (вывод 1С502Л2). Импульсы запуска каскадов строчной развертки используются также для синхронизации формирователя импульсов на микросхеме IC660 (TVS 1103).

Микросхема TVS 1103 является ШИМ-контроллером, формирующем импульсы для запуска усилителя на транзисторах Q672, Q674, Q675, Q676. Усилитель управляет ключевым транзистором Q680, где напряжение +183 В преобразуется в напряжение питания выходного каскада строчной развертки (Н_В). Кроме того, транзистор Q680 нагружен на трансформатор L681. вторичная обмотка которого вместе с выпрямителем на диодах D562, D563 вырабатывает напряжение для питания схемы центровки по горизонтали.

Микросхема IC660 изменяет напряжение Н_В в соответствии с выбранным режимом строчной развертки. Управляющей сигнал в цифровой форме формируется процессором управления IC901. преобразуется в аналоговый сигнал микросхемой ЦАП и с вывода IC1306Л 3 проходит на вывод IC660/2.

На вывод IC660/1 поступает сигнал DCP датчика перегрузки. При увеличении тока потребления выходного каскада строчной развертки сверх допустимой величины микросхема IC660 отключает цепь питания Н_В.

Напряжение Н_В может быть отключено также по команде системы управления. При этом управляющей сигнал высокого логического уровня с вывода IC901 /15 процессора управления подается на базу транзистора 0873. который открывается и шунтирует выход ШИМ-сигнала с вывода ICS80/6.

Напряжение Н_В также отключается, если напряжение в линии +12 В падает ниже допустимого предела. В этом случае открывается транзистор 0883 и также шунтирует вывод IC680/6.

Рис.8. Функциональная схема процессора разверток и выходного каскада кадровой развертки.

Рис.9. Принципиальная схема процессора разверток и выходного каскада кадровой развертки.

Рис.10 Осциллограммы сигналов в контрольных точках процессора разверток и выходного каскада кадровой развертки.

Функциональная схема процессора разверток и выходного каскада кадровой развертки

Принципиальная схема процессора разверток и выходного каскада кадровой развертки

Сформированный пилообразный импульс запуска кадровой развертки с вывода 1С501Й процессора разверток через интегрирующую цепь R416, С421. D405, R415, С416 проходит на вход усилителя мощности (вывод 1С490Л), выполненного на микросхеме TDA9302H.

С выводов 1С501Л1Д4 процессора разверток подается опорное напряжение, которое с делителя R405, R426 поступает на второй вход усилителя (вывод IC49077).

Нагрузкой усилителя мощности являются кадровые отклоняющие катушки, включенные последовательно с конденсатором С412 и резистором R423.

Цепь R427, С409 предотвращает возбуждение усилителя на высоких частотах. Включенные параллельно отклоняющем катушкам конденсатор С411 и резистор R422 выравнивают импеданс нагрузки усилителя.

Питание усилителя мощности осуществляется от источника напряжения +33 В. Напряжение подается через фильтр R429, С408 на вывод IC49072.

Усилитель охвачен отрицательной обратной связью с резистора R423 на вывод IC49071 через uenbR418,C415.

В первую половину прямого хода от верхнего края до середины растра кадровый отклоняющий ток протекает по цепи: источник питания +33 В - диод D401. вывод 1С490У6 - верхнее плечо усилителя мощности - вывод IC490/5 - кадровые отклоняющие катушки - разделительный конденсатор С412 - резистор R423. При этом конденсатор С412 заряжается.

Во время прямого хода кадровой развертки от середины до нижнего края растра конденсатор С412 разряжается по цепи: положительный вывод конденсатора С412 - кадровые отклоняющие катушки - вывод IC490/5 - нижнее плечо усилителя мощности - общий провод - резистор R423 - отрицательный вывод конденсатора С412.

Для сокращения времени обратного хода кадровой развертки усилитель мощности запитывается на этот период от схемы вольтодобавки с элементами D401. С407, D402. Во время прямого хода лучей конденсатор С407 заряжается от источника +33 В, а во время обратного хода внутренний ключ микросхемы IC490 подключает конденсатор С407 последовательно с напряжением источника питания, при этом диод D401 закрывается, и на выводе IC490/3 микросхемы формируется импульс напряжения, почти равный удвоенному напряжению питания.

Импульс обратного хода через резистор R428 поступает в систему управления монитора.

Центровка растра осуществляется подачей постоянного тока от источника +33 В в цепь отклоняющих катушек через управляемый делитель, образованный проводимостями транзисторов 0494,0495. Управляющее напряжение V_POSI подается в цепь базы транзистора 0494 с вывода IC502/4 через согласующий усилитель, выполненный на микросхеме IC401 (LM358M).

Напряжение V_SAWTOOTH, выделенное на резисторе R423, используется для формирования сигналов параболической коррекции.

Микросхема IC501 вырабатывает также бланкирующие (маркирующие) импульсы, которые с вывода IC501/29 передаются на усилитель-формирователь, выполненный на транзисторах О307 - О309. Бланкирующие импульсы с коллектора транзистора О309 поступают в цепь модулятора кинескопа (электрод G1).

Рис.11. Функциональная схема процессора разверток и выходного каскада кадровой развертки.

Рис.12. Принципиальная схема процессора разверток и выходного каскада кадровой развертки

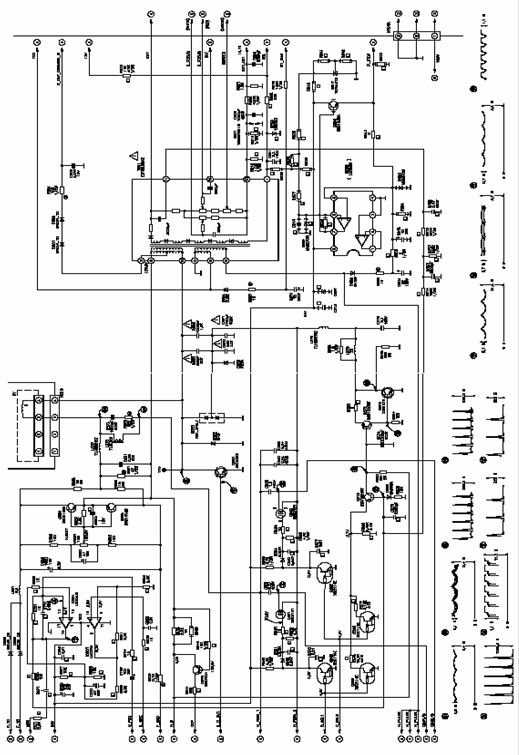

Функциональная схема выходного каскада строчной развертки и источника высокого напряжения

Принципиальная схема выходного каскада строчной развертки и источника высокого напряжения

Выходной каскад строчной развертки выполнен на мощном ключевом транзисторе Q550 и демпферных диодах D552, D555, D560. Нагрузкой выходного каскада служат строчные отклоняющее катушки, один вывод которых подключен к коллектору транзистора Q550, а второй через конденсаторы С563, С565 и С561 (С562) - к схеме диодного модулятора. Указанные конденсаторы, суммарную емкость которых обозначим Ср, кроме гальванической развязки строчных катушек осуществляют S-коррекцию отклоняющего тока.

Диод D555, состоящий из двух соединенных последовательно диодов, и диод D560 являются частью диодного модулятора.

Питание выходного каскада осуществляется по дроссельной схеме, где в качестве дросселя используется первичная обмотка выходного строчного трансформатора Т601.

В первую половину прямого хода лучей магнитная энергия, накопленная в строчных отклоняющих катушках во время предыдущего цикла, создает отклоняющий ток, перемещающий луч от левого края растра к его середине. Этот ток протекает по цепи: строчные отклоняющие катушки - линеаризующая цепь L573, С573, R575 - конденсаторы Ср - верхний по схеме диод сборки D555 - строчные отклоняющие катушки.

В момент подхода лучей к середине растра, когда отклоняющий ток уменьшается до нуля, на базу ключевого транзистора Q550 с вторичной обмотки трансформатора Т541 поступает импульс положительной полярности, открывающий транзистор.

При этом начинает формироваться ток отклонения второй половины прямого хода, перемещающий лучи кинескопа от середины до правого края растра. Ток протекает по цепи: строчные отклоняющие катушки - открытый транзистор Q550 - общий провод - нижний по схеме диод сборки D555 и соединенный с ним параллельно диод D560 - конденсаторы Ср - линеаризующая цепь L575, С573, R575 - строчные отклоняющие катушки.

В момент прихода лучей к правому краю растра транзистор Q550 закрывается отрицательным перепадом базового тока. На коллекторе транзистора возникает положительный импульс напряжения, длительность которого определяется количеством энергии, запасенной в контуре, образованном индуктивностью строчных отклоняющих катушек и конденсаторами Ср. Этот импульс вызывает изменение полярности отклоняющего тока в строчных катушках, что ведет к быстрому перемещению лучей от правого края к левому, то есть к их обратному ходу. Длительность импульса обратного хода определяется эквивалентной емкостью конденсаторов С555, С556, С570, С571.

Коррекция геометрических искажений растра осуществляется с помощью схемы диодного модулятора. Изменение величины отклоняющего тока происходит за счет управления током разряда конденсаторов С570, С571 с помощью изменения проводимости транзистора Q573 по параболическому закону. Транзистор Q573 подключен параллельно конденсаторам С570, С571 через элементы L570, L578, R595.

Кроме коррекции геометрических искажений изменением проводимости транзистора Q573 регулируется размер растра по горизонтали.

Сигнал вертикальной параболической коррекции (V_PCC) с вывода IC501 /10 подается на каскад, выполненный на микросхеме IC601 (LM324M).

В этом узле сигнал коррекции смешивается с сигналом регулировки размера по горизонтали (H_SIZE), который формируется на выводе 1С1306Л9.

Полученный в результате суммирования комплексный сигнал приходит на усилитель сигнала коррекции, выполненный на транзисторах Q574, Q572, Q573. Кроме того, сигнал вертикальной параболической коррекции через цепочку R671, С671 поступает на узел контроля параметров коррекции (вывод IC660/2).

Сигнал горизонтальной параболической коррекции формируется на обмотке трансформатора Т351 и с делителей, образованных конденсаторами С381 - С386, передается на конденсаторы С561, С562.

При изменении частоты развертки командами C_SEL1 и C_SEL2 ступенчато изменяются параметры S-коррекции, что достигается подключением параллельно конденсаторам С563, С565 дополнительного конденсатора С561 либо С562. Подключение осуществляется идентичными ключевыми схемами, выполненными на транзисторах Q560, Q561 и Q562. Q563.

Одновременно сигналами C_SEL1 и C_SEL2 ступенчато изменяется коэффициент усиления усилителя на транзисторах Q574,0572. Q573 за счет изменения величины сопротивления в цепи эмиттера транзистора Q574, которое достигается с помотаю ключей на транзисторах 0568.0569.

Центровка изображения по горизонтали осуществляется с помощью мостовой схемы, образованной транзисторами 0564,0585 и резисторами R588, R589.

Строчные отклоняющее катушки включены в диагональ мостовой схемы последовательно с первичной обмоткой строчного трансформатора Т601. В другую диагональ мостовой схемы подается напряжение питания от выпрямителя на диодах D562, D563. Выпрямитель не имеет гальванической связи с общим проводом монитора. Регулировкой резистора VR584 осуществляется разбалансировка моста, в результате чего меняются величина и направление постоянной составляющей тока, протекающего через строчные отклоняющие катушки.

В цепи питания выходного каскада строчной развертки находится датчик максимального тока, выполненный на резисторах R535, R539. При превышении предельно допустимого тока потребления падение напряжения на резисторах R535, R539 становится достаточным для открывания транзистора Q575. Транзистор открывается, и на его коллекторе вырабатывается сигнал ОСР аварийного отключения строчной развертки.

С части витков первичной обмотки строчного трансформатора (вывод Т601/2) снимается переменное напряжение, из которого диодами D601, D602, резистором R601 и конденсатором С605 формируется напряжение питания системы размагничивания кинескопа (V_DAF_DEGAUSS_B).

Из напряжения, снимаемого с вывода Т601Д5 вторичной обмотки, вырабатывается отрицательное напряжение смещения модулятора (G1J31AS).

Рис.13. Функциональная схема выходного каскада строчной развертки и источника высокого напряжения.

Рис.14. Принципиальная схема выходного каскада строчной развертки и источника высокого напряжения

Функциональная схема выходного каскада строчной развертки и источника высокого напряжения

Принципиальная схема выходного каскада строчной развертки и источника высокого напряжения

Трансформатор Т601 формирует напряжения анода (ЕНТ), статической фокусировки (S_FO-CUS), а также напряжение ускоряющего электрода (SCREEN) кинескопа.

Умножитель напряжения, входящей в состав трансформатора Т601. подключен к общему проводу через конденсатор С601. резисторы R622, R623, а также внутреннее сопротивление источника +12 В. Отрицательное напряжение, выделившееся на конденсаторе С601, суммируется с напряжением источника +12 В. Суммарное напряжение ABL пропорционально току лучей кинескопа и используется в схеме ограничения тока лучей.

На вывод Т601Л 4 трансформатора поступает напряжение параболической формы с коллектора транзистора Q319, которое суммируется с постоянным напряжением и используется для формирования сигнала динамической фокусировки (D_FOCUS).

Контроль высокого напряжения ЕНТ осуществляется напряжением, полученным с делителя, верхнее плечо которого образуют резисторы, входящие в состав трансформатора Т601, а нижнее плечо - резисторы R618 - R621. С делителя снимается напряжение EHT_DET, которое пропорционально высокому напряжению и используется в системе аварийного отключения высокого напряжения.

Флуктуации высокого напряжения с вывода Т601/11 поступают на делитель, образованный элементами R612 - R614, С602, С603. Выделенная постоянная составляющая поступает в базу транзистора Q574. Таким образом осуществляется стабилизация размера растра при изменениях высокого напряжения.

С вторичной обмотки (вывод Т801/5) снимаются импульсы обратного хода лучей (H_PUI. SE). которые выпрямляются диодом D608 и используются для синхронизации функционирования систем монитора.

Выпрямленное напряжение приходит на вход компаратора, выполненного на микросхеме IC602, и используется для формирования напряжения P_STOP аварийного отключения монитора. Опорное напряжение компаратора вырабатывается из напряжения ABL. При увеличении напряжения ABL (аварийный режим) опорное напряжение уменьшается, при этом выходное напряжение компаратора возрастает и открывает транзистор Q603. С эмиттера транзистора поступает сигнал P_STOP аварийного отключения монитора.

Аналогично компаратор функционирует и при увеличении выпрямленного напряжения с вывода Т601У5 трансформатора.

Рис.14. Функциональная схема выходного каскада строчной развертки и источника высокого напряжения.

Рис.15. Принципиальная схема выходного каскада строчной развертки и источника высокого напряжения.

Принципиальная схема блока формирования напряжения динамической фокусировки, узла поворота растра и узла размагничивания кинескопа монитора VIEWSONIC 17GA/GL приведена ниже.

Принципиальная схема блока.

Формирования напряжения динамической.

Фокусировки кинескопа.

Импульсы динамической фокусировки (DAF) формируются посредством суммирования напряжений параболической коррекции строчной развертки, выделенных на вторичной обмотке трансформатора Т351. и напряжения параболической формы, сформированного из пилообразного напряжения вертикальной развертки (V_SAWTOOTH).

Пилообразное напряжение V_SAWTOOTH поступает на вывод 2 микросхемы IC302 (TDA8145) усилителя-формирователя. Выходное напряжение параболической формы с вывода 1С302/?, через эмиттерный повторитель на транзисторе Q303 проходит на базу транзистора Q319.

В коллекторной цепи транзистора Q319 суммируются напряжения параболической формы строчной и кадровой частот. Результирующее напряжение DAF приходит на вывод Т601 /14 трансформатора, где преобразуется в напряжение динамической фокусировки D_FOCUS.

Рис. 16. Принципиальная схема блока Формирования напряжения динамической Фокусировки кинескопа.

Функциональная схема узла поворота растра.

Принципиальная схема блока формирования напряжения динамической фокусировки, узла поворота растра и узла размагничивания кинескопа монитора VIEWSONIC 17GA/GL приведена ниже.

Принципиальная схема блока Формирования напряжения динамической Фокусировки кинескопа

Сигнал Z_AXIS управления углом поворота растра с вывода IC751 /13 поступает на согласующее усилители-формирователи микросхемы IC101 (LM324M), представляющей собой четыре операционных усилителя.

В одном из операционных усилителей сигнал инвертируется. Прямой и инверсный сигналы подаются на усилители мощности, выполненные на двуполярных эмиттерных повторителях (Q101,0102 и 0103,0104). Усилители мощности нагружены на катушку TILT_COIL коррекции угла наклона растра.

Катушка TILT_C0IL расположена на горловине кинескопа и позволяет поворачивать изображение в пределах нескольких градусов относительно горизонтальной оси.

Питание операционных усилителей осуществляется напряжением +12 В (вывод IC101 /4).

Питание усилителя мощности узла поворота растра обеспечивается от цепи питания накала кинескопа.

Рис.17. Функциональная схема узла поворота растра.

Рис.18. Принципиальная схема блока Формирования напряжения динамической Фокусировки кинескопа

Принципиальная схема блока формирования напряжения динамической фокусировки, узла поворота растра и узла разнагничивания кинескопа монитора VIEWSONIC 17GA/GL приведена ниже.

Принципиальная схема блока Формирования напряжения динамической Фокусировки кинескопа

Размагничивание кинескопа осуществляется за счет разряда конденсатора С890 через катушку размагничивания DEGAUSSING_COIL.

Катушка размагничивания вместе с конденсатором С896 и резистором R898 образуют колебательный контур, в котором возбуждаются затухающе

колебания. Возникающее при этом знакопеременное магнитное поле размагничивает металлические детали кинескопа.

Заряд конденсатора С890 осуществляется от делителя напряжения R899, R891. R892, R893, R897, R900. Разрядным ключом является симистор D891. управляющей электрод которого коммутируется транзистором Q

891.

Команда включения узла размагничивания DEGAUSS поступает с вывода IC901/39 процессора управления на базу транзистора Q891.

Рис.4.13. Принципиальная схема блока Формирования напряжения динамической Фокусировки кинескопа

Функциональная схема источника питания. Принципиальная схема источника питания.

Источник питания содержит помехоподавляющий фильтр, выпрямитель сетевого напряжения, импульсный преобразователь напряжения, выполненный на микросхеме IC820 и импульсном трансформаторе, а также выпрямители вторичных импульсных напряжений.

Принцип работы источника заключается в преобразовании выпрямленного сетевого напряжения в импульсное напряжение прямоугольной формы с изменяющейся в зависимости от нагрузки скважностью, с последующей трансформацией и выпрямлением этого напряжения во вторичных цепях.

Сетевое напряжение через предохранитель и двух-звенный сетевой помехоподавляющий фильтр, образованный элементами D801, R801, С801, L801, С802, С803, С805 - С808, L802, подается на диодный мост D808. Между первым и вторым звеньями сетевого фильтра находятся контакты выключателя сетевого питания SW801.

Выпрямленное напряжение сглаживается конденсаторами С814, С815 и через первичную обмотку трансформатора Т801 (выводы Т801Л-6) поступает на ключевой каскад, выполненный на высоковольтном транзисторе, который входит в состав микросхемы IC820 (STRS6533).

Микросхема IC820 является ШИМ-контроллером со встроенным силовым ключом. Контроллер вырабатывает сигнал управления ключевым транзистором, а также сигнал запирания формирователя сигнала управления в режиме ограничения максимального тока, защиты от перенапряжений или защиты от перегрева. Выключение преобразователя может осуществляться также внешним сигналом, подаваемым на вывод IC820/9.

Микросхема IC820 обеспечивает работу преобразователя в режиме стабилизации выходных напряжений при изменении сетевого напряжения или изменения нагрузки. Для этого в ее состав входят генератор пилообразного напряжения и схема сравнения порогового уровня. Эталонное напряжение сравнивается с напряжением обратной связи, в качестве которого используется напряжение питания, поступающее на вывод IC820/4. Изменяя длительность импульса на затворе силового ключа преобразователя, можно изменять количество запасенной в импульсном трансформаторе энергии, а значит и напряжения на выходах вторичных выпрямителей.

Цепь запуска содержит резисторы R811, R812, через которые выпрямленное сетевое напряжение приходит на вход запуска (вывод IC820J8). При этом напряжение питания слаботочных каскадов микросхемы обеспечивается напряжением, поступающем на вывод IC820/4 от параметрического стабилизатора на транзисторе Q820. После выхода источника питания рабочий режим питание микросхемы осуществляется от обмотки 8-9 обратной связи, напряжение которой выпрямляется диодом D807 и сглаживается конденсатором С829, а затем подается на вывод IC820/4.

Кроме указанной цепи стабилизации питающего напряжения используется также цепь стабилизации, анализирующая напряжение одной из вторичных обмоток (обмотка S2), выпрямленное напряжение +105 В которой через делитель R889, VR801, R888 проходит на узел сравнения, выполненный на транзисторе ©303. Коллектор транзистора Q803 через диод оптопары РС830 и резистор R850 подключен к источнику напряжения +35 В. Выделенный на коллекторе транзистора ©303 сигнал ошибки через оптопару подается на вход схемы стабилизации (вывод IC820/7).

Для уменьшения наводок частота переключений преобразователя синхронизируется с частотой развертки монитора, для чего импульсы обратного хода строчной развертки с вывода Т601/5 строчного трансформатора поступают через развязывающую оптопару РС832 на вход схемы синхронизации (вывод IC820/5).

Для обеспечения стабильной и безопасной работы предусмотрено несколько цепей ограничения и зашиты от перегрузок и перенапряжения.

В цепи стока силового ключа находится датчик тока (резистор R834), импульсная составляющая падения напряжения на котором управляет проводимостью транзистора ©825, включенного в цепь отрицательной обратной связи по току с вывода IC820/2 на вывод IC820/6. При увеличении среднего тока силового ключа сверх допустимого значения транзистор ©824 открывается и шунтирует цепь запуска микросхемы IC820.

При увеличении сверх допустимого предела напряжения питания, приходящего на вывод IC820/4, пробивается стабилитрон D810 и на вывод 1С820Я поступает напряжение остановки преобразователя.

На вывод IC820J9 сигнал остановки преобразователя может подаваться и от датчика перегрузки по току источника напряжения +183 В с резистора R890 через оптопару РС831, а также при превышении напряжений в цепях +15 В и накала кинескопа, контролируемых стабилитронами D871 и D846, через базовую цепь транзистора Q822. Датчик тока на резисторе R854 контролирует превышение максимального тока источника напряжения +100 В. Резистор R854 включен в базовую цепь транзистора ©80S. который при перегрузке по току открывается и через делитель подключает источник +100 В к базовой цепи транзистора 0822.

В базовую цепь транзистора G822 поступает также сигнал положительной полярности при неисправности строчной развертки или при увеличении сверх допустимого значения тока лучей кинескопа.

Во всех перечисленных случаях открываются транзистор G822 и диод оптопары РС831. Выходной сигнал оптопары поступает на вход остановки преобразователя (вывод IC820J9).

Из переменного напряжения, снимаемого со вторичной обмотки S1 (вывод Т801/10), формируется напряжение +183 В для схемы динамической коррекции горизонтальной развертки.

Из напряжения обмотки S2 (вывод Т801/11) вырабатывается напряжение +105 В, которое через ключ дежурного режима на транзисторе Q801 поступает в схему строчной развертки.

Из напряжения обмотки S3 (вывод Т801Л 2) формируется напряжение + 35 В, которое используется для разблокирования ключа на транзисторе ©801.

Из напряжения +35 В стабилизаторами на микросхемах IC873 и IC870 вырабатываются напряжения +33 В и +24 В. Включение стабилизатора IC873 производится ключом на транзисторе Q812 при поступлении сигнала SUSPEND.

Из переменного напряжения, снимаемого со вторичной обмотки S4 (вывод Т801/13), формируется напряжение +15 В, из которого затем стабилизаторами на микросхемах IC871 и IC876 вырабатываются напряжения +12 В и +5 В. Микросхема IC871 выключается ключом на транзисторе Q813 при поступлении сигнала POWER_OFF.

Микросхема IC876 кроме стабилизации напряжения +5 В вырабатывает также импульс RESET (вывод IC876/4), который поступает на вывод IC901/35 процессора управления. Импульс RESET формируется как при включении питания монитора, так и при выключении, что обеспечивает сохранение оперативной информации, введенной в память процессора управления IC901, и установку его программы в начало цикла.

Обмотка S5 (вывод Т801Л6) используется для формирования напряжения +8 В, из которого стабилизатором на микросхеме IC877 вырабатывается напряжение накала кинескопа. Стабилизатор IC877 включается ключом на транзисторе Q814 при поступлении сигнала PSMHEAT

При поступлении сигнала STAND_BY ключ на транзисторе Q811 шунтирует базовую цепь транзистора Q809, изменяя потенциал на входе регулировки напряжения стабилизатора (вывод IC877/4). При этом напряжение накала уменьшается приблизительно на 30%.

Обмотка S6 (выводы Т801 л 7,18) используется для формирования напряжения питания блока обработки аудиосигналов. Выпрямленное напряжение подается на стабилизатор IC875. Выходное напряжение стабилизатора (вывод IC875/3) коммутируется ключом на транзисторе Q816 при поступлении команды SUSPEND.

Принципиальная схема усилителя сигналов емкостного датчика.

Рис. 19. Функциональная схема источника питания.

Рис. 20. Принципиальная схема источника питания.

Рис.21. Принципиальная схема усилителя сигналов емкостного датчика

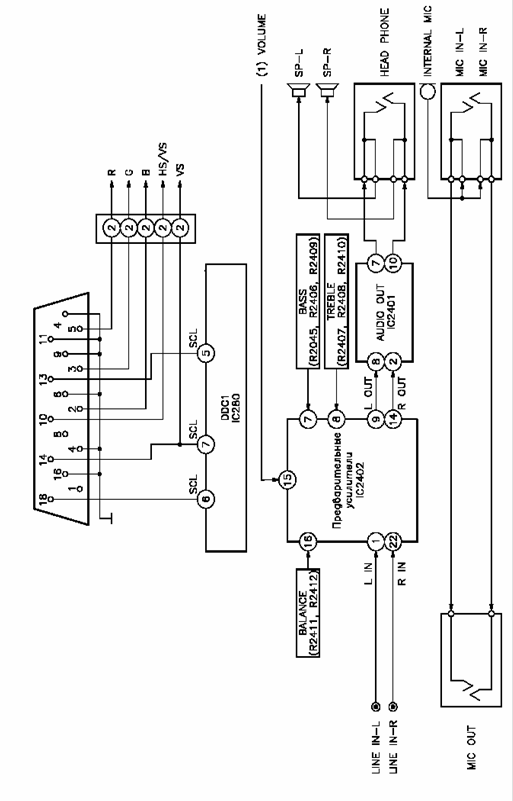

Функциональная схема блока обработки аудиосигналов. Принципиальная схема блока обработки аудиосигналов.

Каскады блока обработки аудиосигналов расположены на отдельной плате.

В состав блока входят двухканальный предварительный усилитель, выполненный на микросхеме IC2402 (CXA1279AS), а также двухканальный выходной усилитель на микросхеме IC2401 (LA4270), нагруженный на громкоговорители или головные телефоны.

Звуковые сигналы с входного разъема JK2004 через делители R2401, R2402, R2403, R2404 и разделительные конденсаторы С2401. С2402 проходят на входы предварительных усилителей (выводы 1С2402Л,22).

Микросхема IC2402 содержит два идентичных усилителя. Схемотехника микросхемы CXA1279AS обеспечивает одновременную регулировку громкости, тембра и баланса в обоих каналах.

Регулировка усиления осуществляется управляющем напряжением VOLUME, поступающем на вывод 1С2402Л6 с вывода IC751/7.

Для регулировки громкости и выключения звука служат клавиши SW905 - SW907 (DOWN, UP и MUTE), выходные сигналы с которых подаются на выводы IC901/31,32,33 процессора управления.

При включении режима MUTE (выключение звука) загорается светодиод D941, на который поступает потенциал высокого логического уровня через ключевой транзистор Q904, управляемый сигналом с вывода IC901/26 процессора управления.

Регулировки тембра фиксированы. На вывод 1С2402ЛЗ подается напряжение с делителя R2407, R2408, определяющее частотную характеристику усилителей в области верхних звуковых частот, а на вывод IC2402/7 поступает напряжение с делителя R2405, R2406, определяющее частотную характеристику усилителей в области нижних частот.

На вход схемы регулировки баланса (вывод 1С2402Л5) подается постоянное напряжение с делителя R2411, R2412, при этом баланс усиления обоих каналов не регулируется.

Устойчивость работы предварительных усилителей определяется внутренними фильтрами верхних и нижних звуковых частот. Внешние элементы указанных фильтров (конденсаторы С2403, С2404, С2407, С2408) подключены соответственно к выводам IC2402/5.6.18.17.

Усиленные звуковые сигналы поступают с выводов 1С2402Й.14 через разделительные конденсаторы С2306, С2304 и ФНЧ (R2302, С2302 и R2301, С2301) на соответствующее входы двухканального усилителя мощности НЧ (выводы IC2401/2.5).

Через разделительные конденсаторы С2308, С2311 и систему фильтров к выходам усилителей мощности (выводы 1С2401/7. Ю) подключена нагрузка - малогабаритные звуковые колонки сопротивлением 8 Ом.

RC-цепочки С2309, R2303 и С2310, R2304 предотвращают возбуждение усилителей мощности на высоких частотах.

Через разъем JK2002 к выходам усилителей мощности могут быть подключены головные телефоны. При этом звуковые колонки автоматически отключаются. Выходная мощность на головных телефонах ограничивается включенными последовательно резисторами R2305, R2306.

Отдельные каскады блока обработки аудиосигналов обеспечивают также питание входящего в его состав электретного микрофона, которое осуществляется через ограничительный резистор R2416.

Через разъем JK2001 к блоку обработки аудиосигналов может быть подключен внешний микрофон, при этом внутренний автоматически отключается.

Выходной сигнал микрофонов выводится из блока обработки аудиосигналов через разъем JK2003.

Питание каскадов блока обработки аудиосигналов осуществляется от цепи AUDIO_B.

Рис. 22. Функциональная схема блока обработки аудиосигналов.

Рис.23. Принципиальная схема блока обработки аудиосигналов.

Рассмотрим логический анализатор, имеющий в своем составе многоразрядное буферное ОЗУ с узлами управления и синхронизации.

Логический анализатор по своему назначению близок к осциллографу, так как он позволяет наблюдать на экране временные диаграммы сигналов. Но в отличие от обычного (не цифрового) осциллографа логический анализатор работает только с цифровыми двухуровневыми (реже трехуровневыми) сигналами, имеет большое количество входных линий (обычно от 16 до 64), работает в режиме однократного запоминания временных диаграмм (как запоминающий осциллограф) и имеет возможность предпусковой регистрации. Последнее требует некоторых пояснений (рис.1).

В отличие от обычных осциллографов, в которых развертывание формы входного сигнала начинается в момент запуска (то есть прихода внешнего сигнала запуска или превышения входным сигналом заданного уровня напряжения), здесь точка запуска может быть и в начале, и в середине, и в конце окна регистрации. Под запуском здесь понимается временная привязка процесса регистрации к исследуемому процессу. Запуском может служить, например, появление в потоке данных заданного кода или переход (фронт) на одной из входных линий. В этом случае оператор может видеть не только то, что происходило после запуска (как в случае с обычным осциллографом), но и то, что происходило до него.

Логические анализаторы делятся на синхронные (или анализаторы логических состояний) и асинхронные (или анализаторы временных диаграмм). Синхронные анализаторы работают от тактового генератора исследуемой схемы и фиксируют только временные сдвиги, кратные его периоду, а следовательно, выявляют только нарушения в логике работы схемы. Асинхронные анализаторы работают от собственного внутреннего тактового генератора, поэтому они измеряют абсолютные значения временных сдвигов и могут выявлять ошибки из-за неправильно рассчитанных задержек, из-за емкостных эффектов и т.д.

Рис.1. Предпусковая регистрация.

Они обычно делаются гораздо более быстрыми, чем синхронные анализаторы (рассчитываются на предельно возможную частоту регистрации).

Мы в качестве примера будем разрабатывать схему логического анализатора, не отличающуюся рекордными характеристиками ни в плане быстродействия, ни в плане количества разрядов, ни в плане развитости системы запуска. Достоинство ее в другом: она выполняется в виде платы расширения персонального компьютера, и, следовательно, при ее использовании оператор получает в свое распоряжение всю мощь этого компьютера: интеллект, средства ввода и отображения информации, дисковую память и т.д. В результате ценой незначительных дополнительных затрат (цена платы) мы можем превратить компьютер (на время или навсегда) в эффективный и очень удобный логический анализатор.

Исходные данные для проектирования примем следующие: количество входных линий (каналов регистрации) - 32, количество регистрируемых состояний - 4096, максимальная тактовая частота - 10 МГц, тактовый генератор - внутренний с изменяемой частотой или внешний, запуск - по положительному или отрицательному переходу на одной из 8 входных линий, глубина предпусковой регистрации - задается программно.

Первый этап проектирования в соответствии с описанным алгоритмом - предварительная оценка интерфейсной части. Прежде всего посмотрим, какие режимы обмена с магистралью нужны в данном случае. Для обеспечения нужного темпа приема данных (до 10 МГц) совершенно необходимо буферное ОЗУ, обмен с которым должен быть периодическим: при регистрации оно заполняется в темпе тактового генератора, по окончании регистрации его содержимое считывается компьютером. Нужно ли максимально ускорять этот процесс считывания? Зарегистрированная информация должна обрабатываться и отображаться на экране с целью анализа ее оператором. Этот процесс неизмеримо более длительный, чем перекачка информации из буферного ОЗУ в системное ОЗУ компьютера. Поэтому в данном случае особой скорости обмена, по-видимому, не требуется. Конечно же, можно организовать 16-разрядный обмен с нашим УС, дающий большой выигрыш во времени по сравнению с 8-разрядным обменом, но зато он требует дополнительных аппаратурных затрат (вдвое больше буферов данных, формирование сигнала - I/O CS 16). К тому же в этом случае усложняется проектирование печатной платы (нужен второй магистральный разъем). Исходя из всех этих соображений, имеет смысл остановиться на 8-разрядном обмене и отказаться от использования ПДП.

Что касается прерываний, то для логического анализатора их использование очень желательно, если не необходимо. Ведь между началом регистрации и ее окончанием, связанным исключительно с приходом запуска, может пройти довольно большое время. Целесообразно предусмотреть возможность выполнения в этот период компьютером других задач. Поэтому прерывание по окончании регистрации мы будем формировать, что, впрочем, не исключает необходимости чтения флага готовности.

Таким образом, интерфейсная часть нашего одноплатного анализатора должна обеспечивать следующие параметры. Количество адресов УС в адресном пространстве устройств ввода/вывода - 5, из которых четыре используются для чтения зарегистрированных данных, а один - для чтения флага готовности. Для записи управляющего слова будем использовать два из этих пяти адресов (надо записать глубину предпусковой регистрации, код выбора тактовой частоты, код выбора запуска). Используем одно прерывание по окончании регистрации. Как видим, ничего сложного здесь нет, поэтому к интерфейсной части мы не возвращаемся.

Переходим к операционной части. Основные ее узлы: буферное ОЗУ объемом 128 Кбит с организацией 4К х 32, счетчик для перебора адресов, внутренний тактовый генератор с программно изменяемой частотой, схема запуска и входные буфера для регистрируемых сигналов.

ОЗУ целесообразно выполнить на многоразрядных микросхемах (для снижения количества корпусов). Требования к его быстродействию в данном случае невысоки (при максимальной тактовой частоте 10 МГц в течение 100 не необходимо переключить счетчик адресов и записать входную информацию в ОЗУ). Таких микросхем, особенно зарубежного производства, достаточно много.

От счетчика требуется максимальное быстродействие (можно взять, например, микросхемы КР531ИЕ17, которые достаточно легко каскадируются без потери быстродействия). Кроме простого перебора адресов счетчик должен также обеспечивать предпусковую регистрацию. Остановимся на этом несколько подробнее. Для того чтобы реализовать предпусковую регистрацию, необходимо до прихода запуска непрерывно переписывать содержимое буферного ОЗУ по кругу (рис.2). Если мы выбираем глубину предпусковой регистрации N тактов, то надо остановить регистрацию через (4096 - N) тактов после прихода запуска. Затем надо считывать содержимое ОЗУ, начиная с точки остановки с перебором адресов в том же направлении, что и при регистрации. Проведя 4096 операций чтения содержимого ОЗУ, мы получим N тактов до запуска и (4096 - N) тактов после запуска, то есть моменту прихода запуска будет соответствовать адрес ОЗУ, считанный N-ым.

Рис.2. Реализация предпусковой регистрации.

Однако все произойдет именно так только в том случае, если от момента начала регистрации до момента прихода запуска наш анализатор успеет зафиксировать N тактов. Иначе мы не перепишем все ОЗУ, и в части его адресов будет находиться предыдущая информация. Чтобы избежать этого, надо запретить реакцию на запуск в течение N тактов после начала регистрации (выдержать своеобразное "мертвое" время). А что будет, если запуск придет в течение этого "мертвого" времени? Если исследуемый процесс периодический, то анализатор среагирует на следующий запуск. Если же процесс однократный, то надо начать процесс регистрации заведомо

раньше (на "мертвое" время или больше), чем начнется изучаемый процесс (например, если мы исследуем старт компьютера при включении питания).

В результате счетчики анализатора должны обеспечивать временную диаграмму, показанную на рис.3. Адреса ОЗУ начинают перебираться с началом регистрации. В течение N тактов после начала регистрации запуск запрещен. Через (4096 - N) тактов после прихода запуска регистрация прекращается.

Рис.3. Временная диаграмма работы счетчиков логического анализатора.

Точно так же может быть реализована предпусковая регистрация в цифровом осциллографе, который, кстати, тоже можно выполнить в виде одноплатного УС, сопрягаемого с системной магистралью. По сравнению с логическим анализатором в схему надо будет добавить одно или несколько АЦП и некоторые другие цифро-аналоговые узлы.