Задание на курсовое проектирование

Тема: Основы проектирования интегральных микросхем широкополосного усилителя

Срок представления проекта к защите –

Исходные данные для проектирования

Схема электрическая принципиальная, таблица электрических параметров элементов усилителя

Содержание пояснительной записки курсового проекта:

Выбор физической структуры полупроводниковой ИМС на БП-транзисторах

Расчёт геометрических размеров элементов ИМС

Разработка эскиза топологии ИМС широкополосного усилителя

Перечень графического материала:

Эскиз топологии ИМС широкополосного усилителя

Руководитель проекта _________________________

Задание принял к исполнению ________________________

Реферат

Пояснительная записка содержит 30 страниц, 3 рисунка, 4 использованных источников, 1 приложение.

Перчень ключевых слов: принципиальная схема, широкополосный усилитель, расчет геометрических размеров, эскиз топологии.

Объект разработки: топология ИМС широкополосного усилителя.

Цель работы: расчет геометрических размеров элементов схемы усилителя, конструирование эскиза топологии.

Методы разработки: конструирование эскиза топологии с помощью пакета программ AutoCAD.

Полученные результаты: библиотека элементов усилителя, эскиз топологии в формате AutoCAD.

Степень внедрения: не внедрено.

Область применения: не применяется.

Основные конструктивные и технико-эксплуатационные характеристики: количество слоев в кристалле – 6, количество элементов в принципиальной схеме –20 элементов, из них: 9 n-p-n транзистора, 9 резисторов.

Содержание

Введение

1. Общие принципы построения топологии биполярных ИМС

1.1 Выбор физической структуры разрабатываемой ИМС

2 Проектирование и расчет геометрических размеров элементов ИМС

2.1 Проектирование и расчет биполярных интегральных транзисторов

2.2 Расчет геометрических размеров резисторов

3 Разработка библиотеки элементов широкополосного усилителя

3.1 Расчет геометрических размеров биполярного n-p-n транзистора

3.2 Расчет геометрических размеров диффузионного резистора

4 Основные правила проектирования топологии ИМС

4.1 Проектирование топологии ИМС

Заключение

Список использованных источников

Приложение А. Эскиз топологии широкополосного усилителя

Введение

Основной тенденцией в современных полупроводниковых ИМС является увеличение степени интеграции. Это, как правило, проявляется в усложнении процесса проектирования топологии ИМС и в итоге появляющегося большего числа ошибок на стадии проектирования. Поэтому можно сказать, что разработка топологии ИМС является наиболее важной и ответственной операцией при проектировании любой ИМС.

В практике проектирования топологии существует много подходов. К одному из них можно отнести следующие этапы проектирования:

получение исходных данных;

расчет геометрических размеров активных и пассивных элементов;

разработка эскиза топологии;

разработка предварительных вариантов топологии;

выбор окончательного варианта топологии и его оптимизация.

Целью данного курсового проекта является расчет геометрических размеров элементов ИМС широкополосного усилителя, проектирование топологии данной схемы. Исходными данными при этом являются: схема электрическая принципиальная и электрические параметры.

Научной новизны курсовой проект не имеет. Практическая значимость заключается в том, что разработана топология полупроводниковой ИМС с заданными, в задании на проектирование, параметрами.

Разработанная топология полупроводниковой ИМС – это законченный элемент ИМС, который можно использовать при проектировании аналоговых микросхем.

1 Общие принципы построения топологии биполярных Имс

Общего подхода к проектированию биполярных интегральных микросхем нет и быть не может, каждый тип характеризуется своими особенностями в зависимости от требований и исходных данных ИМС. Исходными данными при конструировании микросхем являются: принципиальная электрическая схема с номинальными допусками на электрические параметры элементов, базовый технологический процесс с указанием технологических допусков. Принципиальная схема разрабатываемой ИМС широкополосного усилителя приведена на рисунке 1.1, а электрические параметры на данную схему в таблице 1.

Рисунок 1.1 – Принципиальная схема широкополосного усилителя

Таблица 1.

| Номер резистора |

Ri, кОм |

γRi, % |

PRi, мВт |

Номер транзистора |

Imaxэ, мА |

Uкв, В |

Номер диода |

Igi, мА |

Uкв, В |

| 1,5 |

4,2 |

20 |

1,0 |

1-5 |

4 |

12 |

1,2 |

2,8 |

12 |

| 2,4 |

1,0 |

20 |

1,0 |

6,7 |

4 |

12 |

| 3 |

0,1 |

15 |

4,0 |

8,9 |

8 |

12 |

| 6 |

2,65 |

18 |

1,5 |

| 7 |

0,7 |

16 |

4,2 |

Tmax = 950C |

| 8,9 |

5,4 |

20 |

1,0 |

Tmin = -500C |

1.1 Выбор физической структуры разрабатываемой ИМС

Основной структурой, определяющей электрические параметры и характеристики микросхемы, является транзистор. Поэтому, исходя из требований, предъявляемых к транзистору, производят выбор физической структуры различных областей [1], т.е. задаются определенными электрофизическими параметрами, к числу которых относятся: концентрация легирующих примесей, подвижность носителей заряда, время жизни и скорость поверхностной рекомбинации неосновных носителей заряда, удельное сопротивление материала, диэлектрическая проницаемость материала. Для расчета остальных элементов используется выбранная физическая структура основного транзистора.

В настоящее время существуют два основных вида физической структуры ИМС: микросхемы на основе биполярных транзисторов и микросхемы на основе МОП - структуры. Наибольшее количество слоев имеют микросхемы на основе биполярных транзисторов (рис. 1.2). Это скрытый n+-слой, эпитаксиальный, p+ - разделительный, базовый, эмиттерный, специальный резистивный, и т.д.. Для изготовления микросхем на основе МОП – транзисторов необходим лишь один диффузионный слой.

Рисунок 1.2 - Физическая структура биполярного n-p-n транзистора со скрытым n+-слоем.

Удельное сопротивление подложки выбирается исходя из требований к рабочему напряжению коллекторного перехода транзистора. При этом напряжение пробоя перехода коллектор-подложка должно быть больше, чем пробивное напряжение перехода коллектор-база. Удельное сопротивление подложки должно быть как можно большим. Это обеспечивает одновременно малую паразитную емкость перехода коллектор-подложка, но и надо иметь в виду, что одновременно будет увеличиваться сопротивление тела подложки, а это есть паразитный параметр, который сказывается на частотных свойствах. Удельное сопротивление подложки ρ - должно выбираться компромиссным путем из диапазона 1...10 Ом∙см. Толщина подложки должна обеспечивать механическую прочность микросхемы и она выбирается из диапазона hр =250...500 мкм.

Уровень легирования эпитаксиального слоя выбирается исходя из нескольких противоречивых требований:

-для высокого пробивного напряжения изолирующего перехода и для малой удельной емкости переходов необходимо, чтобы уровень легирования эпитаксиального слоя был как можно меньше (но чуть больше уровня легирования подложки);

-для уменьшения последовательного сопротивления тела коллектора, которое влияет на частотные свойства, уровень легирования должен быть как можно выше.

Эти противоречивые требования приводят к следующему компромиссу: сопротивление эпитаксиальной пленки выбирается таким, чтобы оно обеспечивало заданное высоковольтное напряжение самого высоковольтного транзистора с учетом способа его изготовления. Это приводит к выбору значения удельного сопротивления из диапазона ρк = 0,15…5 Ом∙см. Но при всех реальных параметрах транзисторов такие значения удельного сопротивления приводят к завышенному значению сопротивления тела коллектора. Во избежании этого вводят высоколегированный n+-слой. Т.к. напряжение коллектор – база транзисторов составляет Uкб = 12 В, то есть в несколько раз меньше пробивного напряжения перехода коллектор – база, следовательно не необходимости в применении дополнительных мерах защиты от пробоя.

Толщина эпитаксиальной пленки должна по возможности быть как можно меньше, но существует следующее ограничение:

,(1.1) ,(1.1)

где

hэп-глубина залегания коллекторного перехода;

-глубина проникновения n+-области в эпитаксиальный слой при всех температурных режимах формирования структуры; -глубина проникновения n+-области в эпитаксиальный слой при всех температурных режимах формирования структуры;

-ширина области пространственного заряда перехода коллектор-база при рабочем напряжении; -ширина области пространственного заряда перехода коллектор-база при рабочем напряжении;

-все технологические погрешности. -все технологические погрешности.

Скрытый n+-слой изготавливается для того, чтобы обеспечить минимальное сопротивление тела коллектора. Исходя из этой задачи скрытый слой должен быть максимально легирован, но должна быть обеспечена невозможность смыкания этого слоя с базой при подаче на этот переход коллектор-база рабочего напряжения. При этом расползание слоя при дальнейших технологических операциях должно быть строго контролировано. Поверхностное сопротивление скрытого слоя обычно составляет RSСС = 6...8 Ом/квадрат, толщина hсс = 3...8 мкм, поверхностная концентрация легирующих примесей (часто это сурьма из-за невысокого коэффициента диффузии при высоких температурах) RSСС = 1018…1019 см-3.

Базовая область изготавливается методом диффузии, поэтому является неоднородно легированной. Степень легирования выбирается из следующих требований:

-для увеличения напряжения пробоя перехода эмиттер-база и эффективности эмиттера следует легировать базу как можно меньше;

-снижение уровня легирования увеличивает паразитное сопротивление базы и ухудшает частотные характеристики транзистора;

-если базу слабо легировать, так что поверхностная концентрация будет составлять NSб ≤ 5∙1016 см-3, то это может привести к инверсии проводимости поверхностного слоя базы и выходу транзистора из строя.

Поверхностная концентрация примесей составляют примерно NSб = 1016…1019 см-3. Толщина металлургической базы ω0 = 0,5…1,0 мкм, среднее удельное сопротивление базовой области ρб = 0,1…1,0 Ом∙см, поверхностное сопротивление пассивной базы RSбП = 100…200 Ом/квадрат, поверхностное сопротивление активной базы RSба = 5…20 кОм/квадрат.

Уровень легирования эмиттерной области долже быть как можно выше. Но если уровень легирования достигает NSЭ ≈ 1021 см -3, тогда уменьшается время жизни носителей заряда, что приводит к уменьшению эффективности эмиттера. Поэтому уровень легирования выбирается из диапазона NSЭ = 1019…5∙1020 см-3, поверхностное сопротивление составляет RSэ = 5…7 Ом/квадрат. Глубина залегания перехода эмиттер-база определяется, как:

,(1.2) ,(1.2)

Глубина разделительной диффузии должна быть чуть больше толщины эпитаксиальной пленки, так чтобы обеспечивалось слитие этой области с подложкой. Уровень легирования этой области должен быть достаточно высок для эффективной изоляции p-n перехода на кристалле повышенной площади.

В полупроводниковых микросхемах в качестве межэлементных соединений применяются проводники из пленки алюминия. Для исключения пересечений проводников используется 3 основных метода: многослойная металлизация, прокладка шин металлизации над каналами резисторов, защищенными слоем SiO2 и проводящие диффузионные перемычки под слоем двуокиси кремния.

Минимальная ширина металлизированной дорожки (при заданной ее толщине) определяется допустимой плотностью тока. Толщина слоя Al шин металлизации составляет порядка 1,5 мкм и шина имеет удельное сопротивление слоя RS ≈ 0,05 Ом/квадрат Значение RS для пленки приблизительно в 2,5…3 раза превышает значение, получаемое из удельного сопротивления алюминия. Это связано с миграцией Al от коллекторных контактов выходных транзисторов, что повышает сопротивление тела коллектора, рост нитей Al, приводит к закорачиванию эмиттерных p-n переходов и другое.

Геометрические размеры контактных площадок определяются базовой технологией изготовления микросхем и составляют часто 100 × 100 мкм. Площадь контактных площадок должна обеспечивать хорошее соединение. Их целесообразно размещать под отдельными изолированными областями для уменьшения результирующей паразитной емкости и исключение опасности коротких замыканий при дефекте в окисле.

2 Проектирование и расчет геометрических размеров элементов ИМС

В данном разделе приведена методика расчетов геометрических размеров биполярных транзисторов и геометрических размеров резисторов.

2.1 Расчет биполярных интегральных транзисторов

В полупроводниковых ИМС на биполярных транзисторах основным является n-p-n транзистор. Все n-p-n транзисторы можно разделить на 2 группы:

а. Универсальные,

б. Специальные.

Универсальные в свою очередь делятся на: микро и маломощные (рассеиваемая мощность в диапазоне 0,3…3 мВт), транзисторы средней мощности (3…25мВт), мощные транзисторы (более 25мВт). Специальные делятся на: многоэмиттерный транзистор и p-n-p транзистор.

Выбор геометрических размеров транзисторов, количество эмиттеров, базовых и коллекторных контактов и их форма определяются требованиями к параметрам. Максимальная плотность эмиттерного тока, превышение которой приводит к уменьшению коэффициента усиления транзистора, ограничивает рабочий ток. Определение размеров эмиттерной области а, следовательно, и топологии транзистора проводится исходя из обеспечения максимального коэффициента усиления при рабочем токе эмиттера [2].

Расчет геометрических размеров эмиттерной области ведется следующим образом. Длина эмиттерной области рассчитывается по формуле

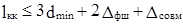

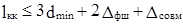

le = 3dmin + Δ,(2.1)

где

dmin-минимальный геометрический размер, обеспечиваемый используемым методом литографии.

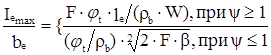

Далее определяем максимальный удельный ток для произвольного случая по формуле

,(2.2) ,(2.2)

где

Iemax-эмиттерный ток, превышение которого вызывает переход к высокому уровню инжекции;

β-максимальное значение коэффициента передачи тока;

.(2.3) .(2.3)

При ψ < 1 рабочей или “активной” является левая часть эмиттера, ближайшая к базовому контакту.

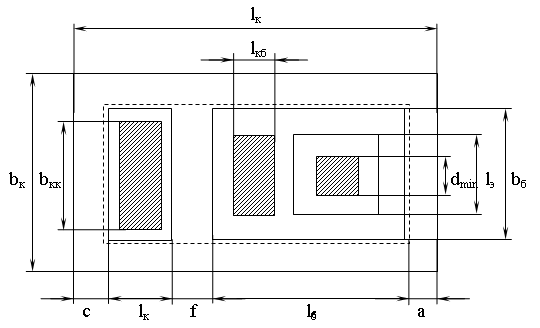

После определения геометрических размеров эмиттерной области транзистора необходимо определить полные геометрические размеры этого элемента. Для примера выберем одну из конфигураций транзистора (рис.2.1).

Найденные исходные данные le и be.

lb ≥ le + 4dmin + 2Δфш + Δсовм ,(2.4)

bb ≥ be + 2dmin + 2Δфш + Δсовм ,(2.5)

где

Δсовм–погрешность при совмещении фотошаблонов,

Δфш–погрешность при изготовлении фотошаблонов.

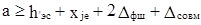

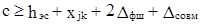

,(2.6) ,(2.6)

,(2.7) ,(2.7)

где

a-минимальное расстояние между краем разделительной диффузии и краем диффузии n+- слоя к коллектору.

,(2.8) ,(2.8)

,(2.9) ,(2.9)

.(2.10) .(2.10)

Рисунок 2.1 - Топологический чертеж маломощного n-p-n транзистора

Размеры коллектора определяются как

,(2.11) ,(2.11)

.(2.12) .(2.12)

По такой же методике рассчитываются геометрические размеры таких элементов, как p-n-p транзисторы и диоды на основе какого-либо перехода транзистора.

Рассчитанные таким образом линейные размеры транзистора с конкретной конфигурацией является минимально возможным для данного типа технологии и должны быть учтены для конкретных параметров и конкретных областей применения транзистора.

2.2 Расчет геометрических размеров резисторов

Резисторы биполярных микросхем обычно изготавливаются на основе отдельных диффузионных слоев транзисторной структуры или из поликремния.

Исходными данными при проектировании резисторов являются: номинал – R, поверхностное сопротивление слоя, на котором он изготовляется – RS, мощность рассеяния – P; погрешность номинала – YR, температурный диапазон работы – ΔT, bmin, погрешности изготовления –  ; удельная мощность рассеяния – P0 и т.д [3]. ; удельная мощность рассеяния – P0 и т.д [3].

В диапазоне номиналов от 100 Ом до 50 кОм резисторы изготовляют на основе базового слоя микросхемы. Его обычные параметры:

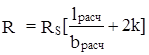

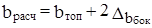

Расчет начинаем с определения коэффициента формы:

.(2.13) .(2.13)

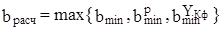

Если Кф > 1, то расчет начинаем с расчета b

Если Кф < 1, то расчет начинаем с расчета l

Если R = 50…1000 Ом, тогда резисторы делаются прямоугольной формы.Если R > 1…2 кОм, то рекомендуется изготавливать резистор сложной формы с любым числом изгибов и любой длиной прямоугольных участков.

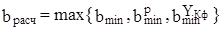

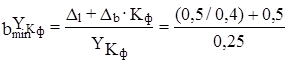

,(2.14) ,(2.14)

где

-минимальная ширина резистора, обеспечивающая необходимую рассеиваемую мощность; -минимальная ширина резистора, обеспечивающая необходимую рассеиваемую мощность;

-минимальная эффективная ширина резистора, обеспечивающая заданную точность изготовления. -минимальная эффективная ширина резистора, обеспечивающая заданную точность изготовления.

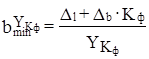

,(2.15) ,(2.15)

,(2.16) ,(2.16)

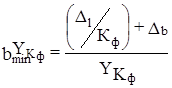

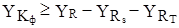

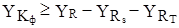

,(2.17) ,(2.17)

где

YКф-относительная погрешность изготовления резисторов;

YR-относительная погрешность номинала резистора;

YRs-относительная погрешность поверхностного сопротивления;

-относительная погрешность изменения номинала при изменении температуры. -относительная погрешность изменения номинала при изменении температуры.

Затем зная bрасч и Кф определяем lрасч,

lрасч = Кф∙bрасч.(2.18)

Рассчитав предварительную длину и ширину резистора необходимо проверить соотношения:

-для резистора прямоугольной формы

,(2.19) ,(2.19)

где

k-коэффициент приконтактной области. (Определяется по таблицам, графикам и монограммам.)

-для резистора сложной формы

,(2.20) ,(2.20)

где

n-число прямоугольных участков;

(n-1)-число изгибов;

0,55-коэффициент, учитывающий один изгиб.

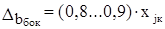

При этом следует помнить, что bрасч это эффективная, а не топологическая ширина резистора.

,(2.21) ,(2.21)

где

bрасч-топологическая ширина резистора (ширина на фотошаблоне);

-расползание диффузии в боковую область при диффузии. -расползание диффузии в боковую область при диффузии.

.(2.22) .(2.22)

3 Разработка библиотеки элементов широкополосного усилителя

Принципиальная электрическая схема генератор представленная в приложении . Она состоит из 35 элементов, из них: 14 n-p-n транзистора, 8 p-n-p транзисторов, 6 резисторов и 7 планарных транзисторов с инжекционным питанием (И2Л – логика). Таким образом, для создания библиотеки элементов цифра – аналогового преобразователя необходимо рассчитать геометрические размеры 1 n-p-n транзистора, 1 p-n-p транзисторов и резистора.

3.1 Расчет геометрических размеров биполярного n-p-n транзистора

Расчет геометрических размеров n-p-n транзистора производится в соответствии с методикой приведенной в пункте 2.1., следовательно, все расчет производятся исходя из размеров области эмиттера. Расчет области эмиттера производим исходя из минимального геометрического размера достижимого используемым методом литографии (по технологическим нормам ОАО «Орбита» - dmin = 6 мкм, Δфш = 0,5, Δсовм. = 0,5), соотношение 2.1, и по максимальному эмиттерному току (соотношение 2.2). Но так как мы не имеем исходных данных для расчета по этим формулам то, размер эмиттерной области можно провести по эмпирической формуле, полученной опытным путем.

I эmах = 0,16 Пэф,(3.1)

где

Iэmах–эмиттерный ток, превышение которого вызывает переход к высокому уровню инжекции;

Пэф–эффективный периметр эмиттера.

Максимальный эмиттерный ток для транзисторов использующихся в схеме широкополосного усилителя приведен в таблице 1. Типовое значение эмиттерного тока - Iэmах = 4 мА, то есть подставляя данное значение тока в соотношение 3.1 можно определить эффективный периметр эмиттера:

Пэфф =  = 16 мкм = 16 мкм

При работе транзистора фактически инжектирует только та часть эмиттера, которая ближе к базовому контакту. Тогда расчетный размер эмиттера выберем равным 16 мкм. Таким образом, эмиттер транзистора будет иметь квадратную форму со стороной

bэ = lэ = 3 dmin – Δ = 14 мкм.

Окна к эмиттерной области выберем равным минимальному размеру окна в окисле dmin = bэк = lэк = 6 мкм.

Как было замечено выше, погрешность совмещения фотошаблонов и погрешность при изготовлении фотошаблона равны Δсовм = Δфш =0,5 мкм, минимальный размер окна в окисле dmin = 6 мкм.

Все остальные геометрические размеры транзистора рассчитываются по формулам, приведенным в пункте 2.

Длина области базы рассчитывается по формуле 2.4

lб ≥ 14 + 4·6 + 2∙0,5 + 0,5 = 39,5 мкм.

Примем lб = 40 мкм.

Ширина области базы рассчитывается по формуле 2.5

bб ≥ 14 + 2·6 + 2∙0,5 + 0,5 = 27,5 мкм.

Примем bб = 28 мкм.

Длина окна контакта к базовой области равна минимальному размеру окна в окисле lбк = dmin = 6 мкм, ширина

bбк ≤ bб – 2dmin + 2Δфш + Δсовм = 28 – 12 + 1 + 0,5 = 15,5 мкм.

Примем bбк = 14 мкм.

a ≥ hэс+ xjкб+2Δфш + Δсовм = 8 + 2,5 + 1 + 0,5 = 12 мкм,

с  hэс+xjэб+2Δфш + Δсовм = 8 + 1,7 + 1 + 0,5 = 11,2 мкм. hэс+xjэб+2Δфш + Δсовм = 8 + 1,7 + 1 + 0,5 = 11,2 мкм.

Примем с = 12 мкм.

f  xiкб+xjэб+2Δфш + Δсовм = 2,5 + 1,7 + 1 + 0,5 = 5,7 мкм. xiкб+xjэб+2Δфш + Δсовм = 2,5 + 1,7 + 1 + 0,5 = 5,7 мкм.

Примем f = 6 мкм.

= 28 + 24 + 1 + 0,5 = 53,5 мкм. = 28 + 24 + 1 + 0,5 = 53,5 мкм.

Примем bк = 54 мкм.

Геометрические размеры подконтактной области коллектора рассчитываются по формулам

= 18 + 1 + 0,5 = 19,5 мкм. = 18 + 1 + 0,5 = 19,5 мкм.

Примем lкк = 18 мкм.

= 54 – 24 + 1 + 0,5 = 31,5 мкм. = 54 – 24 + 1 + 0,5 = 31,5 мкм.

Примем bкк = 30 мкм.

= 40 + 18 + 12 + 12 + 6 + 1 +0,5 = = 40 + 18 + 12 + 12 + 6 + 1 +0,5 =

= 89,5 мкм,

Примем lк = 90 мкм.

3.2 Расчет геометрических размеров диффузионного резистора

В схеме широкополосного усилителя (Приложение А) имеются 9 резисторов с разбросом номиналов от 700 Ом до 5,4 кОм и различной мощностью рассеивания. Наибольшее распространение получили диффузионные резисторы на основе базовой диффузии.

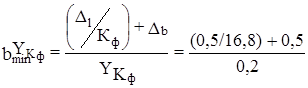

Так как все резисторы выполнены на одном слое, то нет необходимости приводить подробные расчеты каждого резистора. Для примера, рассчитаем резистор R1 и проведем расчет его геометрических размеров по методике описанной в пункте 2.2, при Rs = 250 Ом/□.

Расчет начинаем с определения коэффициента формы:

Так как Кф > 1, то расчет начинаем с расчета ширины резистора - b.

,(2.14) ,(2.14)

где

-минимальная ширина резистора, обеспечивающая необходимую рассеиваемую мощность; -минимальная ширина резистора, обеспечивающая необходимую рассеиваемую мощность;

-минимальная эффективная ширина резистора, обеспечивающая заданную точность изготовления. -минимальная эффективная ширина резистора, обеспечивающая заданную точность изготовления.

Минимальная эффективная ширина диффузионного резистора bmin = dmin = 6 мкм.

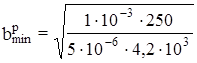

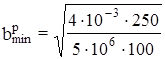

Из соотношения 2.15 определяем  . Значение рассеиваемой резистором мощности и номинал приведено в табличных данных задания на курсовой проект, типовое значение допустимой мощности рассеиваемой резистором – P0 ≈ 5 Вт/мм2. . Значение рассеиваемой резистором мощности и номинал приведено в табличных данных задания на курсовой проект, типовое значение допустимой мощности рассеиваемой резистором – P0 ≈ 5 Вт/мм2.

= 3,45 мкм = 3,45 мкм

; ;

. .

где

YR = 20 %-относительная погрешность номинала резистора;

YRs = 5 - 10 %-относительная погрешность поверхностного сопротивления (примем YRs = 10 %);

-относительная погрешность изменения номинала при изменении температуры. Температурный коэффициент сопротивления базового резистора - αT = 0,002 Ом∙К-1. -относительная погрешность изменения номинала при изменении температуры. Температурный коэффициент сопротивления базового резистора - αT = 0,002 Ом∙К-1.

∙100 % = 29 % ∙100 % = 29 %

= 20 – 10 – 29 = 20 % = 20 – 10 – 29 = 20 %

= 1,1 мкм = 1,1 мкм

Примем эффективную ширину резистора - bрасч. = 6 мкм.

lрасч = Кф∙bрасч = 16,8 ∙ 6 = 100,8 мкм.

Примем lрасч. = 101мкм.

По формуле (2.20) проведем проверку номинала резистора исходя из расчетных значений длины и ширины резистора.

R1 = 250∙[(95/6) + (4-1) ∙ 0,55] = 18,6∙250 = 4,3 кОм

Аналогичным образом производиться расчет для остальных резисторов.

. .

Минимальная эффективная ширина диффузионного резистора bmin = dmin = 6 мкм.

= 44,7 мкм = 44,7 мкм

; ;

. .

где

YR = 15 %;

YRs = 10 %

30 % 30 %

= 15 – 10 – 30 = 25 % = 15 – 10 – 30 = 25 %

= 7 мкм = 7 мкм

Примем эффективную ширину резистора - bрасч. = 45 мкм.

lрасч = Кф∙bрасч = 0,4 ∙ 45 = 18 мкм.

Примем lрасч. = 18 мкм.

По формуле (2.20) проведем проверку номинала резистора исходя из расчетных значений длины и ширины резистора.

R3 = 250∙(18/45) = 100 Ом

Остальные резисторы рассчитываются аналогичным образом.

4 Основные правила проектирования топологии ИМС

Главное требование при разработке топологии - максимальная плотность упаковки элементов при минимальном количестве пересечений межэлементных соединений. При этом обеспечивается оптимальное использование площади кристалла при выполнении всех конструктивных и технологических требований и ограничений. Исходными данными при разработке топологии являются принципиальная электрическая схема, технологические и конструктивные требования и ограничения.

При разработке топологии ИМС придерживались следующих основных правил проектирования топологии полупроводниковых ИМС с изоляцией p-n-переходом [1]:

1). Для учета влияния диффузии примеси под маскирующий окисел, растравливания окисла, ошибок фотолитографии при составлении топологической схемы все элементы схем, кроме контактных площадок, рекомендуется размещать на расстоянии от щели под разделительную диффузию, равном удвоенной толщине эпитаксиального слоя.

2). К изолирующим p-n-переходам всегда должно быть приложено напряжение обратного смещения, что практически осуществляется подсоединением подложки p-типа, или области разделительной диффузии p-типа, к точке схемы с наиболее отрицательным потенциалом. При этом обратное напряжение, приложенное к изолирующему p-n - переходу, не должно превышать напряжения пробоя.

3). При размещении элементом микросхем и выполнении зазоров между ними необходимо строго выполнять ограничения, соответствующие типовому технологическому процессу.

4). Резисторы, формируемые на основе базового диффузионного слоя, можно располагать в одной изолированной области, которая подключается к самому положительному потенциалу схемы, т.е. к коллекторному источнику питания.

5). Резисторы на основе эмиттерного и коллекторного слоев следует располагать в отдельных изолированных областях.

6). Реальная форма резисторов, кроме ширины полоски, не является критичной. Резисторы могут быть прямыми, изогнутыми или иметь любую другую форму, однако во всех случаях отношение длины резистора к его ширине должно быть согласовано с удельным сопротивлением исходного диффузионного слоя и обеспечено получением заданного номинала. Высокоомные резисторы следует выполнять в виде параллельных полосок с перемычками между ними. Номинальное сопротивление резистора в этом случае будет выдержано более точно, чем при изогнутом резисторе.

7). Для уменьшения мест локального нагрева резисторы с большой рассеиваемой мощностью не следует располагать вблизи активных элементов, а рекомендуется выносить из на край кристалла.

8). Резисторы, у которых нужно точно выдержать отношение номиналов, должны иметь одинаковую ширину и конфигурацию и располагаться рядом с друг другом. Это правило относится и к другим элементам микросхем, для которых требуется обеспечить согласование характеристик, т.е. их топологии должны быть одинаковы, а взаимное расположение - как можно более близким.

9). Любой диффузионный резистор может пересекаться проводящей дорожкой, так как проведение металлического проводника по слою двуокиси кремния, покрывающего резистор, не оказывает существенного вредного влияния.

10). Форма и место расположения конденсаторов не является критичными.

11). Для диффузионных конденсаторов требуются отдельные изолированные области. Исключение составляют случаи, когда один из выводов конденсатора является общим с другой изолированной областью.

12). Транзисторы n-p-n-типа, работающие в режиме эмиттерного повторителя, можно размещать в одной изолированной области вместе с резисторами.

13). Все коллекторные области n-типа, имеющие различные потенциалы, должны быть изолированы.

14). Для каждого диода, формируемого на основе перехода коллектор-база, должна быть предусмотрена отдельная изолированная область. Диоды, формируемые на основе перехода эмиттер-база, можно размещать в одной изолированной области.

15). Для улучшения развязки между коллекторными изолированными областями контакт к подложке рекомендуется выполнять в непосредственной близости от мощного транзистора.

16). Для диффузионных областей требуются отдельные изолированные области.

17). Для уменьшения паразитной емкости между контактными площадками и подложкой под каждой из них рекомендуется создавать изолированную область. В этом случае емкость между контактной площадкой и подложкой оказывается включенной последовательно с емкостью изолирующего перехода и, следовательно, результирующая паразитная емкость уменьшается.

18). Соединения, используемые для ввода питания и заземления, следует выполнять в виде коротких широких полосок, что обеспечивает уменьшение паразитных сопротивлений.

19). Число внешних выводов в схеме, а также порядок расположения и обозначения контактных площадок выводов микросхем на кристалле должны соответствовать выводам корпуса.

20). Коммутация элементов микросхем должна иметь минимальное количество пересечений. Если полностью избежать пересечений не удается, их можно осуществить, используя обкладки конденсаторов, формируя дополнительные контакты к коллекторным областям транзисторов, применяя диффузионные перемычки и создавая дополнительные слои изоляции между пересекающимися проводниками. При разработке топологической схемы необходимо стремиться к получению минимально возможной длины межэлектродных соединений.

21). Когда наличие паразитных емкостей не существенно, резисторы могут быть размещены в тех же изолированных областях, что и транзисторы. При этом не имеет значения, должны ли они соединяться между собой. Расстояние между резисторами должно быть не менее 10 мкм. Коллектор транзистора и резистор должны располагаться на расстоянии не менее 12 мкм.

22). Расстояние между диффузионной базовой областью и контактом коллектора может быть увеличено, чтобы провести одну или две металлические дорожки между контактами коллектора и базы. Это можно сделать, так как коллекторный ток главным образом протекает от базы через скрытый слой к коллекторному контакту. Однако чем больше расстояние между базой и коллектором, тем больше паразитное сопротивление и паразитная емкость коллектора. Металлический проводник не может быть размещен между контактами базы и эмиттера за счет удлинения диффузионного базового слоя.

23). Наиболее важным правилом при разработке топологии является минимизация площади, занимаемой микросхемой. Это позволяет увеличить число микросхем, изготовляемых на пластине с заданным диаметром. Кроме того, необходимо учесть, что вероятность случайных дефектов в полупроводниковом кристалле возрастает с увеличением площади. Размеры микросхем зависят от числа изолирующих областей и их площадки, а также от суммарной площади соединительной металлизации, включая площадь, занимаемую контактными площадками.

4.1 Проектирование топологии ИМС широкополосного усилителя

Исходными данными являются принципиальная электрическая схема (Приложение А) геометрические размеры элементов. На этом этапе решаются такие вопросы, как определение необходимого числа изолированных областей, минимизация возможного числа пересечений коммутационных шин элементов и длины шин.

Все транзисторы данной ИМС выполнены по стандартной конфигурации рис.1.2.

Транзисторы VT3, VT5 исполняют роль дифференциального усилителя нагруженного активной нагрузкой выполненной на транзисторах VT2, VT4 и резисторы R2, R4. Диоды D1, D2 включенные последовательно задают напряжение смещения на базе транзисторов. Транзисторы VT1, VT7 включенные по схеме с общим эмиттером обеспечивают большое входное сопротивление данной схемы. Оконечный каскад выполнен на транзисторах VT8, VT9 и резисторах R6 – R9.

Резисторы R1 – R5, R6, R8 – R9 обладают довольно большим номиналом, следовательно, имеют сложную форму, т.е. выполнены в виде меандра. Резисторы помещены в два изолирующих кармана, и подключается к самому высокому потенциалу схемы, т.е. к коллекторному источнику питания.

При проектировании топологии усилителя использовалось один слой металлизации.

Для уменьшения паразитной емкости между контактными площадками и подложкой под каждой из них создана изолированная область.

Топологический чертеж принципиальной схемы приведен в Приложении Б.

Заключение

На основе исходных данных приведенных в задании была разработана библиотека элементов и рассчитаны геометрические размеры элементов. На основе рассчитанных элементов был разработан эскиз топологии ИМС широкополосного усилителя.

Список использованных источников

1.Матсон Э.А., Крыжановский Д.В. Справочное пособие по конструированию микросхем Мн.: Высш. шк. 1982

2.Конструирование и технология микросхем. Курсовое проектирование: Учеб. пособие для вузов. Коледов Л.А., Волков В.А., Докучаев Н.Н. и др.; Под ред. Л.А. Коледлва.-М.: Высш. шк., 1984. 231с., ил.

3.Березин А.С., Мочалкина О.В. Технология и конструирование интегральных схем М. Радио и связь 1983 г

4.Курносов. А. И., Юдин В. В. Технология производства полупроводниковых и интегральных микросхем – М.: Высшая школа, 1986 г. – 368 с.

Приложение А

|