Федеральное агентство по образованию Российской Федерации

Государственное образовательное учреждение

высшего профессионального образования

Тульский государственный университет

Кафедра «Автоматизированные станочные системы»

Курсовая работа

по дисциплине

«Общая электротехника и электроника»

Пояснительная записка

Задание № 7-28

Выполнил:

студент гр. 620281 Кураева Ю.И

Проверил:

преподаватель Золотых С.Ф

Тула 2010

СОДЕРЖАНИЕ

Введение

1. Цель и задачи выполнения курсовой работы

2. Принцип работы ЭП ПТ и общие требования к функционированию контроллера

3. Проектирование блока центрального процессора

4. Проектирование блока запоминающих устройств

5. Проектирование интерфейсного модуля

5.1 Разработка адресного дешифратора

5.2 Разработка регистра вектора прерывания

6. Разработка программного обеспечения

6.1 Разработка подпрограммы пуска ЭД

6.2 Разработка подпрограммы обслуживания прерывания

6.3 Расчет цифрового эквивалента

6.4 Разработка подпрограммы задержки

6.5 Распределение памяти

7. Расчет источника питания

7.1 Расчет стабилизатора

7.2 Расчет выпрямителя

7.3 Расчет трансформатора питания

Заключение

Список используемой литературы

Широкое внедрение в промышленность роботов и гибких производств потребовало существенного расширения и повышения эффективности системы подготовки и переподготовки специалистов в этой области. Создание систем управления роботами и гибкими автоматизированными производствами базируется на средствах вычислительной техники, в первую очередь на больших интегральных схемах и микропроцессорных вычислительных машинах микроЭВМ. По этому одним из направлений подготовки специалистов по системам управления роботами является изучение принципов работы и методов проектирования устройств управления, построенных на базе выпускаемых промышленностью микропроцессорных наборов и микро ЭВМ.

Успехи в области микроэлектроники открывают новые возможности для автоматизации производственных процессов, машин, оборудования и приборов на базе микропроцессоров (МП). Микропроцессоры представляют собой устройства обработки цифровой информации, конструктивно выполненные в виде больших интегральных схем (БИС).

В основу курсового проекта положено проектирование систем на базе одной серии БИС - БИС КР580. Этот выбор обусловлен следующими причинами:

1. Микропроцессорный комплект БИС КР580 является комплектом общего назначения и используется в управляющей, информационной, измерительной, связной, медицинской, бытовой и другой аппаратуре самого различного применения.

2. Комплект БИС серии КР580 представляет собой один из первых отечественных микропроцессорных комплектов. К настоящему времени уже накоплен достаточный опыт построения аппаратурынаего основе. Объем производства МП и микроЭВМ постоянно возрастает, улучшаются их технические характеристики и снижается стоимость. Благодаря реализованной в них возможности программного управления они обладают свойствами универсальных устройств цифрового управления. Это способствует массовому применению МП и микроЭВМ в народном хозяйстве для цифровой обработки данных и управления различными объектами и процессами.

Курсовая работа выполняется с целью закрепления знаний по курсу «Общая электротехника и электроника» и развития навыков самостоятельной работы студентов при разработке технического задания, проектировании и эксплуатации отдельных узлов микропроцессорных систем ЧПУ и обработки данных. Задачами выполнения курсовой работы являются:

- получение навыков разработки схемотехнических вопросов микро процессорной техники;

- проработка ряда вопросов, связанных с прикладным программным обеспечением микропроцессорных систем;

- приобретение практических навыков составления и расчета принципиальных электрических схем цифровой и аналоговой техники.

Электродвигатели (ЭД) постоянного тока нашли широкое применение в приводах главного движения и приводах подач металлорежущих станков и промышленных роботов. Причина - простой способ регулирования частоты вращения вала электродвигателя путем изменения величины управляющего постоянного напряжения. Чем больше управляющее напряжение, тем выше частота вращения. Причем изменение полярности управляющего напряжения приводит к изменению направления вращения вала электродвигателя.

В комплект ЭП ПТ входит тахогенератор ТГ, который закреплен на валу ЭД. Выходное напряжение ТГ, которое пропорционально частоте вращения вала ЭД, используется для ее контроля.

Для управления ЭП ПТ применяются МП контроллеры, которые должны в зависимости от требуемой частоты вращения задавать управляющее напряжение Uупр

и контролировать фактическую ее величину по уровню постоянного напряжения, снимаемого с тахогенератора Uтг

(рис. 1).

Рис. 1 Структура электропривода постоянного тока с микропроцессорным управлением

В состав МП контроллера входят два модуля: процессорный и интерфейсный. Процессорный модуль осуществляет отработку управляющих про грамм для реализации алгоритма управления ЭП ПТ. Интерфейсный модуль обеспечивает связь процессорного модуля с электроприводом: преобразование цифровых сигналов в аналоговые и наоборот, промежуточное хранение данных и фиксацию управляющих сигналов.

Проектируемый МП контроллер обеспечивает следующий алгоритм работы ЭП ПТ.

Перед пуском ЭД, т.е. перед подачей Uупр

, МП контроллер проверяет наличие сигнала "Готовность", поступающего с электропривода (наличие пи тающего напряжения, снятие различных блокировок и т.д.). При отсутствии данного сигнала МП контроллер не производит пуск ЭД и выдает сигнал "Сбой" на световой индикатор. Если сигнал "Готовность" присутствует, то процессорный модуль МП контроллера выдает в интерфейсный модуль цифровой эквивалент Uупр

, который цифро-аналоговым преобразователем преобразуется в аналоговую величину.

После подачи Uупр

на электродвигатель МП контроллер осуществляет программным способом определенную по времени задержку, необходимую для разгона ЭД до заданной частоты вращения, а затем вводит цифровой эквивалент напряжения ТГ. Преобразование аналоговой величины UТГ

в цифровую осуществляется в интерфейсном модуле аналого-цифровым преобразователем.

После ввода UТГ

МП контроллер приступает к сравниванию ее величины с yровнем Uупр

. Если уровень UТГ

соответствует Uупр

, то пуск произошел в нормальном режиме.

Если соответствия нет, то имеет место нештатная ситуация, например, перегрузка ЭД. В этом случае МП контроллер выдает нулевой уровень Uупр

(останов ЭД) и сигнал "Сбой", который индицируется светодиодом в интерфейсном модуле.

При пуске ЭД могут возникнуть различные аварийные ситуации. При наличии сигнала "Авария" МП контроллер должен прервать подпрограмму пуска, остановить ЭД и выдать сигнал "Сбой".

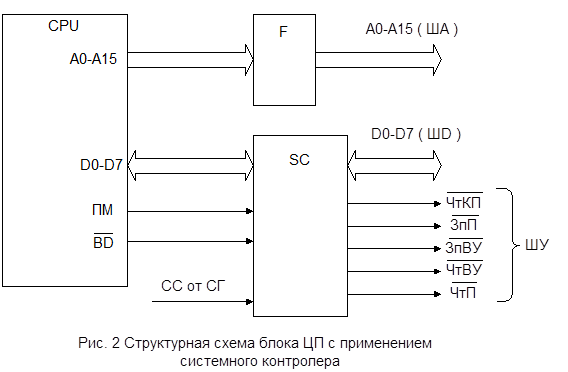

Структурная схема блока ЦП представлена на рис. 2. В его состав кроме ЦП и системного генератора СГ ( на рис. не показан) входят:

- однонаправленный буфер шины адреса БШA;

- системный контроллер СК, объединяющий двунаправленный буфер шины данных, регистр словосостояния и логическую схему формирования шины управления.

Включение БША должно быть таким, чтобы все 16 разрядов ША передавались с его входа на выход.

Так как ШД двунаправленная, то направлением передачи информации через СК необходимо управлять. Это осуществляет сигнал "Прием" (ПМ). При уровне лог. 1 сигналы с ШД через СК должны передаваться в ЦП, а при лог. 0 - из ЦП в ШД.

В начале каждого машинного цикла микропроцессора на ШД выдается восьмиразрядное словосостояние ЦП, отдельные разряды которого используются для формирования сигналов ШУ. Словосостояние ЦП определяет действия, выполняемые микропроцессором в данном машинном цикле (чтение/запись ЗУ, чтение/запись внешних устройств (ВУ) и т.д). Словосостояние фиксируется в СК по сигналу "Строб со стояния" (СС) от системного генератора и хранится в нем до окончания машинного цикла.

СК также служит для формирования следующих управляющих сигналов ШУ:

-  - чтение контроллера прерывания; - чтение контроллера прерывания;

-  - запись в память; - запись в память;

-  - запись во внешнее устройство; - запись во внешнее устройство;

-  - чтение с внешнего устройства; - чтение с внешнего устройства;

-  - чтение из памяти. - чтение из памяти.

Сигналы ПМ и  , ("Выдача") в логической схеме используются для стробирования управляющих сигналов. , ("Выдача") в логической схеме используются для стробирования управляющих сигналов.

Схема подключения СГ к ЦП стандартная. Кварцевый резонатор BQ 1 обеспечивает возбуждение генератора. Интегрирующая цепочка RC служит для первоначального сброса СГ и ЦП при включении питания, а кнопка SB1 - для принудительного сброса. На входе "Готовность" ГT присутствует уровень лог.1, т.к. предполагается, что быстродействие ЗУ и ВУ соизмеримо с быстродействием ЦП.

4.

Проектирование блока запоминающих устройств

Согласно заданию блок ЦП состоит из следующих устройств:

- Центральный процессор КР580 ВМ80

- Системный генератор КР580 ГФ24

- Буфер шины адреса КР589 АП16

- Буфер шины данных КР580 ВК28

Рассмотрим подробно работу блока ЦП.

Главным элементом блока ЦП является микропроцессор. Он подключен по стандартной схеме к системному генератору. Кварцевый резонатор BQ1 обеспечивает возбуждение генератора. Интегрирующая цепочка RC обеспечивает первоначальный сброс системного генератора и микропроцессора при включении питания. Кнопка SB1 предназначена для принудительного сброса. На вход генератора «Готовность» подается лог. 1, так как предполагается, что быстродействие ЗУ и ВУ сопоставимы с быстродействием ЦП. Работа ЦП представляет собой последовательное циклическое выполнение набора инструкций. Во время машинного цикла процессор может производить чтение/запись ЗУ, чтение/запись ВУ (внешних устройств) и др. Действия микропроцессора определяют значение разрядов т.н. восьмиразрядного словосостояния ЦП. По сигналу «Строб состояния» от системного генератора словосостояние ЦП записывается в микросхему системного контролера, выполняющего в данном микроконтроллере функцию буфера шины данных, где и хранится до окончания машинного цикла. Системный контроллер объединяет в себе буфер шины данных и логическую схему управления им. Для нормального функционирования микроконтроллера шина адреса также буферизируется с помощью микросхем буфера шины адреса (БША). Включение БША должно быть таким, чтобы все 16 разрядов шины адреса передавались с его входа на выход, поэтому данный БША состоит из двух микросхем, включенных параллельно.

По заданию требуется спроектировать блок ЗУ со следующими параметрами:

- объем ОЗУ 4 Кб

- организация микросхем ОЗУ 4 Кбx1

- объем ПЗУ 4 Кб

- организация микросхем ПЗУ 1Кбx4

Это означает, что ОЗУ должно иметь 4 Кб при использовании микросхем, позволяющих хранить 4 Кб одноразрядных слов. Соответственно и для ПЗУ.

Блок ЗУ организуется по страничному принципу. Для хранения в ОЗУ 4 Кбайта необходимо 8 микросхем с организацией 4 Кбx1. Для адресации микросхем ОЗУ используются разряды А0-А11 ША.

Соответственно ПЗУ будет состоять из четырех страниц, которые будут организованы на двух микросхемах. Для адресации микросхем ПЗУ используются разряды А0-А9 ША.

Выбор той или иной страницы памяти производит адресный дешифратор. Для его разработки составим таблицу адресов ЗУ:

| А |

А |

А |

А |

А |

А |

А |

А |

А |

А |

А |

А |

А |

А |

А |

А |

Адрес |

№ |

ЗУ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

стр. |

| 0

|

0

|

0

|

0

|

0

|

0

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Нач. адр.0000 |

0 |

| 0

|

0

|

0

|

0

|

1

|

1

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Кон.адр.0FFF |

| 0

|

0

|

0

|

1

|

0

|

0

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Нач. адр.1000 |

0 |

ПЗУ |

| 0

|

0

|

0

|

1

|

0

|

0

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Кон. адр.13FF |

| 0

|

0

|

0

|

1

|

0

|

1

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Нач. адр.1400 |

1 |

| 0

|

0

|

0

|

1

|

0

|

1

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Кон. адр.17FF |

| 0

|

0

|

0

|

1

|

1

|

0

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Нач. адр.1800 |

3 |

| 0

|

0

|

0

|

1

|

1

|

0

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Кон. адр.1BFF |

| 0

|

0

|

0

|

1

|

1

|

1

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Нач. адр.1C00 |

4 |

| 0

|

0

|

0

|

1

|

1

|

1

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Кон. адр.1FFF |

На вход разрешения дешифрации подаются сигналы ЧтП и ЗпП, объединенные по «И». В этом случае дешифрация номеров страниц ЗУ будет осуществляться лишь при обращении к ЗУ.

Сформированные сигналы «Выбор страницы» поступают на входы «выбор микросхемы» каждой страницы ЗУ. При наличии 0 на этом входе микросхема ЗУ выводится из высокоимпедансного состояния и, если это схема ПЗУ, то её выход подключается к ШД, на которую поступают данные выбранные по адресу в соответствии с состоянием разрядов А0-А9.

На микросхемы ОЗУ кроме того необходимо подать сигнал Чт\Зп . Если на этот вход подается 1, то осуществляется запись байта данных с ШД в ячейку с адресом в разрядах А0-А11 и, если подается 0 – считывание в ШД из этой ячейки. Данный режим работы обеспечивается подачей сигнала ЗпП на вход W\R каждой микросхемы памяти.

5.

Проектирование интерфейсного модуля

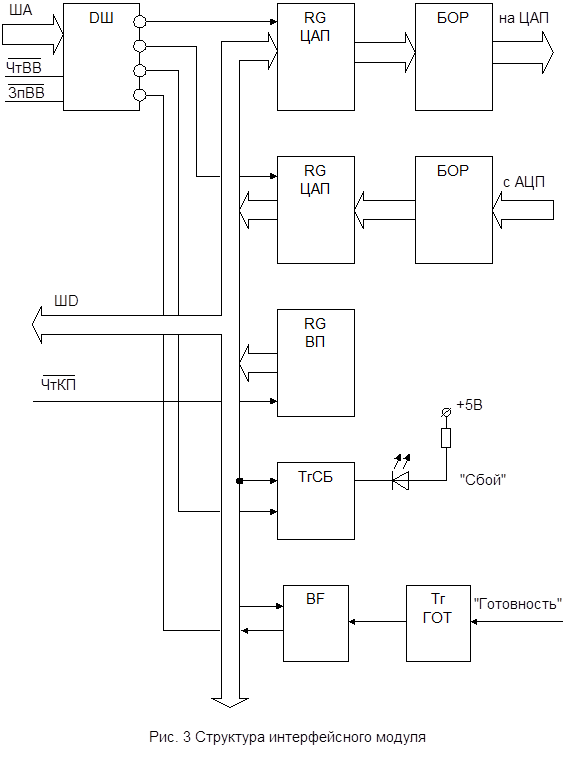

В состав интерфейсного модуля (рис. 3) входят следующие блоки:

- адресный дешифратор (ДШ);

- регистр цифро-аналогового преобразователя (RG ЦАП);

- регистр аналого-цифрового преобразователя (RG АЦП);

- регистр вектора прерывания (RG ВП);

- триггер "Сбой" (Тг СБ);

- триггер "Готовность" (Тг ГОТ);

- буфер-формирователь (BF);

- блоки оптронной развязки (БОР).

Адресный дешифратор производит выбор порта (регистра или триггера) с которым производится обмен информацией путем дешифрации его адреса, поступившего с ША. По сигналу, поступающему с ДШ, производится либо синхронизация вводимой информации в порт , либо вывод выходов порта из высокоимпедасного состояния при чтении содержимого портов.

Регистр ЦАП служит для хранения цифрового эквивалента управляющего напряжения для его последующего преобразования в аналоговую вели чину в цифро-аналоговом преобразователе.

Регистр АЦП служит для приема и хранения цифрового эквивалента напряжения тахогенератора UТГ

, после его преобразования в АЦП.

Регистр вектора прерывания хранит код команды RST. По сигналу "Чтение контроллера прерываний"  выходы регистра выводятся из высокоимпедансного состояния, что обеспечивает выдачу хранимого кода на ШД. выходы регистра выводятся из высокоимпедансного состояния, что обеспечивает выдачу хранимого кода на ШД.

Информационный вход триггера СБ подключается к одному из разрядов ШД. Синхронизация записи в триггер осуществляется сигналом с ДШ.

Запись информации в триггер ГОТ осуществляется внешними сигналами (информационным и синхронизирующим), поступающими с электропривода. Для того, чтобы не блокировать один из разрядов ШД состоянием триггера (0 или 1) выход триггера подключается к одному из разрядов ШД через буфер-формирователь (ВF), имеющий третье состояние. Вывод буфера из этого со стояния (подключение триггера к ШД) осуществляется сигналом с ДШ.

5.1 Разработка адресного дешифратора

Начальный адрес портов интерфейсного модуля – Е3 .

Тогда адреса остальных портов определяются соответственно – Е4, Е5 и Е6.

Представим адреса портов в двоичном коде:

А7…... A0 - разряды ША ;

1110 0011 - адрес RG ЦАП ( порт 1 ) ;

1110 0100 - адрес RG АЦП ( порт 2 ) ;

1110 0101 - адрес Тг СБ ( порт 3 ) ;

1110 0110 - адрес Тг ГОТ ( порт 4 ) .

Дешифрация, т.е. обращение к портам, будет иметь место только в том случае, если хотя бы один из сигналов ЧтВВ или ЗпВВ примет нулевой уровень (обращение к портам ввода/вывода).

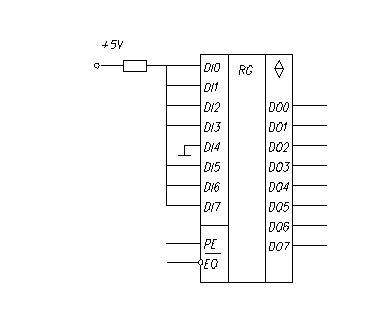

Структура команды RST , код которой хранит RG ВП, имеет следующий вид:

Д7............... Д0 - разряды ШД ;

1 1 x x x 1 1 1 - код команды .

где xxx - двоичный код вектора прерывания.

При четвертом векторе - 11101111. Учитывая, что логической 1 соответствует уровень напряжения > 2,4 В, а логическому 0 -

уровень <

0.4 В входы регистра ( в соответствии с полученным кодом RST) подключают к питанию +5В или к нулевому проводу (Рис.4).

Рис.4

Разработка программного обеспечения включает в себя разработку подпрограммы пуска ЭД, подпрограммы обслуживания прерывания и распределение памяти.

6.1 Разработка подпрограммы пуска ЭД

Блок-схема подпрограммы пуска ЭД, реализующая алгоритм, представлен на рис. 5.

В начале подпрограммы необходимо разрешить микропроцессору обслуживание прерывания и установить указатель стека на выбранный адрес ОЗУ.

При программировании операции ввода состояния триггера ГТ необходимо предварительно установить соответствие между состоянием триггера (лог. 1 или 0) и состоянием электропривода ("готов или не готов").

В блоке 3 производится анализ состояния того разряда ШД , к которому подключен триггер ГT.

В регистр ЦАП выводится цифровой эквивалент управляющего напряжения. Поэтому перед программированием этой операции необходимо вычислить по заданному Uупр его цифровой аналог (см. ниже ) .

Задержка времени для разгона ЭД может быть реализована в виде подпрограммы или без нее. Предварительно необходимо по заданному времени задержки произвести соответствующие вычисления (см. ниже).

В блоках 6 и 7 производится ввод цифрового эквивалента напряжения тахогенератора и его сравнение с цифровым эквивалентом управляющего напряжения. При несоответствии производится вывод

в RG ЦАП кода 00 ( блок 8 ), а в триггер СБ - сигнала "Сбой". Вывод в триггер необходимо организовать таким образом; чтобы разряд ШД, к которому подключен триггер, при вводе принял состояние, при котором светодиод должен излучать. Передача лог. 1 или 0 по этому разряду определяется схемой подключения светодиода к триггеру.

6.2 Разработка подпрограммы обслуживания прерывания

Подпрограмма начинает работу при поступлении сигнала "Авария" на вход микропроцессора " Запрос прерывания " (ЗПР). В состав подпрограммы входят три блока, выполняющиеся последовательно друг за другом.

Первый блок осуществляет запрет прерывания и запись в стек содержимого регистров МП.

Второй блок обнуляет регистр ЦАП и выдает сигнал "Сбой".

Третий блок осуществляет вызов из стека содержимого регистров МП, разрешение прерывания и переход на конец подпрограммы пуска.

6.3 Расчет цифрового эквивалента

Расчет сводится к преобразованию заданного управляющего напряжения из десятичной формы в шестнадцатеричную. Причем старший разряд кодирует направление вращения:

0 - прямое вращение, 1 - обратное.

Задано Uупр = -1,28 В. Так как в ЦАП цифровой код преобразуется в аналоговую величину с определенной дискретностью ( 0.05 В ), то первоначально вычисляется количество дискрет для представления аналоговой величины заданного уровня. Для уровня -1,28 В количество дискрет составляет 2610

, а двоичный эквивалент 110012

. С учетом направления вращения получим 1110012

, в шестнадцатеричной форме 1916

.

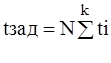

Подпрограмма задержки реализуется путем организации циклического процесса из N циклов. Если известно время выполнения i-той команды ti

, в цикле и количество таких команд K в цикле, то время задержки составит:

Период выполнения одной команды равен:

T = 1 / 2,5*106

= 0,4*10-6

c.

1ком.

= 25 такт.

Время выполнения одной команды равно:

tодн.ком.

= T * 25 = 0,4*10-6

* 25 = 10-5

c.

Количество команд в цикле равно:

Kком.

= tзад.

/ tодн.ком.

= 0,87 / 10-5

= 87000

В шестнадцатеричном представлении N

= 1 53D816

или 3216

*1416

*4416

Структура памяти МП контроллера оформляется в виде, представленном на рис. 10

В начальных адресах ( 00 00 - 00 3F ) располагаются восемь областей, закрепленных за конкретным вектором прерывания. За четвертым вектором закреплены 8 байтов с адресами 00 20 - 00 27. Поскольку подпрограмма обслуживания прерывания занимает больший объем памяти, чем отведенный под вектор прерывания, то в этих областях размещают только команду безусловного перехода по адресу, с которого размещена подпрограмма обслуживания прерывания. Стек - это любая область ОЗУ. Однако его целесообразнее располагать начиная с конечной ячейки, т. к. его заполнение происходит в сторону младших адресов. Подпрограммы пуска и обслуживания прерывания располагаются в тех местах памяти , в каких разработчик считает целесообразным в зависимости от объемов ОЗУ и ПЗУ.

00 00

00 1F

|

ОЗУ |

00 20

00 27

|

Команда перехода по адресу 02 31 |

00 28

00 3F

|

| 01 FF |

Стек |

02 00

02 30

|

Подпрограмма пуска ЭД |

ПЗУ |

02 31

02 42

|

Подпрограмма обслуживания прерывания |

02 43

0B FF

|

Резерв |

Рис. 6 Распределение памяти

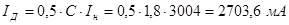

Источник питания рассчитывается только по каналу +5В, так как именно по этому каналу питания МП контроллер потребляет основную мощность.

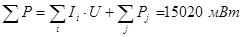

Первоначально определяется суммарная потребляемая мощность всеми применяемыми микросхемами данного контроллера. Исходя из потребляемой мощности, определяется ток нагрузки  при заданном напряжении при заданном напряжении  . .

; ;

; ;

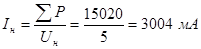

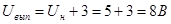

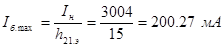

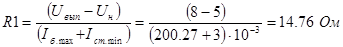

7.1 Расчет стабилизатора

Расчет позволит выбрать все элементы стабилизатора, исходя из заданного выходного напряжения  , и тока нагрузки , и тока нагрузки  . .

Расчет ведем в следующем порядке:

1. Определяем необходимое для работы стабилизатора входное напряжение ( ) при заданном выходном ( ) при заданном выходном ( ): ):

Здесь цифра 3 , характеризующая минимальное напряжение между коллектором и эмиттером транзистора взята в расчете на использование как кремниевых, так и германиевых транзисторов.

2. Определяем максимальную рассеиваемую транзистором мощность:

3. Выбираем регулирующий транзистор. Его предельно допустимая мощность должна быть больше значения  , предельно допустимое напряжение между эмиттером и коллектором – больше , предельно допустимое напряжение между эмиттером и коллектором – больше  , а максимально допустимый ток коллектора – больше , а максимально допустимый ток коллектора – больше  . По справочнику выбираем транзистор КТ 805Б . По справочнику выбираем транзистор КТ 805Б

| Транзистор |

|

|

|

|

| КТ 805Б |

5 |

160 |

15 |

30 |

4. Определяем максимальный ток базы регулирующего транзистора:

. .

5. Выбираем подходящий стабилитрон. Его напряжение стабилизации должно быть равно выходному напряжению стабилизатора, а значение максимального тока стабилизации превышать максимальный ток базы  . По таблице выбираем стабилитрон КС 447А: . По таблице выбираем стабилитрон КС 447А:

| Стабилитрон |

Напряжение стабилизации, В |

|

| Минимальный |

Максимальный |

| КС 447А |

4,7 |

3 |

160 |

6. Подсчитываем сопротивление резистора R1.

. .

7. Подсчитываем мощность рассеяния резистора R1.

. .

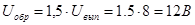

7.2 Расчет выпрямителя

Рассчитать выпрямитель – значит правильно выбрать выпрямительные диоды и конденсатор фильтра, а также определить необходимое переменное напряжение, снимаемое для выпрямления с вторичной обмотки сетевого трансформатора.

Исходными данными для расчета выпрямителя служат: требуемое выпрямленное напряжение  и потребляемый максимальный ток и потребляемый максимальный ток  . .

Расчет ведем в следующем порядке

1. Определяем переменное напряжение, которое должно быть на вторичной обмотке сетевого трансформатора.

. .

Где В

– коэффициент, зависящий от нагрузки (принимается по таблице в методических указаниях).

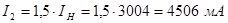

2. По току нагрузки определяем максимальный ток, текущий через каждый диод выпрямительного моста.

. .

Где С

– коэффициент, зависящий от нагрузки (принимается по таблице в методических указаниях).

3. Подсчитываем обратное напряжение, которое будет приложено к каждому диоду выпрямителя.

. .

4. Выбираем диоды, у которых значения выпрямленного тока и допустимого обратного напряжения равны или превышают расчетные. Выбираем диод Д 303.

| Тип диода |

|

|

| Д 303 |

3 |

150 |

5. Определяем емкость конденсатора фильтра:

7.3 Расчет трансформатора питания

Зная необходимое напряжение на вторичной обмотке  и потребляемый максимальный ток нагрузки и потребляемый максимальный ток нагрузки  , трансформатор рассчитываем в такой последовательности: , трансформатор рассчитываем в такой последовательности:

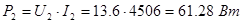

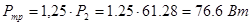

1. Определяем значение тока, текущего через вторичную обмотку трансформатора

2. определяют мощность, потребляемую выпрямителем от вторичной обмотки трансформатора:

3. Подсчитываем мощность трансформатора

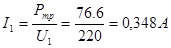

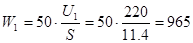

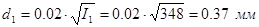

4. Определяем значение тока, текущего в первичной обмотке

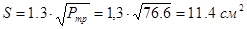

5. Рассчитываем необходимую площадь сечения сердечника магнитопровода

6. Определяем число витков первичной (сетевой) обмотки

7. Определяем число витков вторичной обмотки

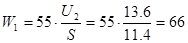

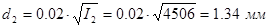

8. Определяем диаметры проводов обмоток трансформатора

Заключение

В данном курсовом проекте была разработана микропроцессорная система управления электродвигателем постоянного тока. Система обеспечивает контроль за скоростью вращения. Данный комплекс можно использовать в станкостроении и машиностроении для управления ЭД.

Выполнение курсового проекта выполнило задачи:

- получение навыков разработки схемотехнических вопросов микропроцессорной техники;

- проработка рядов вопросов, связанных с прикладным про граммным обеспечением микропроцессорных систем;

- приобретение практических навыков составления и расчета принципиальных электрических схем цифровой и аналоговой техни ки.

Список используемой литературы

1. Алексеенко А.Г., Галицин А.А., Иванников А.Д. Проектирование радиоэлектронной аппаратуры на микропроцессорах. - •М.:Радио и связь, 1984.

2. Балашов Е.П., Пузанков Д.В. Микропроцессоры и микропроцессорные системы: Учебн. пособие для вузов. - М.: Радио и связь, 1981.

3. Гушников B.C. Интегральная электроника в измерительных устройствах. - Л.: Энергоатомиздат, 1988.

4. Зельдин Е.А. Цифровые интегральные микросхемы в информационно измерительной аппаратуре. - Л.: Энергоатомиздат,1986.

5. Каган Б.М., Стамин В. В. Основы проектирования микропроцессорных устройств автоматики. - М.: Энергоатомиздат,1987.

6. Калабеков Б. А. Микропроцессоры и их применение в системах передачи и обработки сигналов: Учебн. пособие для вузов.- М.: Радио и связь, 1988.

7. Микро ЭВМ: В 8 кн.: Практ. пособие / Под ред. Л.Н. Прохина. Кн.З. Семейство ЭВМ "Электроника К1" / А.В.Кобылинский, А.В.Горячев, Н.Г.Сабодаш, В.В.Проценко. - М.: Выс. школа, 1988.

1. 8. Микропроцессоры и микро ЭВМ в системах автоматического управления: Справочник С.Т.Хвощ, Н.Н.Варлинский, Е.А.Попов; Под общ. ред. С.Т.Хвоща. - Л.: Машиностроение, 1987.

8. Огнев И.В., Шамаев Ю.М. Проектирование запоминающих устройств. - М.: Выси. школа, 1979.

9. Полупроводниковые БИС запоминающих устройств: Справочник З.В.Баранов, Н.В.Бекин, А.Ю.Гордонов и др.; Под общ. ред. А.Ю.Гордоноваи Ю.Н.Дьякова. - М.: Радио и связь, 1986

Щелкунов Н.Н., Дианов А.П. Микропроцессорные средства системы. - М.: Радио и связь, 1989.

|