Впервые технология Thumb была встроена в ядро ARM7 еще в 1995 году. Адаптированное под технологию Thumb (Thumb-ориентированное) ядро получило типовое обозначение ARM7TDMI и за достаточно короткое время было лицензировано большим количеством фирм-изготовителей всевозможного оборудования, поскольку технология Thumb, явилась откликом фирмы ARM на стремление разработчиков критичных к стоимости применений, типа сотовых телефонов, дисководов CD, модемов и пейджеров, получить приборы с 32-разрядной производительностью и 32-разрядным адресным пространством, но без увеличения стоимости, связываемого с переходом к 32-разрядным системам. Превосходная плотность кода, достигаемая использованием технологии Thumb, позволяет уменьшить требуемый объем памяти - обеспечивает 32-разрядную производительность системы при использовании памяти 16-разрядного формата, что ведет к снижению стоимости системы.

Необходимо отметить, что ядро ARM7TDMI используется при создании не только специализированных ИС, но и при создании микроконтроллеров общего назначения. Так фирма Atmel в сентябре 1998 года начала поставки микроконтроллеров семейства AT91, в основу которых положено ядро ARM7TDMI. Информацию по приборам серии AT91 можно получить на сайте http://www.gaw.ru/html.cgi/doc/atmel/at91.htm.

Архитектура ARM является RISC архитектурой, и система команд и связанный с нею механизм декодирования намного проще, чем у микропрограммируемых CISC компьютеров, что приводит к высокой скорости обработки команд, впечатляющей скорости отклика на прерывания (в реальном масштабе времени), реализации прибора на кристалле малых размеров и, следовательно, малой стоимости прибора.

Конвейерная обработка реализована таким образом, что все компоненты систем памяти и обработки работают непрерывно. Обычно, в то время как одна команда выполняется, следующая команда декодируется и третья команда выбирается из памяти.

Возможности системы команд ARM7TDMI могут быть расширены за счет добавления до 16 внешних сопроцессоров.

При разработке интерфейса памяти разработчики ориентировались на обеспечение реализации потенциально возможной производительности без повышения стоимости самой памяти. Критичные к быстродействию сигналы управления также конвейеризованы с тем, чтобы реализовать функции управления системой памяти в стандартной логике с малым потреблением, и эти сигналы управления упрощают использование быстрых локальных режимов обращения, необходимых для стандартных динамических RAM. Кроме того, интерфейс памяти идеально подходит для организации взаимодействия как со встроенной на кристалл памятью, так и с внешней памятью, с блоками Flash памяти, что позволяет реализовать внутрисистемное программирование, защиту памяти, снизить время выхода на рынок, сократить общую стоимость системы.

Интерфейс с памятью у процессора ARM7TDMI организуется следующими основными элементами:

32-разрядной шиной адреса, определяющей адрес ячейки памяти, которую необходимо использовать.

32-разрядной двунаправленной шиной передачи данных D[31:0], плюс двумя отдельными однонаправленными шинами данных DIN[31:0] и DOUT[31:0], через которые перемещаются команды и данные. Данные могут иметь формат слова, полуслова или байта.

Сигналами управления, определяющими, например, формат перемещаемых данных и направление их передачи и, кроме того, уровень приоритета.

Рис. 1. Блок-схема процессора ядра ARM7TDMI

Этот набор сигналов позволяет ARM7TDMI достаточно просто организовывать интерфейс с DRAM, SRAM и ROM. Для полного использования страничного режима доступа к DRAM, обеспечивается информация о том, является доступ к памяти последовательным или нет. Вообще говоря, интерфейс со статической памятью намного проще чем интерфейс с динамической памятью.

Поскольку ядро ARM7TDMI в основе своей имеет ядро ARM7, то ограничимся кратким напоминанием о его архитектуре и больше внимания уделим особенностям, внесенным технологией Thumb.

Процессор ARM7TDMI - 32-разрядный RISC процессор с 3-уровневым конвейером, сформированный вокруг банка из 37 32-разрядных регистров, в который входят 6 регистров состояния. Процессор оснащен встроенным умножителем 32x8 и 32-разрядным многорегистровым циклическим устройством сдвига. Пять независимых встроенных шин (PC шина, шина инкремента, шина ALU и A- и B-шины) обеспечивают, при выполнении команд высокую степень параллелизма.

Как видно из сравнения блок-схем процессоров ARM7 и ARM7TDMI (См. Рис. 1) в блоке конвейера процессора добавился декомпрессор команд Thumb.

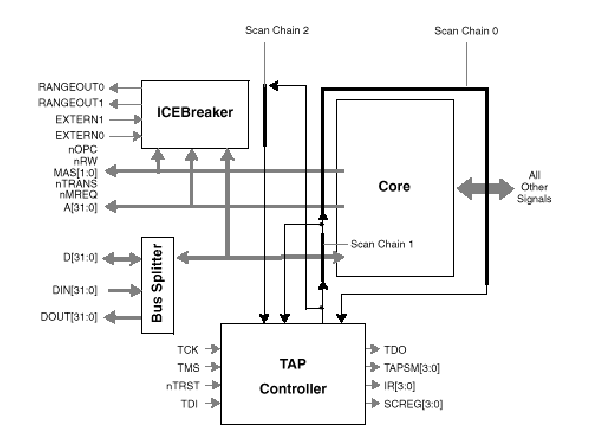

Однако разработчики фирмы ARM этим не ограничились и, имея в виду встраивание ядра в приборы с большим уровнем интеграции, расширили ядро ARM7TDMI (см. Рис. 2) дополнительными аппаратными блоками, обеспечивающими возможность отладки глубоко встроенного ядра.

Рис. 2. Блок-схема ядра ARM7TDMI

Как видно из Рис. 2, ядро ARM7TDMI состоит из ядра собственно процессора, показанного на Рис.1, и расширений отладки: контроллера сканирования TAP (boundary scan) и внутрисхемного эмулятора (ICEBreaker).

Аппаратные расширения отладки ARM7TDMI, обеспечивают развернутые возможности отладки, облегчающие разработку пользовательского прикладного программного обеспечения, операционных систем, и самих аппаратных средств. Аппаратные расширения отладки позволяют останавливать ядро или при выборке заданной команды (в контрольной точке) или при обращении к данным (в точке просмотра), или асинхронно - по запросу отладки.

В этих точках, через JTAG последовательный интерфейс, может быть исследовано внутреннее состояние ядра ARM7TDMI, находящегося в состоянии отладки, и внешние состояния системы. По завершении исследования состояния ядра и системы могут быть восстановлены и продолжено выполнение программы.

Режим отладки ARM7TDMI устанавливается или запросом по одному из сигналов внешнего интерфейса отладки, или внутренним функциональным блоком ICEBreaker, состоящим из двух модулей контрольных точек (watchpoint), работающих в реальном масштабе времени с регистрами состояния и управления ядра, и обеспечивающим поддержку встроенной отладки ядра ARM7TDMI. ICEBreaker программируется в последовательном режиме с использованием контроллера TAP - средства управления работой цепочек сканирования (Scan Chain 0, 1 и 2) через последовательный интерфейс JTAG.

Интерфейс отладки ARM7TDMI основан на архитектуре, описанной в стандарте IEEE Std. 1149.1-1990 "Standard Test Access Port (TAP) and Boundary-Scan Architecture".

Как уже отмечалось выше высокопроизводительное 32-разрядное статическое RISC ядро ARM7TDMI занимает на кристалле очень малую площадь, малое потребление энергии ядром позволяет использовать его в критичных к потреблению применениях, технология Thumb позволяет использовать память 16-разрядного формата меньшей емкости и, соответственно, меньшей стоимости. Не удивительно, что только в течение года, по окончании разработки ядра ARM7TDMI, ядро было лицензировано такими фирмами, как NEC, TI, Symbios Logic, Oki, Atmel, Samsung и VLSI. В дальнейшем лицензии на использование ядра ARM7TDMI получили такие гранды полупроводниковой и электронной отраслей как IBM, HP, Epson, Matsushita и многие другие.

Идя навстречу запросам фирм-разработчиков ASIC и ASSP, разработчиков электронной аппаратуры фирма ARM расширила номенклатуру функциональных макроядер на основе ядра ARM7TDMI (будем называть макроядром некоторое ядро, в данном случае ARM7TDMI, со схемотехнически интегрированными вместе ним дополнительными, расширяющими его возможности функциональными модулями) и в настоящее время в семейство ARM7 Thumb входят: ядро ARM7TDMI, макроядра ARM710T, ARM720T и ARM740T, и синтезируемое (с изменяемой конфигурацией) ядро ARM7TDMI-S.

Основные характеристики четырех первых процессоров приведены в таблице.

| Ядро CPU |

Площадь кристалла |

Потребление (mW/MHz) |

Тактовая частота |

Производительность |

Ядро CPU |

Кэш |

Управление памятью |

ARM7TDMI

ARM RISC

ядро с Thumb и EmbeddedICE

|

1, 0 мм2 при 0, 25мкм

2, 1 мм2 при 0, 35 мкм

4, 8 мм2 при 0, 6 мкм

|

Пиковое: 1, 2

Среднее: 0, 6

Idle: < 100 мкВт, при 3, 3 В, CMOS 0, 35 мкм

|

66 МГц при нормах 0, 35 µ м, CMOS |

0, 9 MIPS/MHz 59 MIPS при 66 МГц |

N/A |

N/A |

N/A |

ARM710T

Кэшированное процессорное макроядро

|

5, 8 мм2 при 0, 25 мкм

11, 7 мм2 при 0, 35 мкм

|

Пиковое: 3, 6

Среднее: 1, 8

Idle: < 100 мкВт при включенном кэш, 3, 3 В, 0, 35мкм CMOS

|

59 МГц при нормах 0, 35мкм CMOS |

53 MIPS при 59МГц |

ARM7TDMI |

8 Кбайт единый кэш |

MMU с полной поддержкой виртуальной памяти |

ARM740T

Кэшированное процессорное макроядро

|

4, 9 мм2 при 0, 25 мкм

9, 8 мм2 при 0, 35 мкм

|

Пиковое: 3, 5

Среднее: 1, 6

Idle: <100 мкВт при включенном кэш, 3, 3 В, 0, 35мкм CMOS

|

59 МГц при нормах 0, 35мкм CMOS |

53 MIPS при 59МГц |

ARM7TDMI |

8 Кбайт единый кэш |

Простая Конфигурация Памяти и Защиты |

ARM720T

Кэшированное процессорное макроядро с MMU для WindowsCE

|

5, 8 мм2 при 0, 25мкм

11, 7 мм2 при 0, 35 мкм

|

Пиковое: 3, 6

Среднее: 1, 8

Idle: < 100 мкВт при включенном кэш, 3, 3 В, 0, 35мкм CMOS

|

59 МГц при нормах 0, 35мкм |

53 MIPS при 59МГц |

ARM7TDMI |

8 Кбайт единый кэш |

MMU с полной поддержкой виртуальной памяти и быстрого контекстного переключения |

Необходимо отметить, что указанные в таблице характеристики (тактовая частота, производительность, потребление, площадь, занимаемая на кристалле) представлены приведенными к CMOS технологии с топологическими нормами 0, 35 мкм. Масштабирование топологии к меньшим топологическим нормам приведет к росту и тактовой частоты и производительности при соответствующем уменьшении занимаемой на кристалле площади напряжения питания и потребления. Так фирма TI, использующая в ряде своих разработок ядро ARM7TDMI, при CMOS технологии GS20 с топологическими нормами 0, 18 мкм получила тактовую частоту свыше 80 МГц, и готова использовать его в CMOS технологии GS30 с топологическими нормами 0, 15 мкм.

При разработке этих макроядер фирма ARM ориентировалась на конкретные области применения, где особенности каждого макроядра позволят реализовать дополнительные возможности без существенного прироста стоимости. Добавление к макроядрам встроенного кэш позволяет минимизировать время доступа к внешней памяти и, сохраняя максимальную производительность, позволяет использовать недорогие RAM. Становится возможным использование системной шины и внешней памяти с быстродействием более низким, чем быстродействие процессора и, следовательно, уменьшить потребление. Широкая полоса частот системной шины может быть также использована и для увеличения полной производительности системы - высвобожденную полосу частот могут использовать другие периферийные устройства, обеспечивая высокую пропускную способность данных в устройствах типа MPEG декодеров цифровых TV приставок.

Макроядро ARM710T, ориентированное на персональные информационные устройства (PDA) и Internet применения, оснащено встроенным полнофункциональным MMU, обеспечивающим использование таких операционных систем как pSOS и EPOC32. Возможность использования виртуальной памяти, обеспеченная MMU, позволяет безопасно использовать коды выгруженные из сети типа Internet или от независимого разработчика. Такая возможность позволяет считать ядро процессора ARM710T идеальным для применения в PDA, интеллектуальных телефонах или Internet телевидении.

Макроядро ARM720T, ориентированное на операционную систему WindowsCE, располагает всеми функциональными возможностями ядра ARM710T плюс специальная поддержка операционной системы WindowsCE. Невысокая цена, высокая производительность и малое потребление процессора ARM720T делают его идеальным решением для перспективных приложений, использующих WindowsCE в PDA, карманных PC, TV и Internet приставках, интеллектуальных телефонах и автомобильных PC.

Макроядро ARM740T, ориентированное на высокопроизводительные встраиваемые применения, в отличие от других макроядер, оснащено кэш который может быть емкостью или 4 или 8 Кбайт и, кроме того, модулем защиты буфера записи и памяти (не полнофункциональным MMU). Макроядро ARM740T ориентировано на использование в мультимедиа и встраиваемых применениях типа цифровых TV приставок, Internet аппаратуры и сетевых устройств, в модемах и системах, для которых разрабатывается специальное ПО, не требующее управления виртуальной памятью, обеспечиваемой MMU.

Выигрыш, который может получить разработчик - более низкая стоимость устройств, малое потребление, за счет малого размера кристалла и снижения сложности схемы. Стоимость разработки ПО также снижается за счет более простой структуры управления памятью.

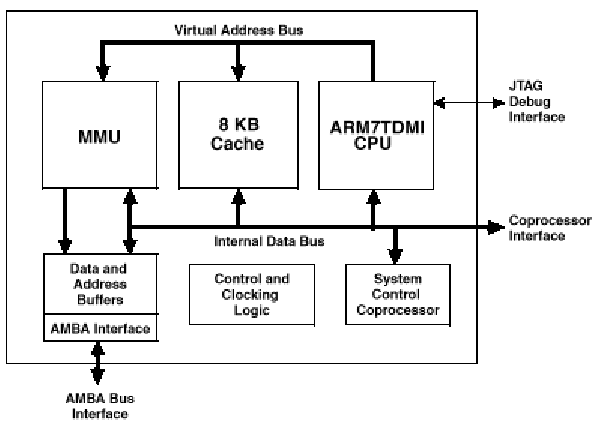

Более полное представление об уровне интеграции макроядер можно получить сравнив блок-схему ядра ARM7TDMI с блок-схемой макроядра ARM710T, приведенной на Рис.3.

Рис. 3. Блок-схема макроядра ARM710T

Рисунок из файла DDI-0086B.pdf (стр. 1-3). Адрес страницы - http://www.arm.com/Pro+Peripherals/Index.html

В процессорных макроядрах ARM710T, ARM720T и ARM740T используется стандартный интерфейс шины AMBA фирмы ARM, упрощающий проектирование ASIC, базирующихся на этих ядрах, обеспечивающий использование стандартной периферии из библиотек фирмы ARM и способствующий многократному использованию схемотехнических решений. Кроме того, шина AMBA упрощает тестирование глубоко встроенных ядер ARM без модификации логики тестирования или тестовых таблиц.

Макроядра оснащены портами для присоединения встраиваемых сопроцессоров, что обеспечивает расширение функциональных возможностей макроядер ARM7XXT архитектурно непротиворечивым способом.

Ядро ARM7TDMI-STM, являющееся последним пополнением семейства ARM7T, это Thumb-ориентированное синтезируемое 32-разрядное RISC ядро с изменяемой конфигурацией, высокой производительностью и малым потреблением.

Ядро ARM7TDMI-S программно совместимо с популярным ARM7TDMI ядром, так что программы для каждого ядра могут разрабатываться на одних и тех же средствах разработки программного обеспечения и основное отличие ядра ARM7TDMI-S от ARM7TDMI ядра заключается в том, что ядро ARM7TDMI-S является полностью синтезируемым - обеспечивающим простую интеграцию в современные технологии изготовления ASIC а это, в свою очередь, способствует сокращению срока выхода применений на рынок. Кроме того, ядро ARM7TDMI-S оптимизируется в процессе синтеза самой фирмой - изготовителем на получение наивысшей производительности элементов используемой библиотеки или на обеспечение специальных требований применения. Тестирование в процессе производства и широкий диапазон средств выявления дефектов также расширяют возможности ядра ARM7TDMI-S.

При разработке ядра ARM7TDMI-S учитывались требования современной методологии синтеза:

Стратегия однотактового выполнения операций и синхронная схемотехника

Однонаправленный шинный интерфейс

Отсутствие ложных путей

Параметризуемые скрипты для получения необходимых размеров и производительности

Доступность как в VHDL, так и в Verilog

Варианты минимальной стоимости проекта на основе ядра ARM7TDMI-S реализуются средствами селективного синтеза. Уменьшенный размер кристалла может быть получен за счет исключения логики EmbeddedICE или использования упрощенной схемы умножителя. Кроме того, исключение логики EmbeddedICE увеличивает уровень защиты программ и данных в требующих повышенных средств защиты применениях типа смарткарт. На основе базового ядра ARM7TDMI-S могут быть синтезированы четыре ядра:

| Синтезируемое ядро |

Умножитель* |

Логика EmbeddedICE |

| ARM7TDMI-S |

Расширенный |

Имеется |

| ARM7TDI-S |

Упрощенный |

Имеется |

| ARM7TM-S |

Расширенный |

Отсутствует |

| ARM7T-S |

Упрощенный |

Отсутствует |

*Примечание:

Расширенный: умножение 8-разрядов/цикл с 64-разрядным результатом и аккумулированием.

Упрощенный: умножение 2-разрядов/цикл с 32-разрядным результатом и аккумулированием.

|