| Кафедра "Вычислительная техника

"

КУРСОВАЯ РАБОТА

На тему: Проектирование устройств на языке

VHDL САПР MAX+PLUS II

Москва, 2009

Содержание

1.1 Введение и Общие сведения о САПР MAX+PLUS II

1.2 Ввод проекта и компиляция

1.3 Моделирование

1.4 Размещение проекта в ПЛИС

1.5 Разработка пересчетных схем

1.6 Создание символа

Литература

1.1 Введение. Общие сведения о САПР MAX+PLUS II

В настоящее время для проектирования ПЛИС фирмы Altera в основном используются два типа САПР: MAX+PLUS II и Quartus. В настоящей главе рассматривается САПР MAX+PLUS, которая включает в себя полный пакет программных средств для проектирования ПЛИС фирмы Altera, в том числе синтез схем с использованием языка VHDL.

В систему MAX PLUS II входят средство для отображения иерархической структуры проекта (Hierarhy Display); графический редактор Graphic Editor; текстовый редактор (Text Editor) для создания и редактирования проектов на языках описания схем, в том числе VHDL; средство для создания и редактирования новых символов (Symbol Editor); графический редактор для ввода тестовых сигналов при моделировании (Waveform Editor); программа для компиляции проектов Compiler; средство для просмотра и редактирования результатов размещения и трассировки (Floorplan Editor); программа моделирования Simulator и другие модули.

1.2 Ввод проекта и компиляция

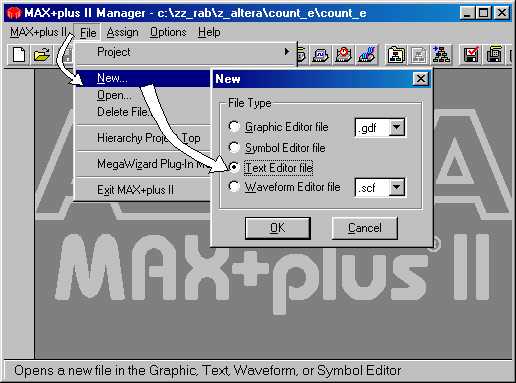

Для ввода проекта сначала создаются необходимые каталоги, в которых будут располагаться проекты, например, в каталоге VHDL_curs создается подкаталог grup_fio (группа_ФИО-латинскими символами), а в нем подкаталог первого проекта, например count_e. Затем необходимо открыть новый файл, для чего из основного окна надо выполнить следующую последовательность команд: File Þ New, после чего в открывшемся окне надо выбрать пункт «Text Editor File». Эта последовательность показана на рис. 3.1. Данный файл необходимо сохранить, при этом надо задать расширение VHD.

Рис. 3.1. Открытие текстового файла.

После этого необходимо зарегистрировать проект. Регистрация проекта с именем, совпадающим с именем текстового файла, осуществляется последовательным выбором пунктов меню: File Þ Project Þ Set Project to Current File. После этого проводится ввод текста проекта и выбор микросхемы (см. рис. 3.2). В приведенном на рис. 3.2 примере выбирается микросхема EPF8282ALC84.

Пусть в исходном файле введено следующее описание:

library IEEE;

use IEEE.std_logic_1164.all;

entity count_e is

port( clk, enable : in STD_LOGIC;

q : out INTEGER range 0 to 63);

end count_e;

architecture e of count_e is

begin

process (clk)

variable cnt: INTEGER range 0 to 63;

begin

if (clk'event and clk = '1') then

if enable = ‘1’ then

cnt := cnt+1;

end if;

end if;

q <= cnt;

end process;

end e;

Рис. 3.2. Выбор микросхемы

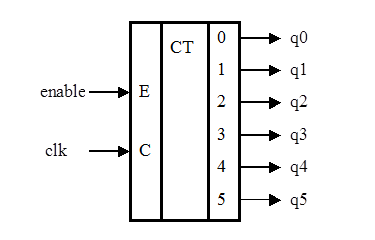

В приведенной программе описан шестиразрядный счетчик, срабатывающий по переднему фронту синхросигнала, то есть по изменению тактового сигнала с “0” на “1” (clk'event and clk = '1’'). Входной сигнал enable является сигналом разрешения, причем “1” соответствует разрешению счета, выходной сигнал счетчика q задается как целое (integer) в диапазоне от 0 до 63 (range 0 to 63). В приведенном описании используется переменная cnt, значение которой присваивается выходному сигналу q. Схема разрабатываемого счетчика приведена на рис. 3.3.

Рис. 3.3. Шестиразрядный счетчик

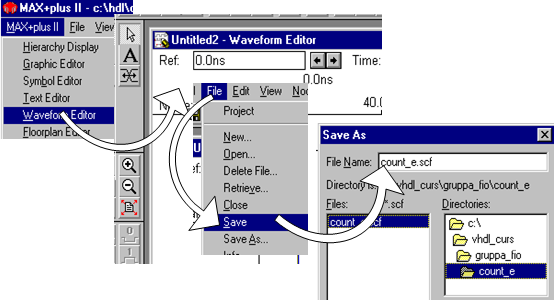

1.3 Моделирование

Рис. 3.4. Регистрация графического файла

При моделировании схем используется графический редактор Waveform Editor. Сначала должен быть создан и зарегистрирован графический файл, процесс регистрации фала с именем count_e.scf показан на рис. 3.4.

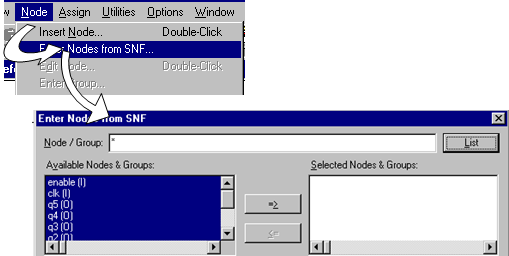

После регистрации необходимо указать, на каких контактах желательно просмотреть сигналы. Процесс выбора тестируемых сигналов показан на рис. 3.5. Когда откроется окно Enter Node from SNF, то необходимо нажатием кнопки List открыть список всех входов-выходов (контактов).

Рис. 3.5. Выбор тестируемых контактов.

Средства редактора Waveform Editor позволяют формировать произвольные последовательности воздействий, масштабировать их во времени; сигналы на шинах представлять в виде векторов двоичных сигналов или в виде чисел (двоичных, восьмеричных, шестнадцатиричных, десятичных); копировать и вставлять фрагменты, менять местами поля, занимаемые сигналами и т.п. На рис. 3.6 показан результат формирования входных сигналов clk и enable.

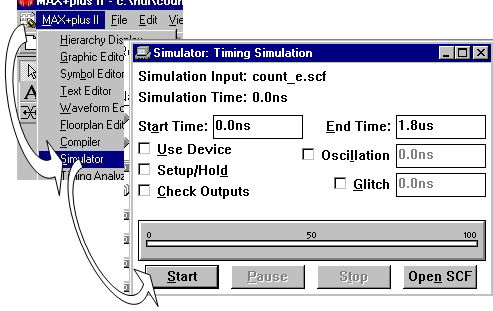

Следующим этапом является установка параметров моделирования, в том числе времени окончания (End Time), для чего необходимо выполнить действия, показанные на рис. 3.7.

Рис. 3.7. Установка параметров и запуск процесса моделирования.

Запуск процесса моделирования производится нажатием кнопки Start.

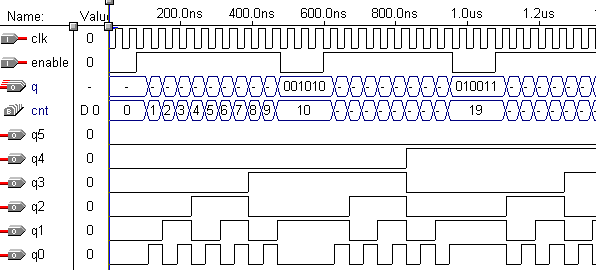

Нажатием кнопки Open SCF процесс моделирования завершается и на экране возникает форма редактора, на которой отображены не только воздействия, но и результаты работы устройства (см. рис. 3.8).

Рис. 3.8. Результаты моделирования

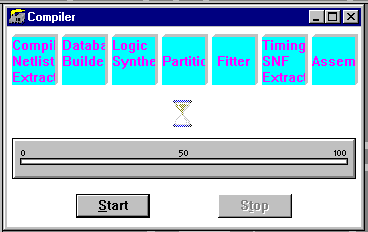

1.4 Размещение проекта в ПЛИС

После ввода проекта проводится компиляция, во время которой на экран выдается окно (см. рис. 3.9), в котором отражаются все этапы компиляции и размещения проекта в микросхему. Во время компиляции происходит размещение проекта в ПЛИС, при этом формируется отчет, в котором отражены результаты размещения, временные характеристики и другие данные.

Рис. 3.9. Компиляция проекта

Результаты использования ресурсов микросхемы отражены в следующих строках:

Chip/ Input Output Bidir LCs

POF Device Pins Pins Pins LCs % Utilized

EPF8282ALC84-2 2 6 0 8 3%

User Pins: 2 6 0

Из приведенного фрагмента видно, что используется ПЛИС EPF8282ALC84‑2, в схеме задействованы два входных контакта (Input Pins), 6 выходных контактов (Output Pins) и восемь логических ячеек (LCs). В отчете также приводится распределение занятых ячеек по столбцам и строкам. В нижеприведенном фрагменте показано, что все занятые ячейки расположены в первом столбце в строке В.

Logic Cell Counts

Column: 01 02 03 04 . . . 11 12 13 Total

A: 0 0 0 0 . . . 0 0 0 0

B: 8 0 0 0 . . . 0 0 0 8

Total: 8 0 0 0 . . . 0 0 0 8

Информация о распределении сигналов по контактам выглядит следующим образом:

Pin Primitive Code INP FBK OUT FBK Name

12 INPUT G 0 0 0 0 clk

73 INPUT 0 0 0 6 enable

22 OUTPUT 0 1 0 0 q0

27 OUTPUT 0 1 0 0 q1

62 OUTPUT 0 1 0 0 q2

61 OUTPUT 0 1 0 0 q3

56 OUTPUT 0 1 0 0 q4

58 OUTPUT 0 1 0 0 q5

Из приведенного фрагмента видно, что синхросигнал является глобальным сигналом и поступает на контакт с номером 12, разрешающий сигнал enable подается на контакт с номером 12, выходные сигналы q5 . . . q0 вырабатываются на контактах 22, 27. 62, 61, 56, 58. В отчете приводится также и другая информация, в том числе об использовании связей в ПЛИС.

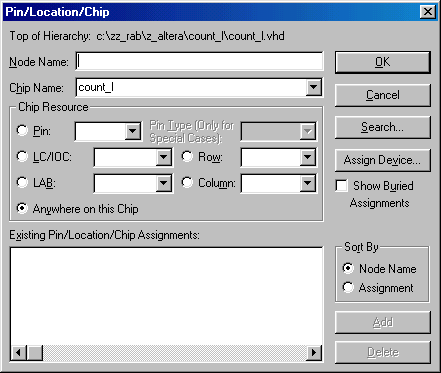

Распределение внешних сигналов по контактам может быть задано проектировщиком до начала компиляции. Для этого из основного окна САПР MAX+PLUS II надо выполнить следующую последовательность команд: Assign Þ Pin/Location/Chip.

Информация о временных задержках может быть получена с помощью программы Timing Analyzer. Для просмотра плана микросхемы можно использовать программу Floorplan Editor.

1.5 Разработка пересчетных схем

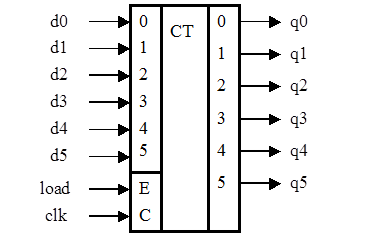

Шестиразрядный счетчик с синхронной загрузкой

Разрабатываемый счетчик (см. рис. 4.1) срабатывает по переднему фронту синхросигнала clk, также, как и в предыдущей схеме. Входной сигнал load задается как обычный управляющий сигнал, причем “0” соответствует загрузке, выходной сигнал счетчика q[5/0] и загружаемое значение d[5/0] задаются как целые (integer) в диапазоне от 0 до 63 (range 0 to 63).

Рис. 3.10. Шестиразрядный счетчик синхронной загрузкой

Описание схемы на языке VHDL задается следующим образом:

library IEEE;

use IEEE.std_logic_1164.all;

entity count_l is

port( clk, ld : in STD_LOGIC;

в : in INTEGER range 0 to 63;

q : out INTEGER range 0 to 63);

end count_l;

architecture l of count_l is

begin

process (clk)

variable cnt: INTEGER range 0 to 63;

begin

if (clk'event and clk = '1') then

if ld = '0' then

cnt := d;

else cnt := cnt+1;

end if;

end if;

q <= cnt;

end process;

end l;

Ввод схемы и регистрация проекта производятся также, как описано выше в предыдущих разделах. В отличие от предыдущей схемы в данном проекте внешние контакты задаются до начала компиляции. Для этого последовательно выбираются пункты меню Assign Þ Pin/Location/Chip, в результате появляется следующее окно (см. рис. 3.11).

Рис. 3.11. Окно Pin/Location/Chip

В открывшемся окне надо нажать клавишу Search, чтобы открыть окно Search Node Database, котором нажимается клавиша List. В результате в окне Names in Database появится список внешних контактов, которые были описаны в интерфейсе entity count_l в исходном тексте. Если теперь нажать на нужный контакт, а потом на OK, то имя этого контакта появится в пункте Node Name окна Pin/Location/Chip, показанного на рис. 3.11. После этого в строке Pin вводится номер контакта микросхемы и нажимается клавиша Add, и в результате в окне Existing Pin/Location/Assignments появляется соответствующая запись. Имя сигнала в окне Node Name и номер контакта в окне Pin можно задавать вручную, не используя средства поиска.

Зададим входные сигналы d0 … d5 на контакты 13, 15, 16, 18, 19 и 20 соответственно. Синхросигнал clk пусть будет поступать контакт 12, сигнал управления ld – на контакт 21. Контакты 9, 8, 7, 6, 4 и 3 закрепим за выходными сигналами q0 … q5. Система САПР должна обеспечить указанное распределение, а в случае невозможности исполнения будут выдаваться соответствующие сообщения и предлагаться возможные варианты исправления.

После этого выполняется компиляция, по результатам которой формируется отчет, в котором, в частности будет указано общая загрузка ресурсов ПЛИС.

Chip/ Input Output LCs

POF Device Pins Pins LCs % Utilized

count_l EPF8282ALC84-2 8 6 10 4 %

User Pins: 8 6 0

В отчете приводятся также назначения контактов, сделанные пользователем, а также замены (если они есть). В отчете приводится также конструктивный вид микросхемы, фрагмент которого (левый верхний угол ПЛИС) показан на рис. 3.13. Из этого рисунка видно, что распределение сигналов в точности соответствует сделанным назначениям, там же показаны контакты питания и другие контакты специального назначения (в том числе контакты, используемые для загрузки конфигурации).

C

O R R R

N E E E

F S S S

_ ^ E E E

в D R R R

O C G V V V

N L q q q q N q q E E E

E K 0 1 2 3 в 4 5 в D в

--------------------------------------

/ 11 10 9 8 7 6 5 4 3 2 1 84

clk | 12

d0 | 13

+DATA0 | 14

d1 | 15

d2 | 16

VCCINT | 17

d3 | 18 EPF8282ALC84-2

d4 | 19

&d5 | 20

ld | 21

RESERVED | 22

RESERVED | 23

Рис. 3.12 Размещение внешних сигналов на контактах ПЛИС.

Анализируя загрузку логических ячеек, можно заметить, что используются ячейки только строки А (блоки А1 … А5), при этом наиболее загружен блок А3, в котором используются 3 ячейки. Эта информация отражена в следующих строках.

Logic Column Row

Array Interconnect Interconnect External

Block Logic Cells Driven Driven Clocks Interconnect

A1 1/8 (12%) 1/8(12%) 1/8(12%) 1/2 2/24( 8%)

A2 1/8 (12%) 1/8(12%) 1/8(12%) 1/2 3/24( 12%)

A3 5/8 (62%) 1/8(12%) 3/8(37%) 1/2 6/24( 25%)

A4 1/8 (12%) 1/8(12%) 1/8(12%) 1/2 3/24( 12%)

A5 1/8 (12%) 1/8(12%) 1/8(12%) 1/2 3/24( 12%)

A6 1/8 (12%) 1/8(12%) 0/8(0%) 1/2 3/24( 12%)

Результаты размещения можно просмотреть также в программе Floorplan Editor (см. рис. 3.13)

Рис. 3.13 Размещение проекта в ПЛИС

На рис. 3.14. показан пример моделирования работы счетчика. Возмущающие воздействия и результат моделирования отображены в окне графического редактора Wave Editor.

Рис. 3.14. Моделирование работы счетчика с синхронной загрузкой.

Шестиразрядный реверсивный счетчик на ПЛИС типа CPLD

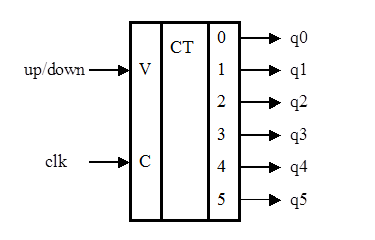

Работу шестиразрядного реверсивного счетчика (см. рис. 3.15) синхронизирует синхросигнал clk, входной сигнал up_down задает направление счета, причем “1” соответствует прямому счету, все остальные значения – обратному. Выходной сигнал счетчика q задается как целое в диапазоне от 0 до 63.

Рис. 3.15. Реверсивный счетчик

Описание устройства задается следующим текстом на языке VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

entity count_r is

port(clk : in STD_LOGIC;

up_down : in STD_LOGIC;

q : out INTEGER range 0 to 63);

end count_r;

architecture r of count_r is

begin

process (clk)

variable cnt: INTEGER range 0 to 63;

variable direction : INTEGER;

begin

if (up_down = '1') then

direction := 1;

else

direction := -1;

end if;

if (clk'event and clk = '1') then

cnt := cnt + direction;

end if;

q <= cnt;

end process;

end r;

В данном описании, как и в предыдущих, используется переменная cnt, значение которой при приостановке процесса присваивается выходному сигналу q.

На рис. 4.6. показан пример моделирования работы счетчика.

Рис. 3.16. Моделирование работы реверсивного счетчика.

Для реализации выберем ПЛИС типа CPLD EPM7032LC44-6 семейства MAX7000.

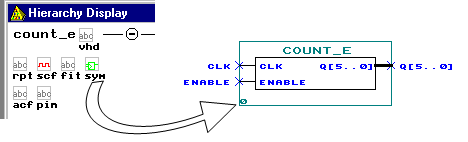

1.6 Создание символа

Часто на практике бывает так, что разрабатываемое устройство является частью более сложного проекта – корневого проекта (top project). Как правило, корневой проект является графическим, поэтому и нашу разработку следует представить в графическом виде – в виде модуля или “символа”, а затем этот символ перенести в корневой проект. Последовательность действий может быть такая: создание символа (см. рис. 3.17) и просмотр символа (см. рис. 3.18).

Рис. 3.17. Создание символа.

Рис. 3.18. Просмотр символа

Литература

1. Стешенко В. Б. ПЛИС фирмы ALTERA: проектирование устройств обработки сигналов. - М.: ДОДЭКА. 2000.

|