Проверка условия, цикл с дополнительным условием

СОДЕРЖАНИЕ

Введение 3

1 Организация памяти в ЭВМ 4

1.1 Концепция многоуровневой памяти 4

1.2 Сверхоперативная память 6

1.2.1 СОЗУ с прямым доступом 8

1.2.2 СОЗУ с ассоциативным доступом 8

.3 Виртуальная память 12

1.3.1 Алгоритмы замещения 14

.3.2 Сегментная организация памяти 16

2 Расчетно-графическое задание 18

2.1 Задание №1 19

2.2 Задание №2 21

3 Тестирование 23

3.1 Тестирование задания №1 23

3.2 Тестирование задания №2 25

Заключение 26

Библиографический список 27

ВВЕДЕНИЕ

Язык ассемблера (англ. assembly language) —машинно-ориентированный язык низкого уровня с командами, обычно соответствующими командам машины, который может обеспечить дополнительные возможности вроде макрокоманд; автокод, расширенный конструкциями языков программирования высокого уровня, такими как выражения, макрокоманды, средства обеспечения модульности программ.

Автокод —язык программирования, предложения которого по своей структуре в основном подобны командам и обрабатываемым данным конкретного машинного языка.

Язык ассемблера —система обозначений, используемая для представления в удобочитаемой форме программ, записанных в машинном коде. Язык ассемблера позволяет программисту пользоваться алфавитными мнемоническими кодами операций, по своему усмотрению присваивать символические имена регистрам ЭВМ и памяти, а также задавать удобные для себя схемы адресации (например, индексную или косвенную). Кроме того, он позволяет использовать различные системы счисления (например, десятичную или шестнадцатеричную) для представления числовых констант и даёт возможность помечать строки программы метками с символическими именами с тем, чтобы к ним можно было обращаться (по именам, а не по адресам) из других частей программы (например, для передачи управления).

Перевод программы на языке ассемблера в исполнимый машинный код (вычисление выражений, раскрытие макрокоманд, замена мнемоник собственно машинными кодами и символьных адресов на абсолютные или относительные адреса) производится ассемблером —программой-транслятором, которая и дала языку ассемблера его название.

Команды языка ассемблера один к одному соответствуют командам процессора. Фактически, они и представляют собой более удобную для человека символьную форму записи —мнемокоды —команд и их аргументов. При этом одной команде языка ассемблера может соответствовать несколько вариантов команд процессора.

Кроме того, язык ассемблера позволяет использовать символические метки вместо адресов ячеек памяти, которые при ассемблировании заменяются на вычисляемые ассемблером или компоновщиком абсолютные или относительные адреса, а также так называемые директивы (команды ассемблера, не переводимые в машинные команды процессора, а выполняемые самим ассемблером).

Директивы ассемблера позволяют, в частности, включать блоки данных, задать ассемблирование фрагмента программы по условию, задать значения меток, использовать макрокоманды с параметрами.

Каждая модель (или семейство) процессоров имеет свой набор —систему —команд и соответствующий ему язык ассемблера. Наиболее популярные синтаксисы языков ассемблера —Intel-синтаксис и AT&T-синтаксис.

Существуют компьютеры, реализующие в качестве машинного язык программирования высокого уровня (Форт, Лисп, Эль-76). Фактически, в таких компьютерах они выполняют роль языков ассемблера.

1 ОРГАНИЗАЦИЯ ПАМЯТИ В ЭВМ

ЭВМ, реализованная по классической фон-неймановской архитектуре, включает в себя:

- процессор, содержащий арифметико-логическое устройство (АЛУ) и центральное устройство управления (ЦУУ);

- память, которая в современных ЭВМ подразделяется на оперативную (ОП или ОЗУ) и сверхоперативную (СОЗУ);

- внешние устройства, к которым относят внешнюю память (ВЗУ) и устройства ввода/вывода (УВВ).

1.1 Концепция многоуровневой памяти

Известно, что память ЭВМ предназначена для хранения программ и данных, причем эффективность работы ЭВМ во многом определяется характеристиками ее памяти. Во все времена к памяти предъявлялись три основных требования: большой объем, высокое быстродействие и низкая (умеренная) стоимость.

Все перечисленные выше требования к памяти являются взаимно-противоречивыми, поэтому пока невозможно реализовать один тип ЗУ, отвечающий всем названным требованиям. В современных ЭВМ организуют комплекс разнотипных ЗУ, взаимодействующих между собой и обеспечивающих приемлемые характеристики памяти ЭВМ для каждого конкретного применения.

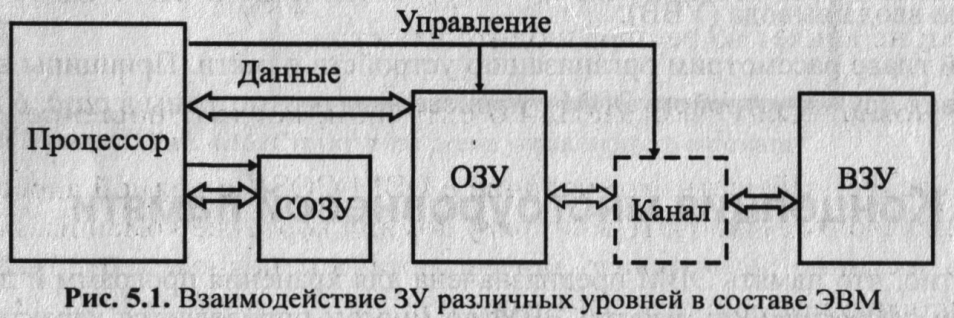

В основе большинства ЭВМ лежит трехуровневая организация памяти: сверхоперативная (СОЗУ) —оперативная (ОЗУ) —внешняя (ВЗУ). СОЗУ и ОЗУ могут непосредственно взаимодействовать с процессором, ВЗУ взаимодействует только с ОЗУ.

СОЗУ обладает максимальным быстродействием (равным процессорному), небольшим объемом (101—5 байтов) и располагается, как правило, на кристалле процессорной БИС. Для обращения к СОЗУ не требуются магистральные (машинные) циклы. В СОЗУ размещаются наиболее часто используемые на данном участке программы данные, а иногда —и фрагменты программы.

Быстродействие ОЗУ может быть ниже процессорного (не более чем на порядок), а объем составляет 106—9 байтов. В ОЗУ располагаются подлежащие выполнению программы и обрабатываемые данные. Связь между процессором и ОЗУ осуществляется по системному или специализированному интерфейсу и требует для своего осуществления машинных циклов.

Информация, находящаяся в ВЗУ, не может быть непосредственно использована процессором. Для использования программ и данных, расположенных в ВЗУ, их необходимо предварительно переписать в ОЗУ. Процесс обмена информацией между ВЗУ и ОЗУ осуществляется средствами специального канала или (реже)—непосредственно под управлением процессора. Объем ВЗУ практически неограничен, а быстродействие на 3—порядков ниже процессорного.

Рисунок 1 –Взаимодействие между процессором и уровнями памяти

Следует помнить, что положение ЗУ в иерархии памяти ЭВМ определяется не элементной базой запоминающих ячеек (известны случаи реализации ВЗУ на БИС —"электронный диск" и, наоборот, организация оперативной памяти на электромеханических ЗУ —магнитных барабанах), а возможностью доступа процессора к данным, расположенным в этом ЗУ.

При организации памяти современных ЭВМ (МПС) особое внимание уделяется сверхоперативной памяти и принципам обмена информацией между ОЗУ и ВЗУ.

1.2 Сверхоперативная память

Применение СОЗУ в иерархической памяти ЭВМ может обеспечить повышение производительности ЭВМ за счет снижения среднего времени обращения к памяти Т при условии, что время цикла СОЗУ Тс будет (значительно) меньше времени цикла ОЗУ Т0. Очевидно:

Т = рс*Тс+(1-рс)*Т0 (1.1)

где рс —вероятности обращения к СОЗУ. Обозначим так же: р0 —вероятности обращения к ОЗУ.

Из (1.1) следует, что повышение производительности ЭВМ может осуществляться двумя путями:

- уменьшением отношения

- увеличением вероятности рс обращения в СОЗУ.

Первый путь связан, прежде всего, с технологическими особенностями производства БИС и здесь не рассматривается.

Если считать, что информация размещается в СОЗУ и ОЗУ случайным образом, то вероятности рс и р0 пропорциональны объемам соответствующих ЗУ. В этом случае рс << р0 и наличие в ЭВМ СОЗУ практически не влияет на ее производительность.

То же можно было бы сказать и о ситуации, когда отношение  1, но не следует забывать, что наличие в ЭВМ СОЗУ с прямой адресацией (РОН) позволяет включать в систему команд короткие команды, использовать косвенно-регистровую адресацию и, в конечном итоге, увеличивать производительность ЭВМ даже при Тс = Т0.

1, но не следует забывать, что наличие в ЭВМ СОЗУ с прямой адресацией (РОН) позволяет включать в систему команд короткие команды, использовать косвенно-регистровую адресацию и, в конечном итоге, увеличивать производительность ЭВМ даже при Тс = Т0.

Итак, для эффективного применения СОЗУ следует таким образом распределять информацию по уровням памяти ЭВМ, чтобы в СОЗУ всегда располагались наиболее часто используемые в данный момент коды.

Принято различать СОЗУ по способу доступа к хранимой в нем информации. Известны два основных класса СОЗУ по этому признаку:

- с прямым доступом;

- с ассоциативным доступом.

1.2.1 СОЗУ с прямым доступом

СОЗУ с прямым доступом (РОН —регистры общего назначения) получило широкое распространение в большинстве современных ЭВМ. Фактически РОН —это небольшая регистровая намять, доступ к которой осуществляется специальными командами. Стратегия размещения данных в РОН целиком определяется программистом (компилятором). Обычно в РОН размещают многократно используемые адреса (базы, индексы), счетчики циклов, данные активного фрагмента задачи, что повышает вероятность обращения в ячейки РОН по сравнению с ячейками ОЗУ.

1.2.2 СОЗУ с ассоциативным доступом

Применение СОЗУ с ассоциативным доступом позволяет автоматизировать процесс размещения данных в СОЗУ, обеспечивая "подмену" активных в данный момент ячеек ОЗУ ячейками СОЗУ. Эффективность такого подхода существенно зависит от выбранной стратегии замены информации в СОЗУ, причем использование ассоциативного СОЗУ имеет смысл только при условии Тс <<T0.

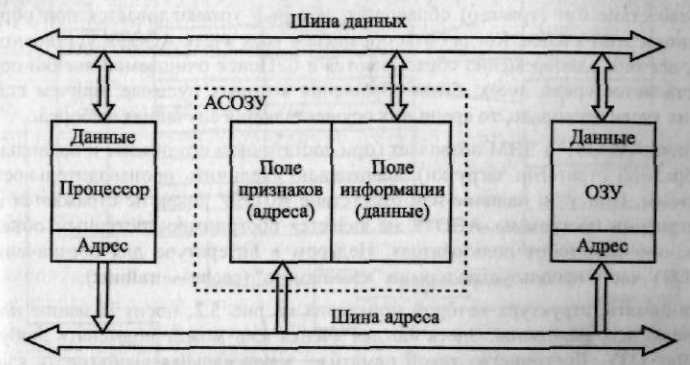

Принцип ассоциативного доступа состоит в следующем. Накопитель ассоциативного запоминающего устройства (АЗУ) разбит на два поля—информационное и признаков. Структура информационного поля накопителя соответствует структуре обычного ОЗУ, а запоминающий элемент поля признаков, помимо функции записи, чтения и хранения бита, обеспечивает сравнение хранимой информации с поступающей и выдачу признака равенства.

Признаки равенства всех элементов одной ячейки поля признаков объединяются по "И" и устанавливают в 1 индикатор совпадения ИС, если информация, хранимая в поле признака ячейки, совпадает с информацией, подаваемой в качестве признака на вход Р накопителя.

Во второй фазе обращения (при чтении) на выход данных D последовательно поступает содержимое информационных полей тех ячеек, индикаторы совпадения которых установлены в 1 (если таковые найдутся).

Способ использования АЗУ в качестве сверхоперативного иллюстрирует рис. 2. В информационном поле ячеек АСОЗУ—копия информации некоторых ячеек ОЗУ, а в поле признаков —адреса этих ячеек ОЗУ. Когда процессор генерирует обращение к ОЗУ, он одновременно (или прежде) инициирует процедуру опроса АСОЗУ, выдавая в качестве признака адрес ОЗУ. Если имеет место совпадение признака ячейки с запрашиваемым адресом (не более одного раза, алгоритм загрузки АСОЗУ не предусматривает возможности появления одинаковых признаков), то процессор обращается (по чтению или по записи) в информационное поле этой ячейки АСОЗУ, при этом блокируется обращение к ОЗУ. Если требуемый адрес не найден в АСОЗУ, инициируется (или продолжается) обращение к ОЗУ, причем в АСОЗУ создается копия ячейки ОЗУ, к которой обратился процессор. Повторное обращение процессора по этому адресу будет реализовано в АСОЗУ (на порядок быстрее, чем в ОЗУ).

Рисунок 2 –СОЗУ с ассоциативным доступом

Таким образом, в АСОЗУ создаются копии тех ячеек ОЗУ, к которым в данный момент обращается процессор в надежде, что "в ближайшее время" произойдет новое обращение по этому адресу. (Существуют и другие стратеги загрузки АСОЗУ, например, если процессор обращается в ОЗУ по определенному адресу, то в АСОЗУ перемещается содержимое целого блока соседних ячеек.)

При необходимости записи в АСОЗУ новой информации требуется отыскать свободную ячейку, а при ее отсутствии (что чаще всего и бывает) —отыскать ячейку, содержимое которой можно удалить из АСОЗУ. При этом следует помнить, что если во время пребывания ячейки в АСОЗУ в нее производилась запись, то требуется не просто очистить содержимое ячейки, а записать его в ОЗУ по адресу, хранящемуся в поле признаков, т. к. процессор, отыскав адрес в АСОЗУ, производит запись только туда, оставляя в ОЗУ старое значение (т. н. "АСОЗУ с обратной записью"). Возможен и другой режим работы СОЗУ —со сквозной записью, при котором всякая запись осуществляется СОЗУ, и в ОЗУ.

При поиске очищаемой ячейки чаще всего используют метод случайного в бора. Иногда отмечают ячейки, в которые не проводилась запись, и пои "кандидата на удаление" проводят из них.

Более сложная процедура замещения предполагает учет длительности пребывания ячеек в АСОЗУ, или частоты обращения по этому адресу, или времени с момента последнего обращения. Однако все эти методы требуют дополнительных аппаратных и временных затрат.

Одним из наиболее дешевых способов, позволяющих учитывать поток обращений к ячейкам, является следующий. Каждой ячейке АСОЗУ ставится в соответствие бит (триггер) обращения, который устанавливается при обращении к этой ячейке. Когда биты обращения всех ячеек АСОЗУ установятся в 1, все они одновременно сбрасываются в 0. Поиск очищаемой ячейки осуществляется среди ячеек, биты обращения которых нулевые, причем если таких ячеек несколько, то среди них осуществляется случайная выборка.

Наличие АСОЗУ в ЭВМ позволяет (при достаточном его объеме и правильно выбранной стратегии загрузки) значительно увеличить производительность системы. При этом наличие или отсутствие АСОЗУ никак не отражается на построении программы. АСОЗУ не является программно-доступным объектом, оно скрыто от пользователя. Недаром в литературе для обозначения АСОЗУ часто используется термин "кэш-память" (cache —тайник).

Кэш-память, структура которой приведена на рис. 3, носит название полностью ассоциативной. Здесь каждая ячейка кэш может подменять любую ячейку ОЗУ. Достоинство такой памяти —максимальная вероятность кэш-попадания (при прочих равных условиях), по сравнению с другими способами организации кэш. К недостаткам можно отнести сложность ее структуры (а следовательно, и высокую стоимость). Действительно, в каждом разряде поля признаков необходимо реализовать, наряду с возможностями записи и хранения, функцию сравнения хранимого бита с соответствующим битом признака, а потом конъюнкцию результатов сравнения разрядов в каждой ячейке.

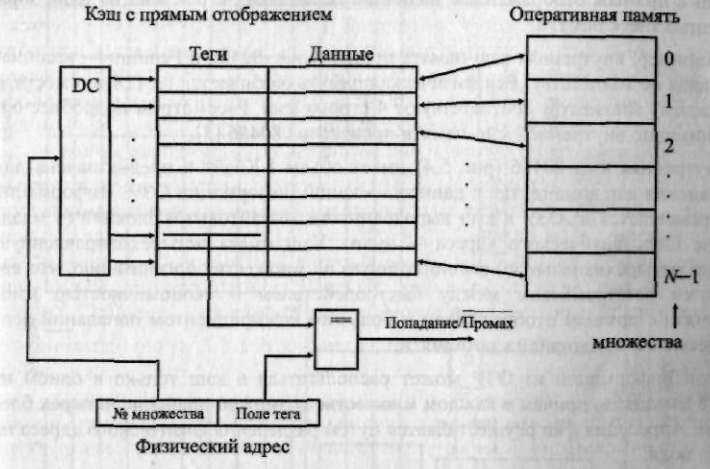

Кэш-память с прямым отображением требует минимальных затрат оборудования (по сравнению с другими вариантами организации кэш), но имеет минимальную вероятность кэш-попаданий. Суть организации (рис. 3) состоит в следующем. Физическая оперативная намять разбивается на блоки (множества) одинакового размера, количество которых (блоков) соответствует числу ячеек кэш, причем каждой строке ставится в соответствие определенное множество ячеек памяти, не пересекающееся с другими. Все ячейки множества претендуют на одну строку кэш.

Такая организация кэш исключает собственно ассоциативный поиск, а следовательно, значительно упрощается схема ячейки поля признаков. Действительно, здесь копия требуемой ячейки оперативной памяти может располагаться в единственной строке кэш. Часть физического адреса (на рис. 3 —старшая) определяет номер множества и, следовательно, строку кэш. Содержимое этой строки выбирается по обычному адресному принципу, и поле тега сравнивается с младшей частью физического адреса. Таким образом, для всей кэш-памяти (любого размера) достаточно единственной схемы сравнения.

Рисунок 3 –Кэш с прямым отображением

Однако предложенная выше структура имеет существенный недостаток. Если проводить разбиение памяти на множества, как показано на рис. 3, то в большинстве случаев кэш будет использоваться крайне неэффективно. Во-первых, хотя адресное пространство физической памяти 32-разрядных микропроцессоров составляет 232 байтов, в современных ПЭВМ обычно используют намять объемом 225 —29 байтов. Следовательно, строки кэш, отображаемые на старшие (физически отсутствующие) множества памяти, никогда не будут использованы.

Во-вторых, если в множества включать следующие подряд ячейки ОЗУ, то копии никаких двух последовательных ячеек ОЗУ нельзя одновременно иметь в кэш (кроме случая последней и первой ячеек двух соседних множеств), что противоречит одной из основополагающих стратегий загрузки кэш —целесообразности копирования в кэш группы последовательных ячеек ОЗУ.

Для исключения отмеченных недостатков разбиение ячеек памяти на множества осуществляется таким образом, чтобы соседние ячейки относились к разным множествам, что достигается размещением поля номера множества не в старших, а в младших разрядах физического адреса.

Для дальнейшего увеличения вероятности кэш-попаданий можно реализовать вариант кэш-памяти, ассоциативной по множеству, которая отличается от кэш с прямым отображением наличием нескольких строк кэш на одно множество ячеек памяти.

1.3 Виртуальная память

Выше были рассмотрены способы организации сверхоперативной памяти и ее взаимодействия с оперативной. Не менее, а порой и более важной проблемой является организация взаимодействия в паре ОЗУ —ВЗУ.

Известно, что в современных ЭВМ (кроме простейших) реализовано динамическое распределение памяти между несколькими задачами, существующими в ЭВМ в процессе решения. Даже для однозадачных конфигураций проблема динамического распределения памяти не теряет актуальности, т. к. в памяти, помимо задачи пользователя, всегда присутствует операционная система или ее фрагмент.

Наличие динамического распределения памяти предполагает, что программа компилируется в т. н. "логических" адресах, а в процессе работы происходит автоматическое преобразование логических адресов в физические.

Наибольшее распространение в ЭВМ получил метод динамического распределения памяти, называемый страничной организацией виртуальной памяти. При использовании этого метода вся память ЭВМ (ОЗУ и ВЗУ) рассматривается как единая виртуальная память. Адрес в этой памяти называется виртуальным или логическим. Вся виртуальная память делится на фрагменты одинакового размера, называемые виртуальными страницами. Размер страницы обычно составляет 0,5—Кбайт. Виртуальный адрес представляется состоящим из двух частей—номера страницы и номера слова на странице (смещения).

Физическая память ЭВМ (ОЗУ и ВЗУ) так же делится на страницы, причем размер физической страницы выбирается равным размеру виртуальной. Таким образом, одна физическая страница может хранить одну виртуальную, причем порядок следования виртуальных страниц в программе совсем не обязательно сохранять на физических страницах. Достаточно лишь установить однозначное соответствие между номерами виртуальных и физических страниц.

Соответствие между номерами виртуальных и физических страниц устанавливается с помощью специальной страничной таблицы (СТ), которую поддерживает операционная система. Размер физической страницы равен размеру виртуальной, поэтому преобразования смещений на странице не производятся.

Поскольку размер СТ достаточно велик, она хранится целиком в ОЗУ и модифицируется операционной системой всякий раз, когда в распределении памяти происходят изменения.

Для увеличения скорости обращения к памяти активная часть СТ обычно хранится в специальной быстродействующей памяти, организованной, как правило, по ассоциативному принципу. При этом в поле признаков АЗУ СТ хранятся виртуальные адреса страниц (иногда вместе с номером программы —в мультипрограммных системах), а в информационной части —соответствующие им номера физических страниц.

Если в результате преобразования виртуального адреса в физический оказывается, что требуемая физическая страница располагается в ВЗУ, то выполнение программы становится невозможным, пока не произойдет "подкачка" требуемой страницы в ОЗУ. Такая ситуация называется страничным сбоем и должна формировать внутреннее прерывание, по которому запускается подпрограмма чтения страницы из ВЗУ в ОЗУ.

При этом возникает серьезная проблема поиска той страницы, которую можно удалить из ОЗУ, чтобы на освободившееся место записать требуемую страницу. Серьезность проблемы обусловлена тем, что неудачный выбор удаляемой страницы (в ближайшее время она вновь понадобится) связан со значительной потерей времени на передачу страниц между ОЗУ и ВЗУ.

1.3.1 Алгоритмы замещения

Правило, по которому при возникновении страничного сбоя выбирается страница для удаления из ОЗУ, называется алгоритмом замещения. Для данной программы, порождающей некоторый поток обращений к памяти, существует, по крайней мере, одна такая последовательность замещений страниц, которая дает для этой программы минимальное количество страничных сбоев.

Теоретически доказано, что минимальное число страничных сбоев будет получено, если в алгоритме замещения использовать информацию о потоке обращений к страницам в будущем (алгоритм Минховского —Шора) или, по крайней мере, о вероятности обращений к страницам в будущем. Алгоритмы замещения, использующие "информацию о будущем", называются физически нереализуемыми, их обычно применяют для оценки качества эвристических алгоритмов замещения.

Эвристические алгоритмы замещения используют информацию о потоке обращений к страницам в прошлом (историю процесса) для экстраполяции характеристик потока обращений в будущем. Как правило, используют три типа информации о прошлом: время пребывания страницы в ОЗУ (или, что то же—очередность поступления страниц), число обращений к страницам за определенный промежуток времени или отрезки времени с момента последнего обращения к страницам.

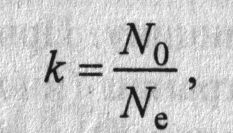

Эффективность эвристического алгоритма можно характеризовать отношением(рис.4):

Рисунок 4 –Эффективность эвристического алгоритма

где N0 —число страничных сбоев при решении данной задачи с применением физически нереализуемого алгоритма; Ne —то же с применением исследуемого эвристического алгоритма.

Эвристический алгоритм можно считать выбранным удачно (для данного класса задач), если коэффициент к близок к 1. Значение NQ может быть получено путем моделирования решения задачи (повторное) с предварительно зафиксированным потоком обращений к страницам.

При выборе подходящего алгоритма замещения следует учитывать не только его эффективность , но и аппаратные затраты и затраты времени на его реализацию.

Например, для реализации т. н. НДИ-алгоритма (наиболее давно используемая) каждой странице, находящейся в ОЗУ, ставится в соответствие таймер, который сбрасывается при обращении к странице. При страничном сбое необходимо осуществить поиск максимального элемента массива таймеров страниц. Для некоторых задач выигрыш времени за счет увеличения к при применении НДИ-алгоритма, по сравнению с алгоритмом случайного замещения, может быть сравним с потерей времени на поиск максимальных значений таймеров.

Некоторые алгоритмы замещения учитывают одновременно несколько параметров прошлого потока обращений.

Алгоритм "Карабкающаяся страница" (КС-алгоритм) поддерживает последовательность номеров страниц, находящихся в ОЗУ. При любом обращении к странице ее номер в последовательности перемещается на одну позицию в направлении начала, меняясь местами с предыдущим в последовательности номером (исключение —обращение к странице, номер которой стоит в начале последовательности). При возникновении страничного сбоя из ОЗУ удаляется страница, номер которой расположен в конце

последовательности, а номер вновь поступившей страницы помещается в конец последовательности. КС-алгоритм учитывает как время пребывания страницы в ОЗУ, так и интенсивность обращения к странице, причем не требует значительных аппаратных затрат, а при страничном сбое —времени на поиск.

Алгоритм "Рабочий комплект" (РК-алгоритм) более сложен в реализации, но позволяет адаптировать свои параметры под конкретный класс задач. Все страницы ОЗУ, к которым было обращение в течение отрезка времени Т, образуют т. н. рабочий комплект и не подлежат удалению из ОЗУ. Остальные страницы (не вошедшие в рабочий комплект) образуют две очереди кандидатов на замещение, причем в первую очередь попадают страницы, на которые не было записи во время пребывания их в ОЗУ. При страничном сбое удаляется страница из первой очереди (FIFO —первый пришел из рабочего комплекта —первый ушел из ОЗУ), а если первая очередь пуста, то —из второй. Из очереди страница может опять попасть в рабочий комплект, если к ней будет обращение. Для реализации РК-алгоритма каждой странице ставится в соответствие таймер на Т, причем каждое обращение к странице сбрасывает таймер (и переводит страницу в рабочий комплект, если она там отсутствовала), а переполнение таймера выводит страницу из рабочего комплекта. Подбором величины Т можно оптимизировать РК-алгоритм под конкретный класс задач.

1.3.2 Сегментная организация памяти

До сих пор предполагалось, что виртуальная память, которой располагает программист, представляет собой непрерывный массив с единой нумерацией слов. Однако при написании программы удобно располагать несколькими независимыми сегментами (кода, данных, подпрограмм, стека и др.), причем размеры сегментов, как правило, заранее не известны. В каждом сегменте слова нумеруются с нуля независимо от других сегментов. В этом случае виртуальный адрес представляется состоящим из трех частей: <номер сегмента> <номер страницы> <номер слова>. В машине к виртуальному адресу может добавиться слева еще <номер задачи>. Таким образом, возникает определенная иерархия полей виртуального адреса, которой соответствует иерархия таблиц, с помощью которых виртуальный адрес переводится в физический. В конкретных системах может отсутствовать тот или иной элемент иерархии.

Виртуальная память была первоначально реализована на "больших" ЭВМ, однако по мере развития микропроцессоров в них так же использовались идеи страничной и сегментной организации памяти.

2 РАСЧЕТНО-ГРАФИЧЕСКОЕ ЗАДАНИЕ

2.1 Описание среды разработки

Моделируемая ЭВМ включает процессор, оперативную (ОЗУ) и сверхоперативную память, устройство ввода (УВв) и устройство вывода (УВыв). Процессор, в свою очередь, состоит из центрального устройства управления (УУ), арифметического устройства (АУ) и системных регистров (CR, PC, SP и др.)

В ячейках ОЗУ хранятся команды и данные. Емкость ОЗУ составляет 1000 ячеек. По сигналу MWr выполняется запись содержимого регистра данных (MDR) в ячейку памяти с адресом, указанным в регистре адреса (MAR). По сигналу MRd происходит считывание –содержимое ячейки памяти с адресом, содержащимся в MAR, передается в MDR.

Сверхоперативная память с прямой адресацией содержит десять регистров общего назначения R0-R9. Доступ к ним осуществляется (аналогично доступу к ОЗУ) через регистры RAR и RDR.

АУ осуществляет выполнение одной из арифметических операций, определяемой кодом операции (COP), над содержимым аккумулятора (Acc) и регистра операнда (DR). Результат операции всегда помещается в Acc. При завершении выполнения операции АУ вырабатывает сигналы признаков результата: Z (равен 1, если результат равен нулю); S (равен 1, если результат отрицателен); OV (равен 1, если при выполнении операции произошло переполнение разрядной сетки). В случаях, когда эти условия не выполняются, соответствующие сигналы имеют нулевое значение.

В модели ЭВМ предусмотрены внешние устройства двух типов. Во-первых, это регистры IR и OR, которые могут обмениваться с аккумулятором с помощью безадресных команд IN (Acc:=IR) и OUT (OR:=Acc). Во-вторых, это набор моделей внешних устройств, которые могут подключаться к системе и взаимодействовать с ней в соответствии с заложенными в моделях алгоритмами. Каждое внешнее устройство имеет ряд программно-доступных регистров, может иметь собственный обозреватель (окно видимых элементов).

УУ осуществляет выборку команд из ОЗУ в последовательности, определяемой естественным порядком выполнения команд (т.е. в порядке возрастания адресов команд в ОЗУ) или командами передачи управления; выборку из ОЗУ операндов, задаваемых адресами команды; инициирование выполнения операции, предписанной командой; останов или переход к выполнению следующей команды.

2.2 Задание №1

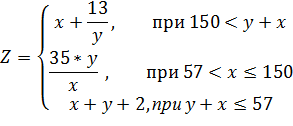

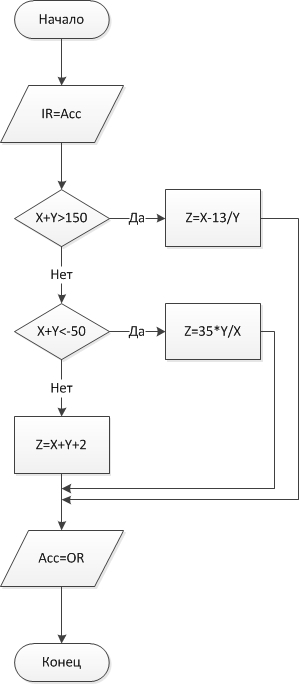

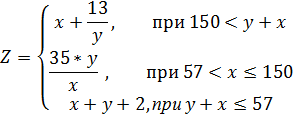

Система уравнений:

Блок-схема алгоритма решения задачи:

Рисунок 3 –Блок-схема программы

Таблица 1 – Размещение данных в ОЗУ

|

x

|

000

|

|

|

|

|

|

|

|

|

|

|

00

|

010000

|

220041

|

230040

|

220042

|

440000

|

000150

|

140015

|

130009

|

110021

|

210042

|

|

10

|

440000

|

000057

|

140021

|

130027

|

110027

|

410000

|

000013

|

260040

|

230041

|

020000

|

|

20

|

090000

|

410000

|

000035

|

260041

|

250040

|

020000

|

09000

|

210041

|

230040

|

430000

|

|

30

|

000002

|

020000

|

090000

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

|

40

|

000056

|

000100

|

000156

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

Таблица 2 –Листинг программы

|

Адрес

|

Команда

|

Примечание

|

|

Мнемокод

|

Код

|

|

000

|

in

|

010000

|

Считываем х

|

|

001

|

wr 41

|

220041

|

Размещение х в ОЗУ M(41)

|

|

002

|

add 40

|

230040

|

x+y

|

|

003

|

wr 42

|

220042

|

Запись в М(42)

|

|

004

|

sbi 150

|

440000

|

Расчет ограничения

|

|

005

|

|

000150

|

|

|

006

|

jns 15

|

140015

|

Переход, если положительно

|

|

007

|

js 9

|

130009

|

Переход, если отрицательно

|

|

008

|

jz 21

|

110021

|

Переход, если ноль

|

|

009

|

rd 42

|

210042

|

Чтение x+y

|

|

010

|

sbi 57

|

440000

|

Расчет ограничения

|

|

011

|

|

000057

|

|

|

012

|

jns 21

|

140021

|

Переход, если положительно

|

|

013

|

js 27

|

130027

|

Переход, если отрицательно

|

|

014

|

jz 27

|

110027

|

Переход, если ноль

|

|

015

|

rdi 13

|

410000

|

Расчет

|

|

016

|

|

000013

|

первого

|

|

017

|

div 40

|

260040

|

уравнения

|

|

018

|

add 41

|

230041

|

|

|

019

|

out

|

020000

|

Вывод

|

|

020

|

hlt

|

090000

|

Стоп

|

|

021

|

rdi 35

|

410000

|

Расчет

|

|

022

|

|

000035

|

вторго

|

|

023

|

div 41

|

260041

|

уравнения

|

|

024

|

mul 40

|

250040

|

|

|

025

|

out

|

020000

|

Вывод

|

|

026

|

hlt

|

090000

|

Стоп

|

|

027

|

rd 41

|

260041

|

Расчет

|

|

028

|

add 40

|

230040

|

первого

|

|

029

|

adi 2

|

430000

|

уравнения

|

|

030

|

|

000002

|

|

|

031

|

out

|

020000

|

Вывод

|

|

032

|

hlt

|

090000

|

Стоп

|

Результат выполнения программы:

При y=56,x=100; Z=100;

При y=56,x=10; Z=168;

При y=56,x=1; Z=58;

2.3 Задание №2

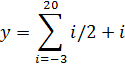

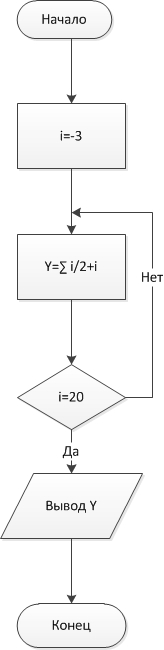

Уравнение:

Блок-схема алгоритма решения задачи:

Рисунок 4 –Блок-схема программы

Таблица 3 – Размещение данных в ОЗУ

|

x

|

000

|

|

|

|

|

|

|

|

|

|

|

00

|

212030

|

320000

|

261002

|

320004

|

310000

|

350000

|

330004

|

330002

|

320002

|

320003

|

|

10

|

210030

|

231001

|

220030

|

241040

|

130000

|

140016

|

310003

|

020000

|

090000

|

000000

|

|

20

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

|

30

|

000100

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

000000

|

|

…

|

|

|

|

|

|

|

|

|

|

|

|

100

|

|

100002

|

100001

|

000000

|

000001

|

000002

|

000003

|

000004

|

000005

|

000006

|

|

110

|

|

000008

|

000009

|

000010

|

000011

|

000012

|

000013

|

000014

|

000015

|

000016

|

|

120

|

|

000018

|

000019

|

000020

|

000000

|

000000

|

00000

|

000000

|

000000

|

000000

|

Таблица 2 –Текст программы

|

Адрес

|

Команда

|

Примечание

|

|

Мнемокод

|

Код

|

|

000

|

rd @30

|

212030

|

Считываем i

|

|

001

|

wr R0

|

320000

|

Записываем в R0

|

|

002

|

div #2

|

261002

|

i/2

|

|

003

|

wr R4

|

320004

|

Запись в R4

|

|

004

|

rd R0

|

310000

|

Чтение R0

|

|

005

|

mul R0

|

350000

|

i^2

|

|

006

|

add R4

|

330004

|

i^2+i

|

|

007

|

add R2

|

330002

|

(i^2+i)+0

|

|

008

|

wr R2

|

320002

|

Запись

|

|

009

|

wr R3

|

320003

|

|

|

010

|

rd 30

|

210030

|

Чтение М(30)

|

|

011

|

add #1

|

231001

|

+1

|

|

012

|

wr 30

|

220030

|

Запись в М(30)

|

|

013

|

sub #125

|

241040

|

-125

|

|

014

|

js 0

|

130000

|

Переход, если отрицательно

|

|

015

|

jns 16

|

140016

|

Переход, если ноль

|

|

016

|

rd R3

|

310003

|

Чтение R3

|

|

017

|

out

|

020000

|

Вывод

|

|

018

|

hlt

|

090000

|

Стоп

|

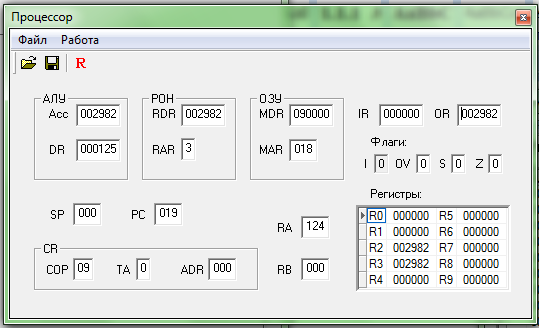

Результат выполнения программы:

Y= 2982

3 ТЕСТИРОВАНИЕ ПРОГРАММЫ

3.1 Тестирование задания №1

Система уравнений:

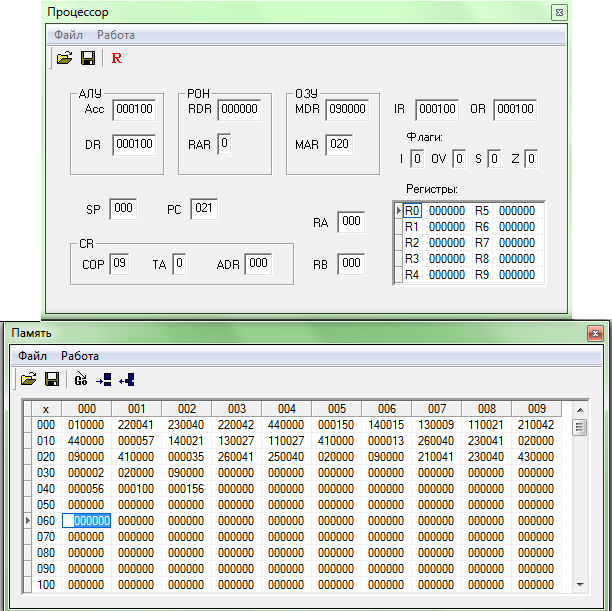

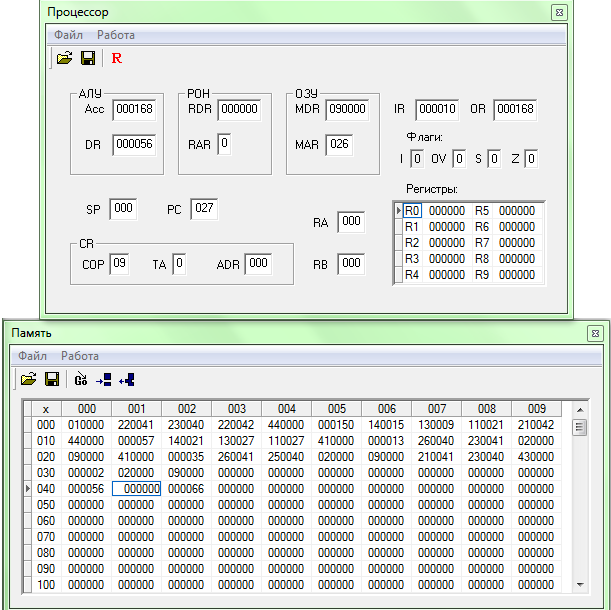

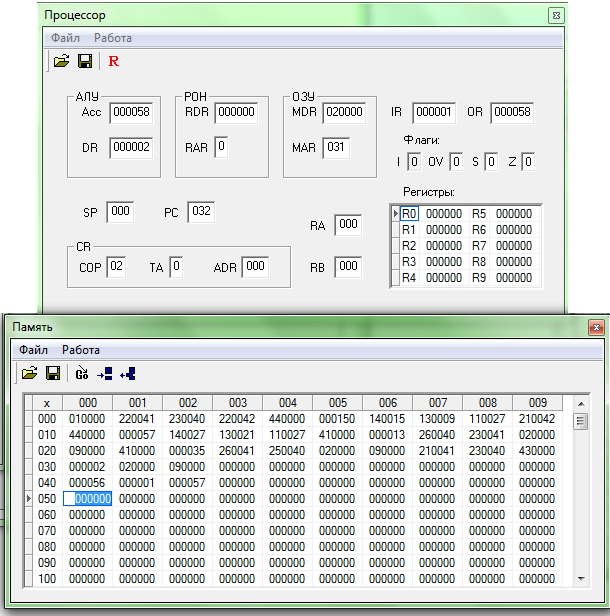

В ячейке памяти 40 хранится значение переменной Y, в ячейке 41 –значение X. При запуске программы на выполнение, содержимое ячейки помещается в аккумулятор и происходит сравнение переменных X и Y с областью определения функции. Также в ячейку 43 помещается сумма X и Y. В зависимости от значения переменных X и Y вычисляется соответствующая формула. Значение выводится в поле OR.

Результаты работы программы при разных значениях переменных:

Рисунок 5 –Результат выполнения программы при X=100, Y=56

Рисунок 6 –Результат выполнения программы при X=10, Y=56

Рисунок 7 –Результат выполнения программы при X=1, Y=56

3.2 Тестирование задания №2

Уравнение:

Рисунок 8 –Результат работы программы 2

Для вычисления значения этого выражения целесообразно использовать цикл для подсчета суммы. На каждом шаге цикла вычисляется значение выражения и умножается со значением выражения, вычисленным на предыдущем шаге цикла.

ЗАКЛЮЧЕНИЕ

В ходе выполнения курсовой работы было разработано две программы на упрощённом языке Assembler.

В данных программах были использованы: проверка условия, цикл с дополнительным условием.

Выполненные программы отлажены и работают правильно. Были учтены все граничные значения, в которых программа могла работать неправильно.

Также в ходе выполнения работы был изучен и освещён такой раздел как “Организация памяти в ЭВМ”. Раздел изложен в достаточно полном содержании и охватывает многие аспекты данной темы.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1 Библиотека MSDN [Электронный ресурс]. –Режим доступа : http://msdn.microsoft.com/ru-ru/library. –.05.2012

Жмакин А.П. Архитектура ЭВМ. –СПб.: БХВ-Петербург,2006. 320 с.

История AMD в процессорах [Электронный ресурс]. –Режим доступа: http://www.thg.ru/cpu/amd_cpu_history/. –.09.2012

Краткая история процессоров: 31 год из жизни архитектуры х86 [Электронный ресурс]. –Режим доступа : http://www.thg.ru/cpu/. –.01.2013

Пятнадцать процессоров Intel x86, вошедших в историю [Электронный ресурс]. –Режим доступа : http://www.compdoc.ru/comp/cpu/short-processor-x86-history/. –.08.2011

Таненбаум Э. Архитектура компьютера. 5-е изд. –СПб.: Питер, 2007. –с.

Уинн Л. Рош Библия по техническому обеспечению Уинна Роша . –СПб.: Москва, 2008,–с.

Форум программистов и сисадминов CyberForum.ru: [Электронный ресурс]. –Режим доступа : http://www.cyberforum.ru/. –.12.2012

Цилькер Б.Я., Орлов С.А. Организация ЭВМ и систем. –СПб.: Питер, 2008. –с.

Юров В.И. Assembler. –СПб.: Питер, 2005. –с.

|

|

|

|

|

|

КР.125026.230100.62.ПЗ

|

Лист

|

|

|

|

|

|

|

|

23

|

|

Изм.

|

Лист

|

№ докум.

|

Подп.

|

Дата

|

Проверка условия, цикл с дополнительным условием