Проверочные (контролирующие) тесты

Проверочные (контролирующие) тесты

Все возникающие в ЭВМ ошибки проявляются в виде отказов (систематических ошибок) и случайных ошибок (сбоев).

При отказе происходит полная или частичная утрата системой (или ее отдельным элементом) работоспособности из-за выхода за допустимые пределы значений одного или нескольких параметров этой системы. При сбое происходит кратковременное нарушение нормальной работы ЭВМ, при котором один или несколько ее элементов срабатывают неправильно, причем после сбоя эти элементы могут про�должительное время функционировать нормально.

Для выявления элементов, приведших к отказу, и эле�ментов, параметры которых близки к граничным, приме�няются аппаратурные, программные и аппаратурно-программные методы контроля. Для сигнализации о происшед�шем сбое используются обычно методы программного конт�роля.

Программно-логический контроль.

Программно-логический контроль служит для проверки правильности решения задачи при выполнении рабочей программы. Основным преимуществом этого метода контроля является возможность обнаружить ошибки выполнения программы, обусловленные сбоем. Обычно программно-логический контроль применяется для проверки решения задачи в целом или ее отдельных достаточно самостоятель�ных этапов. Наиболее известными способами программно-логического контроля являются: двойной счет, введение математических и смысловых проверок и т. д.

Контроль методом двойного счета основан на двукратном решении одной и той же задачи. Результаты решений сравниваются, и их совпадение считается призна�ком достоверности. В зависимости от типа задач применяют различные способы сравнения результатов решения.

Для статистических и экономических задач, где резуль�тат обычно получается в виде таблиц, подсчитываются кон�трольные суммы при каждом варианте просчета и контроль ведется по сравнению этих сумм. Метод двойного счета прост в исполнении, но требует больших затрат машинного вре�мени.

Введение в программу математических и логических про�верок промежуточных результатов позволяет в значитель�ной мере сэкономить машинное время по сравнению с мето�дом двойного счета, но требует значительных предваритель�ных затрат времени математиком (или программистом) на анализ алгоритма решения и формулировку дополнитель�ных математических и логических проверочных условий.

Тестовый контроль процессора

Прежде чем рассматривать систему тестового контроля процессора, кратко напомним структуру процессоров совре�менных ЭВМ и их основные функции.

Процессор представляет собой устройство для автомати�ческого выполнения последовательности операций (ариф�метических, логических, обмена информацией с другими устройствами ЭВМ), предусмотренных программой решения задачи. Процессор связан с ОЗУ и внешними за�поминающими устройствами машины и каналами устройств ввода-вывода.

Процессор состоит из арифметического (АУ) и управляющего устройств (УУ).

УУ управляет ходом вычислительного про�цесса в ЭВМ, т. е. выбирает машинные команды из ОЗУ, расшифро�вывает их, преобразуя в микрооперации (каждая микрооперация соот�ветствует одному элементарному преобразованию в ЭВМ, например, очистке сумматора, сдвигу, изменению содержимого счетчика на еди�ницу и т.д.). Кроме основных функций, связанных с организацией вычислительного процесса, УУ обеспечивает: пуск и останов ЭВМ; управление каналами и устройствами ввода-вывода; управление раз�личными режимами работы машины; связь оператора (пользователя) с различными устройствами ЭВМ и т. д.

АУ формирует из адресной части машинных команд (в адрес�ной части машинной команды указаны адреса ячеек ОЗУ, где хра�нятся операнды, над которыми нужно выполнить указанную в опера�ционной части команды операцию) исполнительные адреса и, полу�чив из ОЗУ операнды, выполняет микропрограмму (набор микро�операций, соответствующих заданной машинной команде).

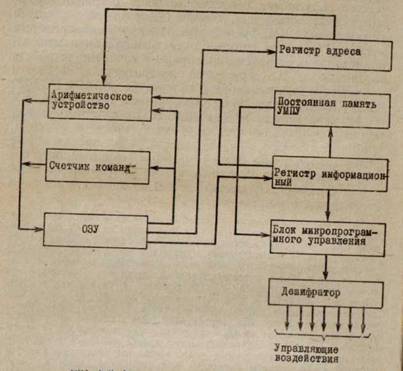

Обобщенная структурная схема процессора приведена на рисунке.

Рис. Структурная схема процессора ЭВМ.

Рассмотрим очень кратко цикл работы процессора при выполнении очередной команды:

1)счетчик команд передает в ОЗУ адрес очередной команды.

2)адресная часть команды из ОЗУ направляется в ре�гистр адреса.

3)содержимое адресной части команды из регистра адреса передается в АУ.

4)АУ формирует исполнительный адрес.

5)из АУ исполнительный адрес передается в ОЗУ.

6)операнды исполняемой команды из ОЗУ передаются в информационный регистр.

7)из информационного регистра операнды следуют в АУ.

8)АУ расшифровывает код операции, а блок микро�программного управления выдает управляющие сигналы путем последовательной выборки микроопераций, соответ�ствующих расшифрованной машинной команде, из постоян�ной памяти устройства микропрограммного управления (УМПУ).

9)полученный результат записывается в информацион�ный регистр;

10) результат вычислений из информационного регистра записывается в соответствующую ячейку ОЗУ.

Заметим, что в постоянной памяти УМПУ хранятся все микрокоманды, используемые процессором данной ЭВМ, а блок микропрограммного управления предназначен для управления арифметическим и другими функциональными устройствами в процессе выполнения микропрограмм всех машинных команд ЭВМ.

Из описания работы процессора ясно, что для создания эффективной системы контроля необходимо организовать контроль работы отдельных устройств процессора, их взаимодействия и контроль выполнения всех операций, выполняемых про�цессором.

В тестах при профилактическом конт�роле отдельных блоков процессора обычно создается тяжелый режим работы, при котором можно выявить элементы с параметрами, приближающимися к граничным.

Для проверки устройств процессора применяют тесты, использующие постоянные и переменные коды. Каждый тест в том и другом случае представляет собой набор примеров. В тестах на постоянных кодах решение всех примеров полу�чено заранее. Проверка устройства или группы блоков устройства состоит в том, что на этом устройстве решаются последовательно (в автоматическом режиме, задаваемом тестом) один пример за другим и полученные результаты сравниваются с эталонными. Если хотя бы один из результа�тов не совпадает, то подается сигнал об ошибке. Для обеспечения более надежной проверки обычно предусматривается возможность зацикливания теста, что дает возможность выявить не только постоянные, но и случайные ошибки.

Проверка на переменных кодах также использует идею набора примеров. Однако при такой проверке в тесты не заложены эталонные ответы решения примеров. Тесты на переменных кодах в зависимости от типа проверяемого устройства используют проверку полученного результата решения либо за счет восстановления первоначального набора исходных чисел, либо путем выполнения обратного действия.

При составлении примеров для программы на перемен�ных кодах важную роль играет задание исходных чисел. Коды этих чисел могут быть заданы заранее в виде таблиц либо вычисляться заново при каждом просмотре примера (при проверке решение каждого примера обычно выполняется многократ�но). В первом случае при очередном просмотре примера программа обращается к новой строке таблицы. Во втором случае при каждом новом обращении к примеру произво�дится предварительное преобразование кодов исходных чисел, например, путем их сложения, или умножения, или сдвига и т. д. Таким образом, описанный пример про�верки на переменных кодах выполняется путем многократ�ного решения одного и того же примера, но с разными исход�ными данными.

Преимуществом тестов на постоянных кодах является большая степень локализации неисправности, но они зани�мают много места в памяти ЭВМ. Тесты на переменных кодах занимают гораздо меньший объем памяти ЭВМ, но не во всех устройствах эти тесты позволяют достаточно точно локализовать неисправность. Поэтому в системе тестов обычно используют оба варианта тестов.

Тесты проверки блоков УУ обычно строятся таким обра�зом, чтобы в соответствии с принципом работы процессора проверить в отдельности устройства, участвующие в расши�фровке адресной и операционной частей команды. Проверка устройств, участвующих в обработке операционной части команды, проводится тестами, содержащими примеры с использованием всех машинных кодов данной ЭВМ и их различных комбинаций для создания тяжелых режимов работы проверяемых устройств.

Проверка блоков, участвующих в расшифровке адресной части команды, может быть проведена так: в ячейки ОЗУ записывают некоторую эталонную информацию, а затем с помощью теста в адресные регистры считывают адреса ячеек ОЗУ, где эта эталонная информация записана, и производят сравнение.

Тесты проверки АУ процессора строятся так, чтобы проконтролировать его работу с охватом максимально воз�можного числа цепей прохождения информации и при необходимости создать в проверяемых блоках тяжелые режимы. При проверке АУ основной задачей является проверка правильности выполнения всех арифметических и логических операций, осуществляемых данной машиной. Так же как и при проверке УУ, тест проверки блоков (а точ�нее, цепей выполнения различных операций) АУ состоит из набора примеров. Для простой проверки (первичной) правильности выполнения той или иной операции очень часто используют контроль по четности (хотя эта форма контроля наибольшее свое применение нашла в аппаратных методах контроля). Контроль по четности исключительно широко используется в ЭВМ на различных этапах обработки информации, начиная с поступления ее с устройств ввода. Контроль по четности можно использовать, например, в качестве первого примера при проверке операций вычита�ния, сдвига и т. д.

Операция вычитания в ЭВМ обычно реализуется как выполнение операции сложения одного числа в прямом коде, а второго в обратном или дополнительном. Если, например, нужно от числа А отнять число В, то число А представляется в прямом коде, а число В в обратном или дополнительном коде, а затем эти два числа складываются. Поэтому для того, чтобы провести операцию А-В, число В необходимо предварительно перевести в обратный или дополнительный код (напомним, что обратный код числа В получается путем инвертирования каждого разряда этого числа, а дополнительный код — добавлением к обратному единицы в младшем разряде). Контроль по четности при переводе числа в обратный код выполняется по следующему правилу: если количество разрядов в исходном числе четное, то и четность числа в обратном коде та же, что и у исходного числа; если же количество разрядов нечетное, то четность числа в обратном коде противоположна четности исходного числа. При задании контрольного примера чет�ность числа, которое необходимо вычесть, вычисляется заранее и после перевода числа в обратный (или дополни�тельный) код выполняется сравнение по четности. Однако в подавляющем большинстве примеров при выполнении контрольного примера используют для сравнения эталон�ный результат решения (при работе с тестами на постоян�ных кодах).

Контрольные примеры проверки выполнения арифметических и логических операций в тестах ЭВМ почти всегда содержат две операции: 1) операция условного перехода по признаку; 2) при�знак переполнения или аварийный останов. Часто эти две операции ис�пользуются совместно.

Проверка ОЗУ

Оперативное запоминающее устройство ЭВМ предназ�начено для приема и хранения информации, поступающей из других устройств ЭВМ или извне через устройства ввода, и выдачи этой информации по соответствующим запросам в другие устройства ЭВМ.

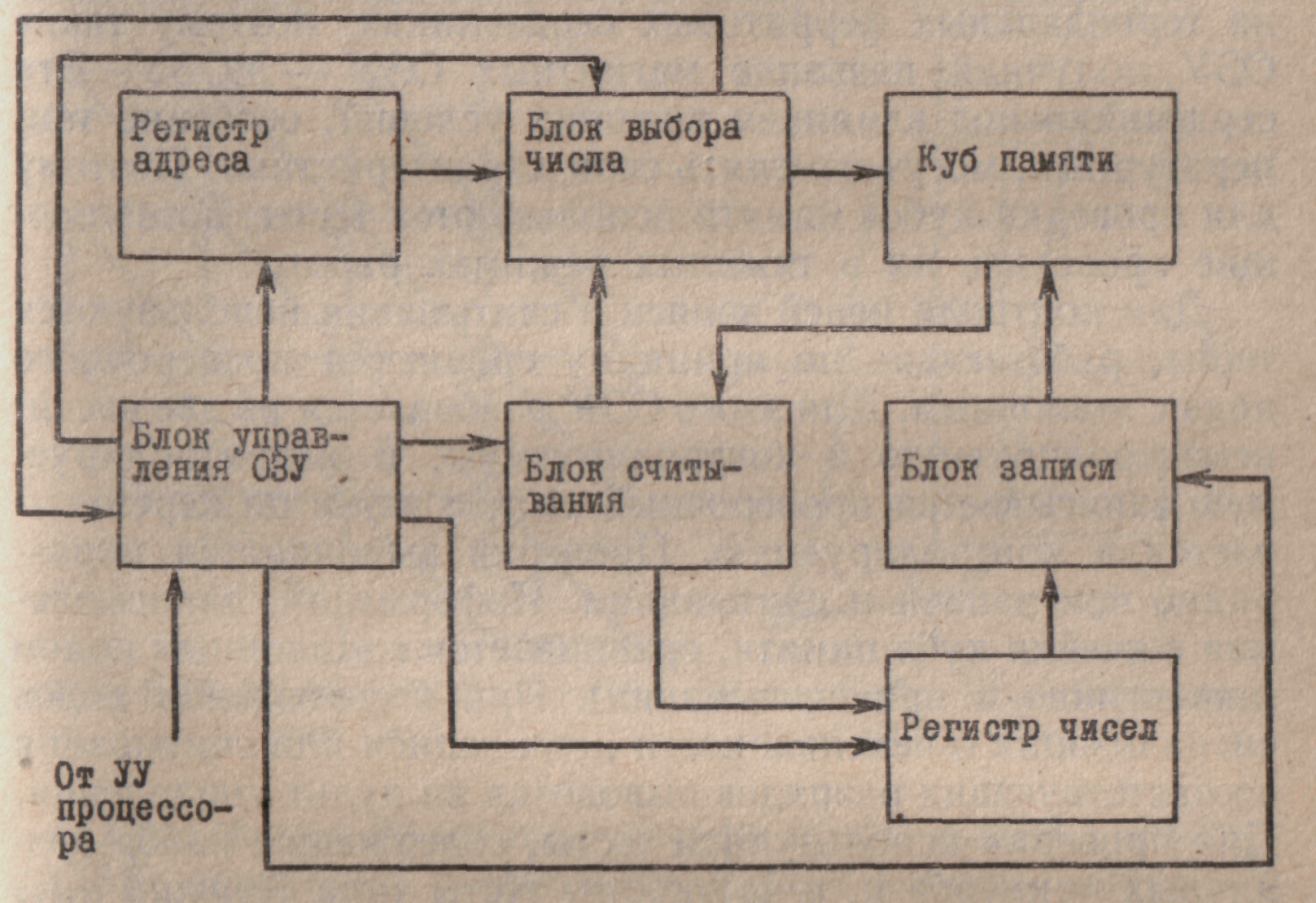

Рис. Структурная схема ОЗУ.

Структурная схема ОЗУ в общем виде представлена на рисунке. Работает ОЗУ в соответ�ствии со схемой следующим образом:

по сигналу, поступающему от устройства управления процессором в блок управления ОЗУ, вырабатывается сиг�нал, определяющий режим работы (т.е. считывание, запись, считывание-запись и т. д.), и в регистр адреса записывается код адреса числа, которое нужно считать (режим считы�вания), или код адреса числа и само число, записываемое в регистр чисел (режим записи);

блок управления ОЗУ вырабатывает управляющие сигналы для выполнения заданного режима работы. При считывании производится расшифровка адреса и с помощью блока считывания необходимое число из куба памяти пересылается на кодовые шины числа. При записи блок записи записывает код соответствующего числа в блока памяти. В режиме считывание-запись в блоке памяти, после считывания восстанавливается только что считанное число.

Тесты контроля ОЗУ должны включать в себя тесты контроля цепей записи и считывания чисел и адресов и тесты контроля блока памяти.

Для контроля цепей записи и считывания используются тесты, работающие по принципу сравнения проверочного кода с эталонным. Для этого ОЗУ разбивается на две части: неконтролируемую и контролируемую. В неконтролируе�мую записывается проверочный тест, а затем он переписы�вается в контролируемую. Проверка выполняется пораз�рядно при записи и считывании. Информация, записывае�мая в ячейки куба памяти, сравнивается с эталонным кодом (аналогично и при считывании). При несовпадении кодов сигнализация о неисправности цепи записи или считывания соответствующих разрядов выводится на пульт управления. Для проверки используются тесты, содержащие набор раз�личных примеров и, в частности, тесты типа бегущий нуль и бегущая единица.

Бегущий нуль — это группа кодов, в каждом из которых записаны единицы во все разряды, кроме одного, в котором записан нуль. Бегущим нулем этот тест называется потому, что в каждом коде местополо�жение нуля сдвинуто на один разряд:

01111 ... 11

10111 ... 11

11011 ... 11

11101 ... 11

11111 ... 01

11111 ... 10

Бегущая единица – эта группа кодов, в каждом коде все разряды заняты нулями, а один — единицей, которая от кода к коду перемещается на один разряд:

10000 ... 00

01000 ... 00

00100 ... 00

00000 ... 01

Кроме рассмотренных вариантов используется теста шахматный код – т.е. 0 и 1 чередуются.

Для выполнения тестов памяти используются различные режимы работы.

Режим адресный код служит для проверки цепей записи и считывания адресной части команд. Работает этот режим следующим образом: вначале выделяется проверяемая область основной памяти, т. е. определяется ее начальный и конечный абсолютные адреса. Затем в младшие разряды ячеек этой области записываются их абсолютные адреса. И режиме считывания производится сравнение содержимого ячеек со значением абсолютных адресов этих ячеек. Если результаты не совпали, то печатается стандартное сообще�ние об ошибке, если совпали, то выделяется новая область в основной памяти и проверка продолжается.

Также для проверки ОЗУ применяется режимы тяжелый код и обратный (инверсный). При тяжелом коде в зависимости от значения (0 или 1) разрядов тестового слова, которое хранится в эталонной части памяти, в проверяемую часть записывается последовательность нулей или единиц. При обратном коле в проверяемую часть записываются наоборот единицы или нули.

Тест проверки взу на магнитных дисках.

Для проверки НЖМД и НГМД используются тестовые режимы, когда тестовая последовательность данных записывается в сектора (кластеры) следующие по порядку друг за другом или в произвольном порядке (режим баттерфляй).

5

Проверочные (контролирующие) тесты