Двохнаправлений 8-ми розрядний шинний формувач К1810ВА86

ЗМІСТ

1. Загальні відомості про серію К1810 5

2. Мінімальний режим ВМ86 7

3. Генератор тактових імпульсів 8

4. Восьмирозрядний буферний регістр ИР82 10

5. Мікропроцесор К1810ВМ86 12

6. Двохнаправлений 8-ми розрядний шинний формувач

К1810ВА86 17

7. Принципова схема мікропроцесорної системи 19

8. Висновок 20

9. Список літератури 21

-

Загальні відомості про серію К1810

Склад МПК серії К1810 приведений в табл. 1.1, а основні електричні параметри БІС, які входять до неї – в табл. 1.2. Навантажувальна здатність кожного виходу БІС відносно невелика і відповідає одному входу мікросхеми, що виконана по стандартній ТТЛ-технології.

Таблиця1.1

|

Тип БІС

|

Призначення

|

Технологія

|

|

К1810ВМ86

|

Центральний процесор

|

n-МДП

|

|

К1810ВМ88

|

ЦП з 8-ми бітовою зовнішньою ШД

|

n-МДП

|

|

К1810ВМ89

|

Арифметичний сопроцесор

|

n-МДП

|

|

К1810ВМ87

|

Спеціалізований процесор вводу/виводу

|

n-МДП

|

|

К1810ГФ84

|

Генератор тактових сигналів

|

ТТЛШ

|

|

К1810ВГ88

|

Системний контролер шини

|

ТТЛШ

|

|

К1810ВБ89

|

Арбітр системної шини

|

ТТЛШ

|

|

К1810ВТ02

|

Контролер динамічної пам’яті (16К)

|

n-МДП

|

|

К1810ВТ03

|

Контролер динамічної пам’яті (64К)

|

n-МДП

|

|

К1810ВИ54

|

Інтервальний таймер

|

n-МДП

|

|

К1810ВТ37

|

Контролер прямого доступу до пам’яті

|

n-МДП

|

|

К1810ВИ59

|

Програмований контролер переривань

|

n-МДП

|

|

К1810ИР82/83

|

Регістр

|

ТТЛШ

|

|

К1810ВА86/87

|

Шинний формувач

|

ТТЛШ

|

Саме цьому практично завжди вихідні сигнали БІС необхідно буферизувати за допомогою зовнішніх схем, забезпечуючи необхідну навантажувальну здатність.

Таблиця1.2

|

Параметр

|

Значення(min/max)

|

|

Напруга живлення, В

|

4,75 / 5,25

|

|

Вхідна напруга низького рівня, В

|

-/ 0,8

|

|

Вхідна напруга високого рівня, В

|

-/ 2,0

|

|

Вихідна напруга низького рівня, В

|

-/ 0,45

|

|

Вихідна напруга високого рівня, В

|

2,4 / -

|

|

Вихідний струм високого рівня, мА

|

-/ -0,4

|

|

Вихідний струм низького рівня, мА

|

-/ 2,0

|

|

Струм витоку на входах чи на входах/виходах, мкА

|

-/ +- 10

|

|

Ємність входу чи входу/виходу, пФ

|

-/ 10

|

|

Ємність навантаження, пФ

|

-/ 100

|

Гранично допустимі умови експлуатації МПК БІС: температура навколишнього середовища 0…70°С; напруга на будь-якому виході відносно корпуса – 1,0…+7 В.

Центральний процесор, що входить до складу, К1810ВМ86 здійснює загальну обробку даних і управління блоками системи у відповідності із заданою програмою. Характерною особливістю МП К1810ВМ86 є можливість часткової ре конфігурації апаратної частини для забезпечення роботи в двох режимах: мінімальному та максимальному.

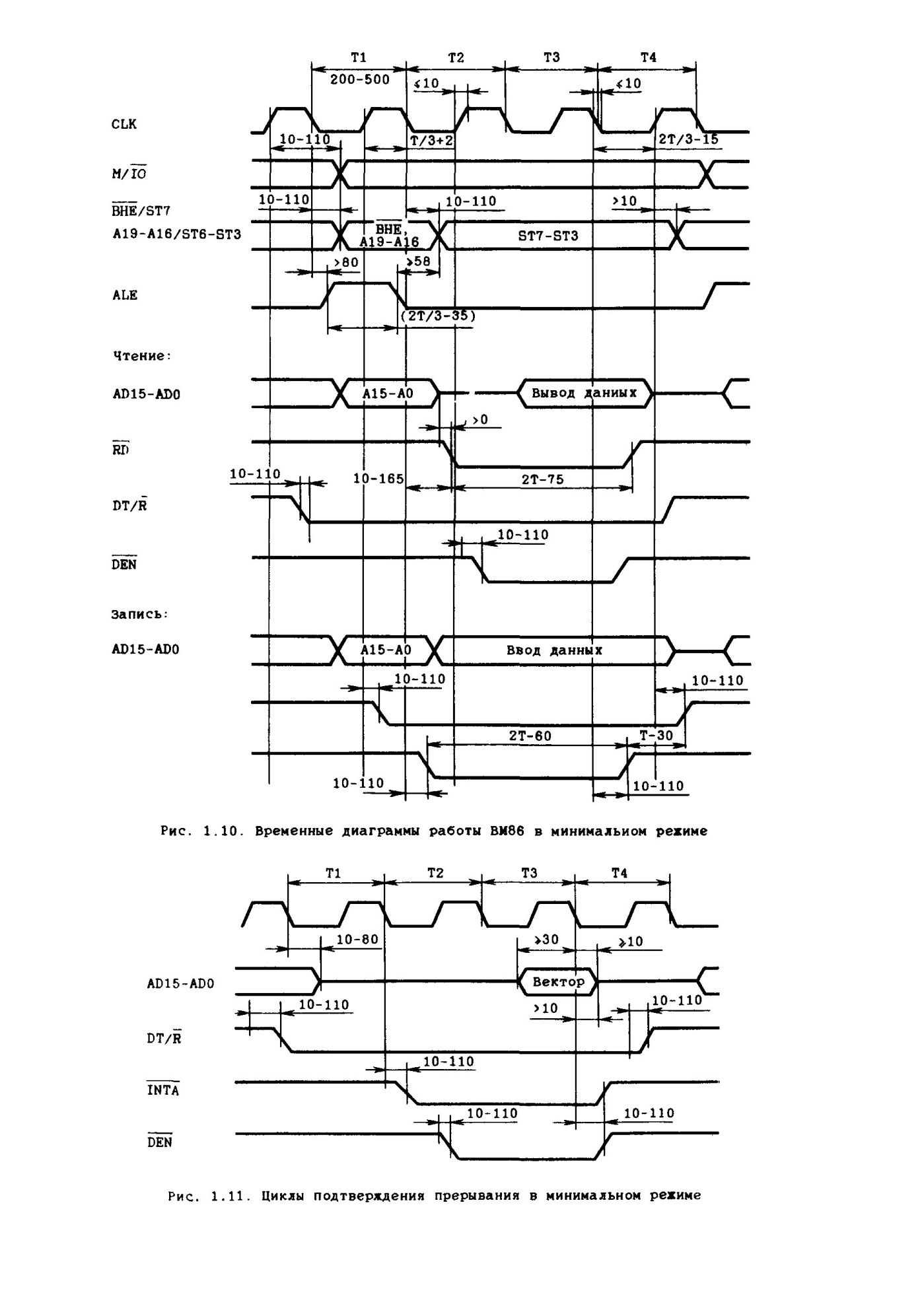

В мінімальному режимі МП формує усі сигнали для управління внутрішньо системним інтерфейсом МПС і використовується для побудови одно процесорних контролерів і мікроЕОМ. При цьому для побудови блоку центрального процесору використовується мала кількість ІС: генератор К1810ГФ84, буферні регістри К1810ИР82/83 і шинні формувачі К1810ВА86/87.

В максимальному режимі МП використовується для побудови багатопроцесорних систем (МПС), в котрих сигнали управління шиною створюється системним контролером ВГ88 на основі коду, сформованого МП.

Широка та постійно збільшуючись номенклатура БІС, що використовуються в МПС на основі МП серії К1810, забезпечують різноманітність функцій, простоту технічних рішень, компактність апаратної частини і високу ефективність використання цих систем.

2. Мінімальний режим ВМ86

Рис2.1. Архітектура МК з МП1810

У такій конфігурації процесор складається з МП КР1810ВМ86, системного генератора КР1810ГФ84 і ВІС магістрального інтерфейсу КР580ИР82/83 КР580ВА86/87 або КР1810ИР82/83 і КР1810ВА86/87, призначених для забезпечення необхідної здатності навантаження.

У схемі (Рис1.1) інтерфейс адресної шини реалізований на буферних регістрах КР580ИР82, в які записується Інформція з виходів AD0-AD15, A16-A19 МП1810ВМ86 по сигналу STB у такті TI і зберігається там протягом всього машинного циклу. Інтерфейс шини даних реалізований на шинних формувача КР580ВА86.

Інформація про дані надходить в формувачі по сигналу ()з виходів AD0-AD15 МП КР 1810ВМ86 у такті Т2-Т3. Мультиплексор К555КП11 формує роздільні ігнали читання / запису ЗУ і ВУ. Є можливість організації каналу прямого доступу до пам'яті (ПДП) на БІС КР1810ВТ37 і системи переривань на БІС КР1810ВН59.

3. Генератор тактових імпульсів

Генератор тактових імпульсів забезпечує синхронізацію роботи МПС. У складі МПК К1810 є мікросхема К1810ГФ84 (далі ГФ84), яка призначена для формування серій синхроімпульсів, сигналів скидання та готовності системи на основі мікропроцесора ВМ86.

Генератор ГФ84 характеризується: схемотехнологією — ТТЛШ; частотою синхронізації — до 80 МГц; напругою живлення — плюс 5 В і споживаною потужністю — 0,7 Вт; амплітудою імпульсів — 4,5 В (рис. 3.1).

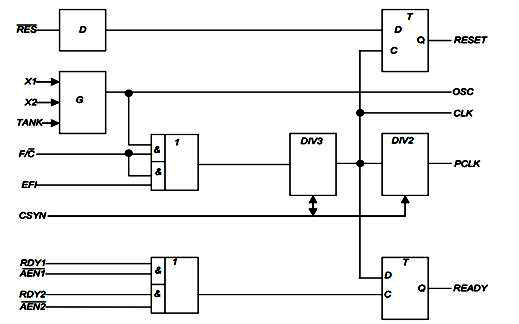

Рис.3.1. Структура ГТІ К1810ГФ84

Мікросхема ГФ84 містить схеми задаючого генератора G, дільники частоти на три DIV3 і два DIV2, які разом з логічними елементами виробляють прямокутні імпульси CLK, РСLК і синусоїдальний сигнал OSK. Вони призначені відповідно для тактування роботи мікропроцесора ВМ86,

портів периферії чи зовнішніх пристроїв системи.

Сигнали синхронізації можуть формуватися з коливань основної частоти кварцового резонатора, підключеного до входів Х1 і X2 (рис. 3.2).

За допомогою LС-фільтра, з'єднаного із входом ТАNК, можна змінити

частоту коливань резонатора.

Рис.3.2. Генератор тактових імпульсів ГФ84:

а-умовне графічне позначення; б-схема підключення кварцового резонатора

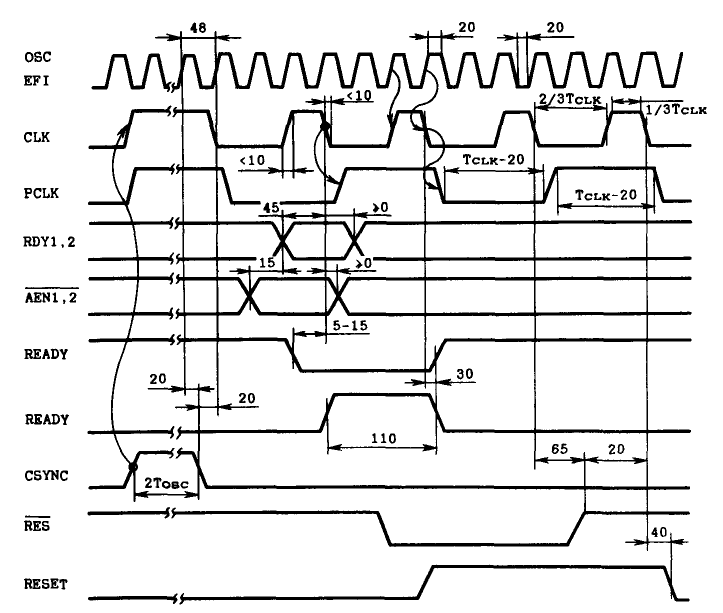

Х1 і Х2 - виводи для підключення кварцового резонатора;

TANK - Вхід для підключення RC - ланцюга, що забезпечує автоматичне формування сигналу скидання при включенні джерела живлення;

F/ - Вхід використовується для вибору задає генератора.

При = 0 відповідає внутрішньому генератору (кварцовий резонатор), а при = 1 - зовнішньому генератору імпульсів, що підключається на вхід ЕFI;

EFI - Для зовнішнього джерела частоти;

CSYN - Вхід синхронізації для тактової частоти декількох БІС;

- Сигнал початкового встановлення;

RDY1, RDY2 - вхід сигналу готовності від пристроїв, що підключаються до каналу системи;

, - Сигнали доступу до адреси по відношенню до сигналів готовності RDY1, RDY2;

RESET - Сигнал скидання;

OCS - Тактовий сигнал задаючого генератора;

СLK - вихід тактових імпульсів, їх частота дорівнює 5МГц і утворюється розподілом частоти задає на 3 (його частота 15МГц);

PCLK - Тактовий сигнал для периферійних БІС;

READY - вихід сигналу готовності, синхронізований із заднім фронтом сигналу CLK. Він дозволяє забезпечити поєднання в часі роботи МП з роботою зовнішніх пристроїв, що мають меншу швидкодію.

Рис.3.3.Часова діаграма роботи ГТІ К1810ГФ84

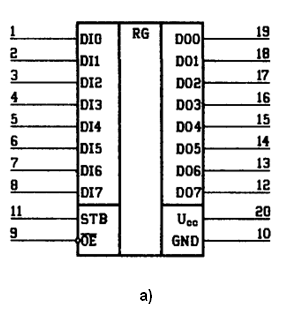

4. Восьмирозрядний буферний регістр ИР82

Восьмирозрядний буферний регістр ИР82 з трьома станами характеризуют такі параметри: схемотехнологія — ТТЛШ; число транзисторів на кристалі — 524; напруга живлення — плюс 5 В і споживана потужність 1 Вт.

Регістр ИР82 має вісім тригерів, стробоване записування даних у які відбувається по входах DI7-DI0 при значенні сигналу SТВ = 1 (рис. 4.1).

Прямі виходи D07-D00 регістра підключені до буферних схем SW з трьома станами.

При значенні сигналу OE = 0 буфери відкриваються і дані передаються на

вихід. Якщо OE =1, то буфери установлюються в Z-стан. Сигнал OE не 5 впливає на стан тригерів та функцію записування інформації.

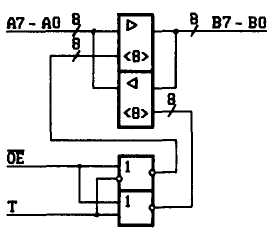

Шинний формувач ВА86 забезпечує двонаправлений обмін даними між локальною та системною шинами, підсилення сигналів та відключення від шини у визначені моменти часу. Мікросхема ВА86 характеризується такими параметрами: ТТЛШ схемотехнологією, числом транзисторів на кристалі — 567; напругою живлення — плюс 5 В і споживаною потужністю — 1 Вт.

Шинний формувач (ШФ) має двонаправлені входи — виходи А7-А0 та B7-B0, вхід Т для керування напрямком обміну і вхід OE для зняття Z-стану визначеного напрямку переходу.

Кожний розряд формувача містить дві схеми SW з трьома станами кожна.

При OE =1 всі SW-схеми знаходяться в Z-стані, при OE=1 і Т=0 обмін даними відбувається в напрямку від А до В. При OE=0 і Т=1 обмін даними відбувається від В до А.

Формувач споживає від ЦП струм біля одного міліампера, а може віддавати в системну шину десятки міліампер.

Рис 4.1. Буферний регістр ИР82:

а-умовне позначення; б-функціональна схема

DI0 – DI7 - Лінії вхідних даних;

DO0 – DO7 - Лінії вихідних даних;

STB - Стробуючий сигнал;

- Дозвіл видачі даних;

Ucc - Напруга живлення;

GND - Заземлення.

Так як за варіантом розрядність адреси даних = 20 біт, то необхідно використовувати 20/8 3 мікросхеми регістрів К1810ИР82.

Рис.4.2. Часова діаграма роботи К1810ИР82

5. Мікропроцесор К1810ВМ86.

К1810ВМ86 — радянський однокристальний 16 - розрядний мікропроцесор, що виконує близько 2 млн операцій в секунду. Синхронізується тактовою частотою від 2 до 5 МГц. Є клоном мікропроцесора Intel 8086 з тактовою частотою до 10 МГц.

Входить до складу мікропроцесорного комплекту серії КР1810, призначеного для побудови мікро- ЕОМ.

Мікропроцесор К1810ВМ86 (далі позначений для стислості ВМ86 ) містить 14 16 - бітових внутрішніх регістрів і утворює 16 - бітову шину даних для зв'язку з зовнішньою пам'яттю і портами введення-виведення. Шина адреси має 20 ліній, що дозволяє безпосередньо адресуватися до пам'яті ємністю до 1 Мбайт = 220 = 1048576 байт. Простір пам'яті розділяється на сегменти по 64 Кбайт, причому в будь-який момент часу МП може звертатися до комірок чотирьох сегментів, які програмно обрані як поточних. Сегментація пам'яті забезпечує зручний механізм обчислення фізичних адрес і сприяє модульним проектування програмного забезпечення, що спрощує програмування і налагодження.

Для скорочення необхідного числа висновків БІС молодші 16 адресних ліній мультиплексовані в часі з лініями даних і складають єдину шину адреси / даних ( ШАД ). Чотири старші адресні лінії аналогічно мультиплексовані з лініями стану. Щоб сигнали цих ліній можна було використовувати в системі, їх обов'язково поділяють за допомогою зовнішніх схем, тобто здійснюють демультиплексирование шин.

Має 20 -ти розрядну шину адреси, що дозволяє забезпечити пряму адресацію 1 Мбайт зовнішньої пам'яті. Область адресного простору пам'яті розбита на сегменти по 64 КБ. Така організація пам'яті забезпечує зручний механізм обчислення фізичних адрес. Шина адреси та шина даних мультиплексовані. При організації обчислювальних систем їх потрібно розділити (регістри -засувки ). Мікропроцесор може звертатися як до пам'яті, так і до зовнішніх пристроїв.

При виконанні операцій введення - виведення використовуються 8 - або 16 - бітові адреси, так що крім доступу до основної пам'яті МП може звертатися до портів ( регістрів введення - виведення ), сумарна ємність пам'яті яких становить 64 Кбайт. У БІС ВМ86 реалізована багаторівнева система переривань по вектору з числом векторів до 256. Адреси підпрограм переривання займають область ємністю 1 Кбайт, яка розташовується в пам'яті, починаючи з молодших адрес. Передбачена також організація прямого доступу до пам'яті, при якому МП припиняє роботу і переводить в третій стан шини адреси, даних і управління.

При зверненні до зовнішніх пристроїв використовуються 16 молодших ліній шини адреси. Отже, можна підключити 64 до 8-бітних зовнішніх пристроїв або 32 до 16-ти розрядних. Мікропроцесор має багаторівневу систему переривань: 256 векторів переривань.

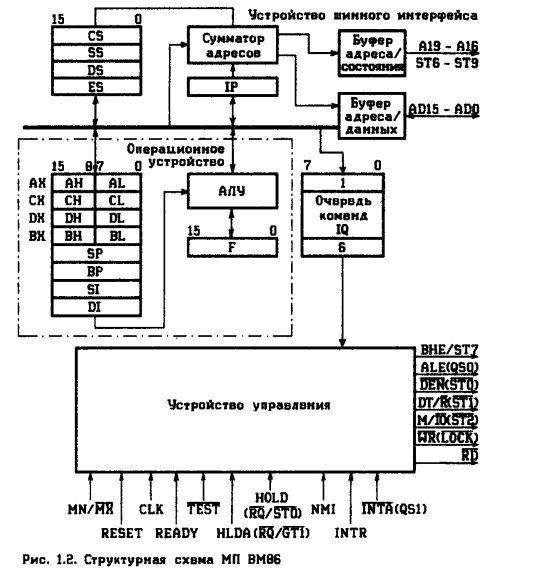

Рис 5.1. Структурна схема МП ВМ86.

Збільшена структурна схема МП ВМ86 (рис. 5.1 ) містить дві відносно незалежні частини: операційне пристрій, що реалізує задані командою операції, і пристрій шинного інтерфейсу, що здійснює вибірку команд з пам'яті, а також звернення до пам'яті і зовнішніх пристроїв для зчитування операндів і запису результатів. Обидва пристрої можуть працювати паралельно, що забезпечує суміщення у часі процесів вибірки і виконання команд. Це підвищує швидкодію МП, так як операційне пристрій, як правило, виконує команди, коди яких вже знаходяться в МП, і тому такти вибірки команди не включаються до її цикл.

Операційний пристрій МП містить групу загальних регістрів, арифметично-логічний пристрій ( АЛП), регістр прапорів F і блок управління.

Вісім 16 - бітових регістрів загального призначення беруть участь у багатьох командах. У цих випадках регістри загального призначення кодуються трехбітовим кодом, який розміщується в поле ( або полях) формату команди.

У відповідності з основним призначенням розглянутих регістрів виділяють регістри АХ, ВХ, СХ, DX, використовувані насамперед для зберігання даних, і регістри SP, BP, SI, DI, які зберігають головним чином адресну інформацію. Особливістю регістрів АХ, ВХ, СХ, DX є те, що вони допускають роздільне використання їхніх молодших байтів AL, BL, CL, DL і старших байтів АН, ВН, СН, DH. Тим самим забезпечується можливість обробки як слів, так і байтів і створюються необхідні умови для програмної сумісності ВМ86 і ВМ80. Відповідність регістрів цих двох мікропроцесорів зазначено в табл. 1.12, де FL - молодший байт регістра F.

Всі інші регістри є неподільними і оперують 16-бітовими словами, навіть у разі використання тільки старшого чи молодшого байтів. Вказівні регістри БР і ВР зберігають зміщення адреси в межах поточного стекового сегмента пам'яті, а індексні регістри і 01 зберігають зміщення адреси відповідно в поточному сегменті даних і в поточному додатковому сегменті. Однак при використанні цих регістрів для адресації операндів можлива зміна сегментів пам'яті.

Арифметичне-логічний пристрій (АЛП) містить 16-бітовий комбінаційний суматор, за допомогою якого виконуються арифметичні операції, набори комбінаційних схем для виконання логічних операцій, схеми для операцій зрушень і десяткового корекції, а також регістри для тимчасового зберігання операндів і результатів.

Буфер шини адреси / даних ( БАД ) містить 16 двонапрямлених керованих підсилювачів з трьома вихідними станами і забезпечує номінальну навантажувальну спроможність ліній AD15 - ADO.

Буфер шини адресу/стану (БАС) містить чотири односпрямованих підсилювача з трьома вихідними станами і забезпечує номінальну навантажувальну спроможність ліній A19/S6 - A16/S3.

Сегментні регістри зберігають базові (початкові ) адреси сегментів пам'яті: кодового сегмента CS, в якому міститься програма; стекового сегмента SS; сегмента даних DS; додаткового сегмента ES, в якому зазвичай містяться дані. Наявність сегментних регістрів обумовлено поділом пам'яті на сегменти і використовуваним способом формування адрес пам'яті.

Суматор адрес здійснює обчислення 20-бітових фізичних адрес.

Покажчик команд 1Р зберігає зсув наступної команди в поточному кодовому сегменті, тобто вказує на наступну по порядку команду. Він є аналогом стандартного програмного лічильника з тією лише різницею, що його вміст визначає адресу команди лише в сукупності з вмістом регістра СБ; якщо ж СБ заповнений нулями, аналогія стає повною.

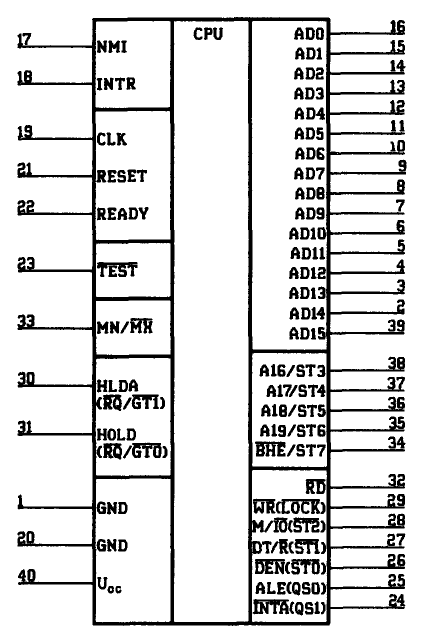

Рис 5.2. Мікропроцесор К1810ВМ86. Умовне позначення.

AD15 - AD0 - мультиплексна двунаправлена шина адреси/даних, по якій з поділом у часі передаються адресна інформація та дані;

A16/S3, A17/S4, A18/S5, A19/S6 - лінії адреси/стану. В перебігу такту Т1 тримає старші біти адреси при зверненні до пам’яті чи ВУ, в перебігу Т2, Т3, ТW, T4 – інформація про стан МП;

/S7- дозвіл старшого байта, активний сигнал означає, що по старшій половині AD15 - AD8 передаються 8 - бітові дані. Він замикається в зовнішньому регістрі адреси і використовується як додатковий адресний вихід, визначальний доступ до старшого банку пам'яті. Спільне використання та молодшої лінії адреси А0 для дешифрування адрес дозволяє здійснювати передачу слів або окремих байтів по шині АD;

- читання, строб, показує що МП виконує цикл читання;

RDY – готовність;

INTR - запрос переривання;

NMI - немаскуюче переривання;

- вхідний сигнал, перевіряємий командою WAIT, котра переводить МП в стан очікування при = 1;

CLK - тактова синхронізація ( тактирование ). Сигнал синхронізації від зовнішнього генератора тактових імпульсів, призначений для синхронізації МП. Використовується серія тактових імпульсів CLK з періодом повторення T, рівним 200 - 500 нс.;

RESET - скидання, переводить МП в певний початковий стан, в якому скинуті сегментні регістри ( крім CS, всі розряди якого встановлюються в одиничний стан ), покажчик команд IP, всі прапори, регістри черги команд і всі внутрішні тригери в пристрої керування. Сигнал RESET не впливає на стан загальних регістрів, які встановлюються в початковий стан програмним шляхом. На час дії сигналу RESET всі виходи, що мають три стани, стають пасивними. Мінімальна тривалість сигналу RESET при першому включенні МП становить 50 мкс., А при повторному запуску - чотири такту синхронізації. Після зняття сигналу RESET робота МП поновлюється з початкового стану;

MN/- мінімальний / максимальний режим. Сигнал на цей вході визначає режими роботи МП: 1 - мінімальний, 0 - максимальний. Використовуваний режим в роботі мінімальний, тому на нього потрібно подавати напругу;

ST2-ST0 - лінії стану, характеризують тип виконуючого циклу;

/, /,/, /- запит/Надання, використовується для обміну між процесорами в багатопроцесорній системі, для управління процедурою використання шин;

- блокування шини;

QS1, QS0 - стан черги, вказує стан внутрішньої 6-ти байтової черги команд МП.

Так як за варіантом розрядність адреси даних = 20 біт, то необхідно використовувати 20/16 2 мікропроцесора К1810ВМ86.

Рис 5.3. Часові діаграми роботи ВМ86 у мінімальному режимі.

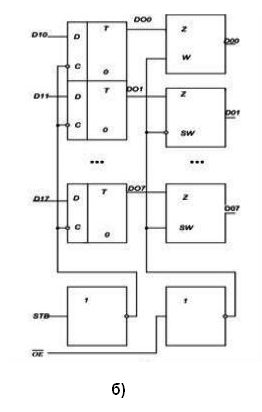

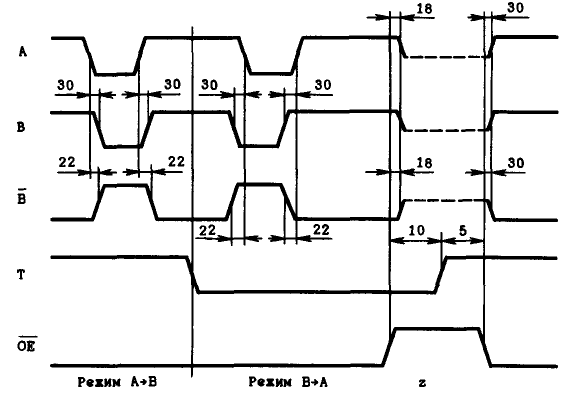

6. Двохнаправлений 8-ми розрядний шинний формувач К1810ВА86.

Шинний формувач представляє 8-розрядний паралельний приймач з трістабільний виходами і використовується як буферну пристрій шини даних в мікропроцесорних системах. Графічне зображення наведено на рис.6.2. Восьмирозрядних шинні формувачі застосовують як буферні пристрої шини даних. Велика вихідна ємність і простота управління дозволяють використовувати їх для побудови двонаправлених узгоджувальних буферів міжмодульних зв'язку. Формувач складається з восьми однакових функціональних блоків із загальними сигналами керування. Функціональні блоки складаються з двох підсилювачів формувачів з трьома станами на виходах, схема включення яких забезпечує різноспрямовану передачу.

Рис. 6.1. Функціональна схема ШФ ВА86

Опишемо виводи мікросхеми.

Рис 6.2. Умовне позначення К1810ВА86.

DI7-DI0 - вхід/вихід ліній даних. Залежно від стану входу Т вони можуть бути вхідними, якщо на Т сигнал високого рівня, і вихідними, якщо на Т сигнал низького рівня;

DО7-DО0 - вхід / вихід ліній даних. Вони є вхідними, якщо на Т сигнал низького рівня, і вихідними, якщо на Т сигнал високого рівня;

Т - вхід керування напрямком передачі. При Т = 0 здійснюється передача від DO до DI, при Т=1 - від DI до DO;

- вхід дозволу передачі. При =0 знімається Z - стан з виходу формувача, обраного по входу Т.

Так як шина даних в МП К1810ВМ86 складає 20 біт, то необхідно використовувати 20/8 3 мікросхеми К1810ВА86

Рис. 6.3. Часова діаграма роботи ШФ ВА86

7. Принципова схема мікропроцесорної системи

Принципова схема мікропроцесорної системи проілюстрована на кресленні 1. Специфікація елементів наведена в дод. А.

На комплекті К1810 була спроектована принципова схема МПС. Вона складається з ГТІ К1810ГФ84, шинного формувача К1810ВА86, буферних регістрів К1810ИР82, мікропроцесора К1810ВМ86. У схемі інтерфейс адресної шини реалізований на буферних регістрах К1810ИР82, в які записується інформція з виходів AD0-AD15, A16-A19 МП1810ВМ86 по сигналу STB у такті TI і зберігається там протягом всього машинного циклу. Інтерфейс шини даних реалізований на шинних формувача К1810ВА86.

Інформація про дані надходить в формувачі по сигналу ()з виходів AD0-AD15 МП КР 1810ВМ86 у такті Т2-Т3. Мультиплексор К555КП11 формує роздільні ігнали читання / запису ЗУ і ВУ.

8. Висновок

Результатом виконання курсового проекту є спроектована мікропроцесорна система на комплекті К1810.

Згідно з технічним завданням був зроблений опис всіх мікросхем, які використовуються в МПС: ГТІ К1810ГФ84, шинний формувач К1810ВА86, буферні регістрі К1810ИР82, мікропроцесор К1810ВМ86. Розроблена спрощена схема мікропроцесорної системи у мінімальному режимі. На базі підібраних мікросхем була розроблена структурна та принципіальна схема, яка відображає розташування та взаємозв’язок блоків між собою.

В рамках курсового проекту була вирішена основна задача – розвиток та закріплення навичок самостійної роботи при вирішені конкретної задачі розробки мікропроцесорної системи.

8.Список літератури

- Ю. М. Казаринова., Микропроцессорный комплект К1810: Структура, программирование, применение/ Под ред. И.П. Степаненко. – М.: Высшая школа, 1990.

- Горбачев Г.Н., Гаплыгин Е.Е. Промышленная электроника: Учебник для вузов/ Под ред. Лабунуева. – М.: Электроатомиздат, 1988.-320с. ил

- Ефимов И.Е., Козырь И.Я, Горбунов Ю.И. Микроэлектроника: проектирование, виды микросхем, функциональная микроэлектроника: Учебное пособие для приборостроения спец.вузов. – М.: Высшая школа, 1987. – 416c.

- В.Г. Домрачев., Ю. Н. Чернышов. Микропроцессорные БИС и их применение: Одноплатные микроЭВМ/ Под ред. В.Г Домрачева. – М.: Энергоатомиздат, 1988.

- Горбунов В.Л., Панфилов Д.И., Преснухин Д.Л. Микропроцессоры. Основы построения микро ЭВМ. – М.: Высшая школа,1986

Двохнаправлений 8-ми розрядний шинний формувач К1810ВА86