Транзисторные Электронные ключи

Лекция 1.4

Транзисторные Электронные ключи

Электронный ключ (ключ) – электронная схема, основное назначение которой состоит в замыкании и размыкании цепи нагрузки под действием управляющих входных сигналов.

Качество ключа характеризуется:

1) падением напряжения на нем в замкнутом (включенном) состоянии;

2) током в разомкнутом (выключенном) состоянии;

3) временем переключения из одного состояния в другое;

4) мощностью, затрачиваемой в цепи управления ключом.

Простейшие ключи применяются в цифровых устройствах в качестве логических инверторов, реализующих логическую функцию НЕ.

На основе ключей создаются логические элементы, триггеры, мультивибраторы, другие импульсные и цифровые устройства.

На рис. 1, а нагрузка, подключенная к транзисторному ключу, оказывается зашунтированной большим или малым сопротивлением транзистора. В таком электронном ключе на биполярном транзисторе, когда на базе транзистора «0» относительно эмиттера, транзистор «закрыт», ток через него не идёт, на коллекторе всё напряжение питания (сигнал высокого уровня – «1»). Когда на базе транзистора «1», он «открыт», возникает ток коллектор-эмиттер и падение напряжения на сопротивлении коллектора, напряжение на коллекторе, а с ним и напряжение на выходе, уменьшается до низкого уровня «0».

Схема представляет собой логический инвертор, реализующий логическую функцию «НЕ» (логический элемент «НЕ»).

Если транзистор и резистор поменять местами (рис. 1, б), то получится «логический повторитель» (схема задержки).

Ключи на биполярных транзисторах

Статические характеристики ключа с ОЭ

Схема простейшего транзисторного ключа с ОЭ c активной нагрузкой Rк показана на рис.4.16,а. В цепи управления включены источник управляющего напряжения eб и резистор Rб. Широкое распространение ключа ОЭ объясняется тем, что он имеет наибольший коэффициент усиления по мощности.

В статических состояниях ключа транзистор либо открыт, либо закрыт. Открытый транзистор обычно насыщен, в ряде случаев используются и ненасыщенные транзисторные ключи, в которых открытый транзистор работает на границе активного режима.

Напомним, что в активном режиме эмиттерный переход смещен в прямом направлении (uэб > 0), коллекторный – в обратном (uкб < 0). В активном режиме коллекторный ток в соответствии с формулой (5) приблизительно линейно зависит от тока базы: . Токи и напряжения на электродах транзистора можно найти графоаналитически. Для этого на семействе выходных характеристик (рис.4.16,б) строится прямая, соответствующая уравнению

, (34)

которая называется линией нагрузки. На семействе входных характеристик (рис.4.16,в) строится прямая

.

Например, при eб = еб5 ордината точки пересечения прямой с входной характеристикой дает ток базы iб5. Точка А пересечения выходной характеристики для iб = iб5 с линией нагрузки, как видно, соответствует режиму насыщения.

Остаточное напряжение на транзисторе в режиме насыщения

,

где – разность напряжений на коллекторном и эмиттерном переходах; rнас – сопротивление коллекторного слоя в режиме насыщения. Значение составляет десятки милливольт (10 - 40 мВ). Омическая составляющая остаточного напряжения Iкнrнас меняется в широких пределах. Для уменьшения этой составляющей в интегральных транзисторах всегда используются скрытые коллекторные слои и обычно Uкн = 50 – 100 мВ. Однако в ряде кремниевых транзисторов Uкн достигает 1 В, а у мощных высоковольтных транзисторов даже 3 - 5 В.

Эквивалентная схема ключа ОЭ в режиме насыщения показана на рис.4.17 (для p-n-p-транзистора). Значение Uбн оставляет 0,3 - 0,4 В

у германиевых транзисторов и 0,6 - 1,1 В – у кремниевых. Значение Uбн у кремниевых транзисторов слабо зависит от тока.

Формальным критерием насыщения является условие, чтобы напряжение на коллекторном переходе было прямым. Однако в тех случаях, когда заданы токи, такой критерий неудобен. Вместо него используется так называемый токовый критерий насыщения:

.

Силу этого неравенства характеризуют особым параметром – степенью насыщения:

, (35)

где iб – отпирающий ток базы. Значение S = 1 соответствует границе с активным режимом.

Закрытое состояние транзистора соответствует режиму отсечки. В этом состоянии, строго говоря, должно выполняться условие eб < 0. Однако практически эмиттерный переход кремниевого транзистора остается закрытым, если eб < Uпор 0,6 В. При этом токи всех трех электродов транзистора обычно не превышают долей микроампера. Поэтому падением напряжения на сопротивлениях Rб и Rк можно пренебречь и считать |uбэ| = |eб| и |uкэ| = |Ек|.

Переходные процессы в простейшем транзисторном ключе

Временные диаграммы для процессов при скачкообразных изменениях ЭДС входной цепи eб представлены на рис.4.21,а. Процесс при включении состоит из этапов: задержки фронта tз, формирования фронта коллекторного тока tф и накопления избыточного заряда в базе tн.

Задержка фронта обусловлена зарядом входной емкости Свх запертого транзистора. Пока , емкость Свх заряжена до напряжения uбэ = Eб2, эмиттерный переход закрыт (однако имеется емкостный ток) и согласно рис.4.21,б

,

где с = СвхRб; Свх = Сэ + Ск, минус в левой части равенства будет только при использовании транзистора типа p-n-p.

Полагая t = tз, -uбэ = Uпор, находим:

,

откуда

. (40)

Если бы емкость Свх перезаряжалась постоянным током Iб1, то и

. (41)

На этапе формирования фронта коллекторного тока tф транзистор работает в активном режиме, ток коллектора iк нарастает при постоянном токе базы iб = Iб1. Изменение заряда в базе описывается уравнением (39), где iб = Iб1. Заряд увеличивается от начального значения Qб(0) = 0, стремясь к значению Qб() = Iб1B, получаемому из (39) при . Следовательно, заряд в базе

, (42)

а ток коллектора с учетом равенства (38)

.

Поскольку, как было показано в § 4.4, , можем записать

. (43)

Фронт коллекторного тока заканчивается в момент времени t = tф, когда транзистор насыщается, ток iк достигает значения , а заряд в базе – граничного значения Qгр, которое с учетом равенства (38) определяется как

. (44)

Время tф определяется из уравнения, получающегося при подстановке в (42) t = tф, Qб(tф) = Qгр,

. (45)

То же самое выражение следует после подстановки в (43) t = tф, iк(tф) = Iкн.

Пример. Пусть В0 = 100, Iб1 = 0,1Iкн, экв = 150 нс. Тогда

.

После насыщения транзистора в конце интервала tф внешних изменений в схеме ключа не происходит. Однако продолжается накопление заряда в базе за счет инжекции неосновных носителей не только через эмиттерный, но и через коллекторный переходы. В результате этого распределение концентрации неосновных носителей в базе бездрейфового транзистора (линия 2, рис.4.20) смещается вверх при iк = Iкн = const параллельно линии 1, показывающей распределение неосновных носителей в граничном режиме. Заряд в базе насыщенного транзистора можно представить в виде суммы

Qб = Qгр + Qизб, (46)

где Qизб – избыточный заряд; Qгр определяется из (44).

На этапе накопления избыточного заряда в базе справедливо уравнение

, (47)

которое отличается от (37) заменой б на время жизни в состоянии насыщения н и приравниванием к нулю третьего слагаемого в левой части (поскольку ). Отсчитывая время t

от начала этапа накопления, найдем экспоненциальный закон изменения заряда:

,

где получается из (47) при .

Время накопления можно оценить по формуле

. (48)

Для упрощения полученных соотношений принято B = const, н = const. В действительности время жизни неосновных носителей в базе плавно меняется по мере их накопления.

Итак, в конце этапа накопления имеем , откуда

.

Поскольку согласно (35) степень насыщения

,

а , получим:

. (49)

В момент подачи в базу запирающего тока

начинается процесс выключения транзистора, состоящий из двух этапов: рассасывания длительностью tр, формирования спада коллекторного тока длительностью tc (см. рис.4.21).

На этапе рассасывания транзистор остается в режиме насыщения, но происходит уменьшение накопленного в базе заряда. Этот процесс описывается уравнением, аналогичным (47):

, (50)

и продолжается до перехода транзистора в активный режим, когда заряд достигает значения . Полагая, что в начале рассасывания , из (51) находим:

,

откуда, полагая t = tp, Qб(tp) = Qгр, получаем:

. (51)

С учетом равенств (44), (35) и выражение (51) преобразуется к виду

, (52)

где S – степень насыщения транзистора перед началом рассасывания.

Из выражения (52) отчетливо видно, что время рассасывания tр уменьшается с увеличением запирающего тока Iб2 и уменьшением степени насыщения.

На этапе спада tс транзистор снова работает в активном режиме. Решая уравнение (39) при iб = -Iб2, Qб(0) = Qгр = Iкн = = Iкнв/В, получаем:

. (53)

Заряд уменьшается по экспоненциальному закону, стремясь к значению –Iб2B. Однако заряд неосновных носителей, определяемый по модулю, не может стать отрицательным. Процесс заканчивается при Qб = 0. Согласно (38) ток коллектора уменьшается пропорционально заряду. Подставляя в формулу (53) t = tc, Qб = 0, находим:

. (54)

Отметим, что граничный заряд в выражениях (45), (54) принимается равным IкнB/В, а в выражении (52) – Iкнн/В. Коэффициент передачи тока базы В на границе активного режима меньше, чем в активном.

Из полученных соотношений для длительностей интервалов переходного процесса следует, что эти интервалы сокращаются при уменьшении времени жизни неосновных носителей в базе (B или н), а интервалы tф, tр, tс – при увеличении управляющего сигнала (Iб1 или Iб2). Кроме того, длительности интервалов tф и tр зависят от степени насыщения S: с ростом S время tф уменьшается, поскольку,

например, при S = 4 в (45) имеем: , а при

S = 5 - , время tр увеличивается.

Таким образом, рассмотрен метод расчета переходных процессов в транзисторе с ОЭ при активной нагрузке и скачкообразных изменениях входного тока. Однако метод заряда может использоваться и при более сложной нагрузке, когда ток коллектора насыщенного транзистора не остается постоянным, и при другой форме входного тока.

В действительности процесс запирания транзистора развивается сложнее, чем описано. В частности, когда в процессе спада ток коллектора iк становится меньше запирающего тока базы Iб2, ток эмиттера становится отрицательным и растет по модулю с уменьшением тока iк. При этом распределение неосновных носителей в базе становится нелинейным (т.е. нарушается основное допущение метода заряда). Когда концентрация неосновных носителей у эмиттерного перехода упадет до равновесного значения, эмиттерный переход начинает работать при отрицательном смещении (uэ < 0). Наступает этап динамической отсечки транзистора, на котором оба p-n-перехода смещены в обратном направлении, а концентрация неосновных носителей имеет максимум в средней части базы. Если Iб2 << Iкн, влиянием этапа динамической отсечки можно пренебречь.

4.6. Особенности процессов в планарных транзисторах

Планарная технология является основной при изготовлении транзисторов. При этом введение примесей в исходную пластину полупроводника осуществляется за счет диффузии (см. § 2.7), следствием чего является неравномерное их распределение в направлении диффузии.

Примерное распределение примесей в p-n-p-структуре (рис.4.22) получено в результате двукратной диффузии. Исходная пластина полупроводника p-типа содержит акцепторную примесь с концентрацией Nа.исх порядка (1014-1015) атом/см3. В результате первой диффузии донорной примеси и последующей разгонки получается распределение концентрации донорной примеси с поверхностной концентрацией Nд.пов порядка 1017 атом/см3 и почти

экспоненциально спадающее на участке будущей базы. При этой диффузии формируется коллекторный p-n-переход транзистора. Затем на меньшую глубину производится диффузия акцепторной примеси, распределение которой с учетом последующей разгонки приобретает более резко спадающий характер, чем распределение донорной примеси. Причем поверхностная концентрация акцепторов Nа.пов имеет порядок 1019-1020 атом/см3. В процессе второй диффузии формируется эмиттерный переход транзистора, который можно считать резким, а коллекторный переход получается плавным.

Поскольку в данном случае пластина содержит как акцепторную, так и донорную примеси, концентрация носителей заряда определяется эффективной концентрацией примеси Nа.эф = Nа + Nа.исх - Nд и Nд.эф = Nд - Nа.исх - Nа. Наглядное изображение распределения примесей в пластине (рис.4.22) затруднительно, поскольку концентрации при переходе из эмиттерного слоя в базовый меняются на два порядка. Толщина технологической базы wб0 получается порядка десятых долей и единиц мкм, например в высокочастотном транзисторе КТ 312 wб0 = 2 мкм, а в СВЧ-транзисторе КТ 904 wб0 = 0,7 мкм.

Планарные транзисторы отличаются от рассмотренных в основном процессами в базе и коллекторе. Поскольку эффективная концентрация примеси в базе плавно уменьшается вдоль оси x (на рис.4.23,а показана в увеличенном масштабе), появляется электрическое поле, ускоряющее движение носителей заряда, инжектированных из эмиттера, т.е. планарный транзистор относится к дрейфовым.

Действительно, из-за того, что равновесная концентрация основных носителей в базе nп0 также будет уменьшаться вдоль оси х, возникает диффузионный поток электронов вдоль оси х. Вследствие того, что концентрация электронов nп0(х) в левой части базы становится меньше Nд.эф(х), возникает нескомпенсированный положительный объемный заряд донорных атомов, а в правой части базы концентрация nп0(х) становится больше Nд.эф(х) и возникает отрицательный объемный заряд. Этим и объясняется возникновение электрического поля в базе, напряженность которого составляет от сотен до тысяч В/см. Следовательно, появляется дрейфовая составляющая потока электронов в базе, направленная навстречу диффузионной и компенсирующая ее. Распределение равновесной концентрации неосновных носителей в базе определяется на основании равенства (1-2):

,

она увеличивается вдоль оси х.

Поскольку дырки, инжектированные из эмиттера, в базе дрейфового транзистора движутся за счет не только диффузии, но и электрического поля, время пролета носителей через базу существенно уменьшается.

В активном режиме распределение концентрации неосновных носителей в базе дрейфового транзистора нелинейное (рис.4.23,б), поэтому погрешность при расчете длительности фронта коллекторного тока tф методом заряда увеличивается.

Поскольку у дрейфовых транзисторов коллекторный переход плавный и почти симметричный (рис.2.3), граничные концентрации

неосновных носителей с обеих сторон перехода почти одинаковы. В режиме насыщения необходимо учитывать инжекцию не только из коллектора в базу, но и из базы в коллектор и, соответственно, накопление избыточного заряда как в базе, так и в коллекторе. Распределение концентраций неосновных носителей в режиме насыщения дрейфового транзистора (рис.4.24) примерно такое же, как в инверсном режиме транзистора.

Если положить время жизни неосновных носителей одинаковым и равным н во всех трех слоях транзистора, то суммарный избыточный заряд, накапливающийся в установившемся режиме насыщения в этих слоях (суммирование осуществляется без учета знака заряда) оказывается пропорциональным отпирающему току базы Iб1:

.

При неодинаковых временах жизни пропорциональность суммарного заряда Q() току базы сохраняется, но выражение становится громоздким [10].

Планарные транзисторы отличаются тем, что пассивная часть базы значительно толще активной. Часть избыточного заряда Q() накапливается в пассивной части базы.

При анализе рассасывания tр и спада коллекторного тока tс планарных транзисторов метод заряда дает большую погрешность, чем при анализе фронта tф, поскольку распределение концентрации в базе в переходном процессе сильно отклоняется от линейного.

Поскольку коллекторный слой планарного транзистора значительно высокоомнее, чем эмиттер, при расчете его характеристик необходимо учитывать сопротивление этого слоя.

Ключи на полевых транзисторах

Электронные ключи на полевых транзисторах работают на тому же принципу, что и электронные ключи на биполярных транзисторах. Ключи на полевых транзисторах потребляют меньший ток управления, обеспечивают гальваническую развязку входных и выходных цепей, однако быстродействие их немного ниже по сравнению с биполярными.

Работа МДП-транзисторов в ключевом режиме

Известны три разновидности ключей на МДП-транзисторах:

1) с резисторной нагрузкой;

2) с динамической (транзисторной) нагрузкой;

3) комплементарные (КМОП или КМДП) ключи.

В ключевых схемах наиболее часто применяют МДП-транзисторы с индуцированным каналом n-типа, так как это позволяет сравнительно просто согласовывать выходные потенциалы предыдущих ключей со входными потенциалами последующих ключей. Такие ключи по своим логическим уровням и порогам совместимы с логическими элементами ТТЛ.

Ключи на МДП-транзисторах с каналами n-типа обеспечивают более высокое быстродействие, чем при использовании транзисторов с каналами p-типа.

Ключи на МДП-транзисторах с резисторной нагрузкой

При рассмотрении ключей на МДП-транзисторах будем полагать, что входное напряжение uвх подаётся с выхода аналогичного ключа. Входное напряжение высокого уровня, соответствующее логической единице, обозначается U1, напряжение низкого уровня, соответствующее логическому нулю, – U0. Нагрузкой ключа являются входные цепи других ключей.

При низком входном напряжении uвх = U0, которое меньше порогового напряжения Uпор , МДП-транзистор закрыт, состояние ключа с резисторной нагрузкой (рис. 1, а) соответствует точке А на рис. 1, б. Выходное напряжение в этом состоянии uвых = Ес = U1, где U1 – напряжение логической единицы на выходе ключа.

При высоком входном напряжении uвх = U1 > Uпор транзистор открыт, состояние ключа соответствует точке В (рис. 1, б).

Увеличивая сопротивление Rc , можно уменьшить наклон нагрузочной прямой АВ, которая соответствует уравнению , и сделать остаточное напряжение как угодно малым (рис. 1, б). Это одно из важнейших преимуществ ключей на МДП-транзисторах перед биполярными ключами. Остаточное напряжение ключа с резисторной нагрузкой определяется выражением

, (1)

где – удельная крутизна; S – крутизна МДП-транзистора.

Ключи на МДП-транзисторах с динамической нагрузкой

В ключе с динамической нагрузкой (рис. 2, а) транзистор VT1 называется активным (управляющим), а транзистор VT2 – нагрузочным. Транзистор VT2 включен вместо резистора Rc, причем его затвор может быть соединен с источником питания Ес либо подключен к отдельному источнику смещения.

Рассмотрим случай, когда затвор нагрузочного транзистора VD2 подключен к источнику питания +Ec , т.е. uзи2 = uси2. При низком потенциале на входе uвх= U0 < Uпор1 транзистор VТ1 закрыт, поэтому токи ic1 = ic2 = 0. На выходе через открытый транзистор VТ2 устанавливается высокий потенциал uвых= U1, значение которого может находиться в пределах от Ес до Ес–Uпор2 (здесь Uпор2 – пороговое напряжение транзистора VТ2, зависящее от напряжения между истоком и подложкой).

При увеличении входного напряжения до значения U1 > Uпор1 транзистор VT1 открывается, его рабочая точка В находится на пересечении выходной характеристики транзистора VT1 для uзи1= U1 и линии нагрузки. Линия нагрузки строится по уравнению

. (2)

Задаваясь значениями uзи2 = uси2 , по статическим характеристикам транзистора находим соответствующие значения тока ic2 = ic1 , а по уравнению (2) – значения uси1 . Тогда получаем координаты точек (uси1 , iс1) линии нагрузки.

Важной характеристикой ключа является передаточная характеристика uвых = f(uвх) (рис. 3).

В схеме (см. рис. 2, а) минимальное значение уровня логической единицы на выходе . Для получения малых значений уровня логического нуля рабочая точка В транзистора VT1 при (см. рис. 2, б) должна находиться на крутом участке выходной характеристики. Транзистор VT2 работает на пологих участках выходных характеристик. Для уменьшения Uост крутизна нагрузочного транзистора Sуд2 должна быть намного меньше, чем крутизна активного транзистора Sуд1 .

Значения входного напряжения uвх , при которых модуль коэффициента усиления ключа , называются порогами переключения и . Область между порогами называется зоной неопределённости.

Минимальное допустимое значение потенциальной помехи, не вызывающее ложного переключения, называется помехоустойчивостью (к положительной и отрицательной помехе):

. (3)

Примеры построения других логических элементов на МОП-транзисторах

КМОП(КМДП)-структуры

КМОП (комплементарная логика на транзисторах металл-оксид-полупроводник) или КМДП (комплементарная логика на транзисторах металл-диэлектрик-полупроводник) – технология построения электронных схем, в которой используются полевые транзисторы с изолированным затвором с каналами разной проводимости.

Комплементарный = дополнительный, добавочный, дополняющий.

CMOS = Complementary(-symmetry) Metal-Oxide-Semiconductor

Технология CMOS используется в персональных компьютерах для хранения настроек базовой системы ввода-вывода BIOS (Basic Input-Output System).

Отличительной особенностью схем КМОП по сравнению с биполярными технологиями (ТТЛ, ЭСЛ и др.), используемыми для создания логических элементов, является очень малое энергопотребление в статическом режиме (в большинстве случаев можно считать, что энергия потребляется только во время переключения состояний).

Отличительной особенностью структуры КМОП по сравнению с другими МОП-структурами (n-МОП, p-МОП) является наличие как n-, так и p-канальных полевых транзисторов; как следствие – КМОП-схемы обладают более высоким быстродействием и меньшим энергопотреблением, однако при этом характеризуются более сложным технологическим процессом изготовления и меньшей плотностью упаковки.

Подавляющее большинство современных логических микросхем, в том числе, процессоров, используют схемотехнику КМОП.

История

Схемы КМОП в 1963 г. изобрёл Фрэнк Вонлас (Frank Wanlass) из компании Fairchild Semiconductor, первые микросхемы по технологии КМОП были созданы в 1968 г. Долгое время КМОП рассматривалась как энергосберегающая, но медленная альтернатива ТТЛ, поэтому микросхемы КМОП нашли применение в электронных часах, калькуляторах и других устройствах с батарейным питанием, где энергопотребление было критичным.

К 1990 г. с повышением степени интеграции микросхем встала проблема рассеивания энергии на элементах. В результате технология КМОП оказалась в выигрышном положении. Со временем были достигнуты приемлемые скорость переключения и плотность монтажа, недостижимые в технологиях, основанных на биполярных транзисторах.

Ранние КМОП-схемы были очень уязвимы к электростатическим разрядам. Сейчас эта проблема в основном решена, но при монтаже КМОП-микросхем рекомендуется принимать меры по снятию электрических зарядов.

Для изготовления затворов в КМОП-ячейках на ранних этапах применялся алюминий. Позже, в связи с появлением так называемой самосовмещённой технологии, которая предусматривала использование затвора не только как конструктивного элемента, но одновременно как маски при получении сток-истоковых областей, в качестве затвора стали применять поликристаллический кремний.

Примеры логических элементов на КМОП-технологии

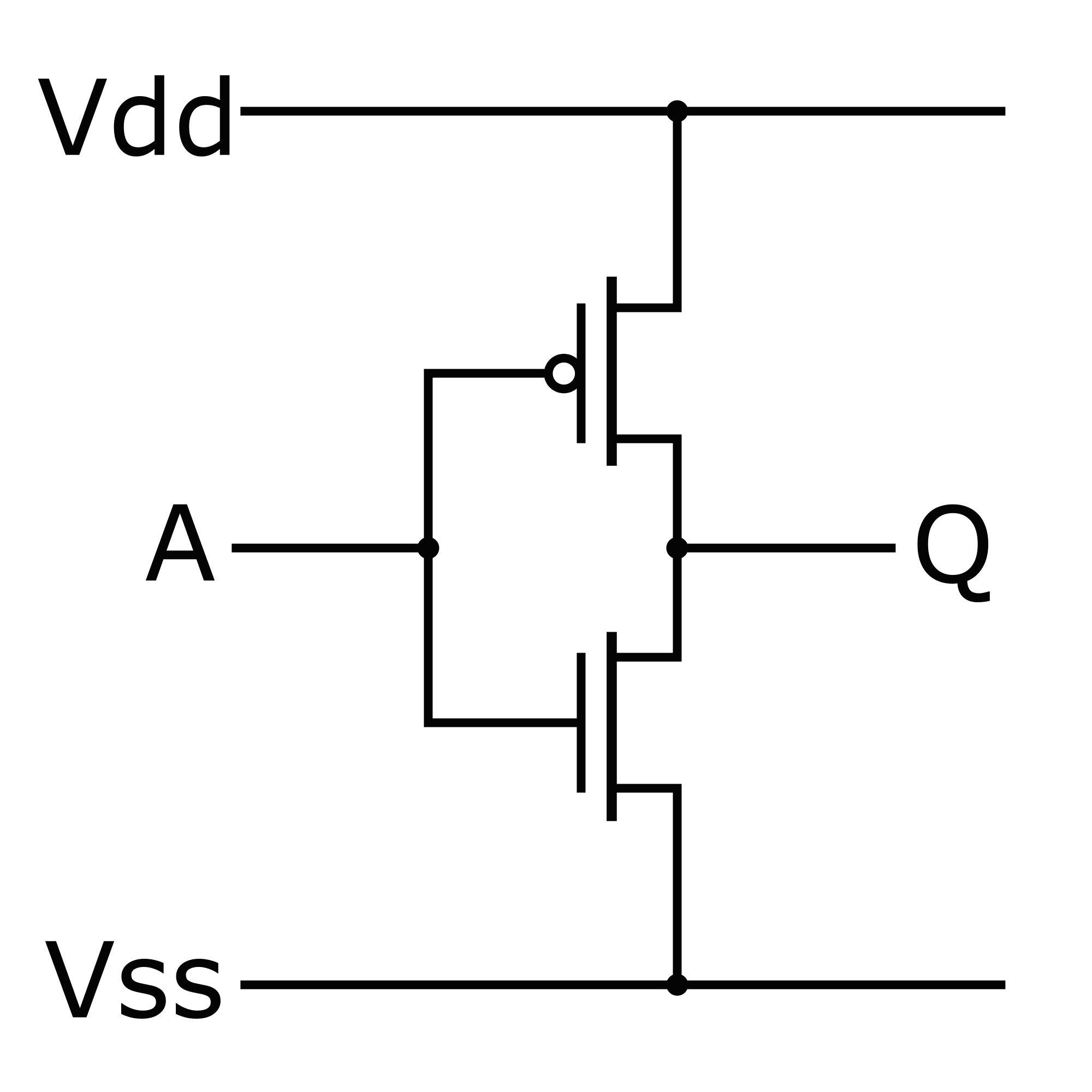

1. Логический инвертор (логический элемент НЕ)

Комплементарный ключ (рис. 5, а) строится на транзисторах с каналами разных типов. Когда потенциал uвх = U0 < Uпор1 , n-канальный транзистор VT1 закрыт, а p-канальный транзистор VT2 открыт и работает на крутом участке выходной характеристики. При увеличении потенциала на входе до уровня uвх = Uпор1 открывается транзистор VT1. В схеме начинает протекать ток

.

Падение напряжения uси2 увеличивается, но рабочая точка транзистора VT2 находится на крутом участке характеристики, поэтому уменьшение выходного напряжения uвых = Ес – uси2 незначительно. При дальнейшем увеличении uвх рабочая точка транзистора VT2 попадает на пологие участки выходных характеристик, потребляемый от источника ток достигает значения

.

Падение напряжения uси2 возрастает, а потенциал uвых падает.

Когда потенциал uвх достигает значения , запирается транзистор VT2 и на выходе устанавливается потенциал uвых = U0 = 0.

Практически остаточное напряжение на комплементарном ключе может быть уменьшено до нескольких микровольт. Ширина зоны неопределённости мала: 0,1 В. При типовых значениях пороговых напряжений Uпор1 , Uпор2 = 2-3 В помехоустойчивость , составляет 2 В и более. Напряжение питания выбирается из условия Ес > Uпор1 + Uпор2 .

Важным преимуществом комплементарного ключа является то, что ток и мощность, потребляемые от источника в статических состояниях, практически равны нулю.

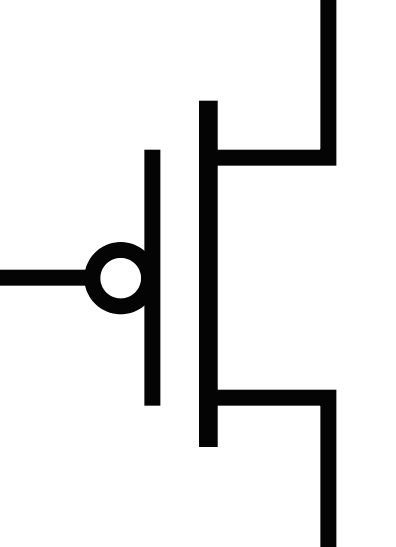

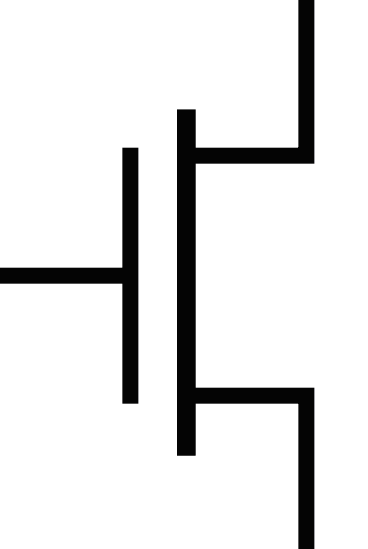

– упрощённое условное обозначение ПТ с p-каналом

– упрощённое условное обозначение ПТ с p-каналом

(открывается при отрицательном или нулевом напряжении Uзи)

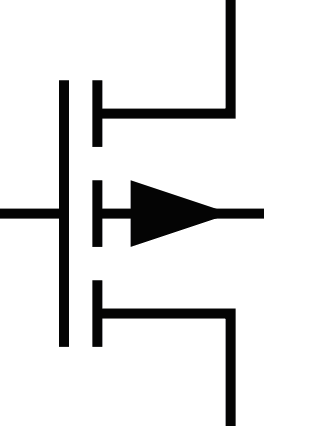

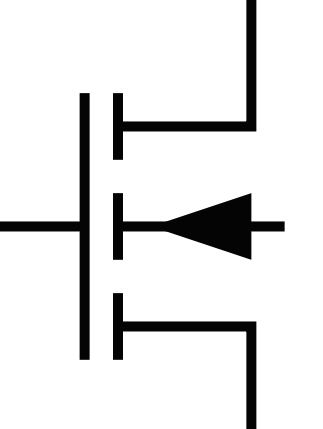

– упрощённое условное обозначение ПТ с n-каналом

– упрощённое условное обозначение ПТ с n-каналом

(открывается при положительном напряжении Uзи)

Рис. 6. Схема статического КМОП-инвертора

Обозначения напряжений питания:

1) положительное напряжение питания:

VCC (БПТ) (Collector – коллектор)

VDD (ПТ) (Drain – сток)

1) отрицательное напряжение питания или «земля»:

VEE (БПТ) (Emitter – коллектор)

VSS (ПТ) (Source – исток)

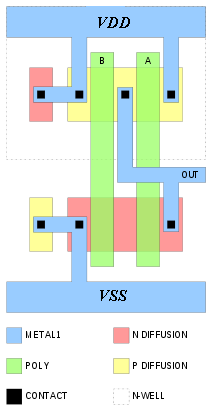

Рис. 7. Структура планарного КМОП-инвертора (вид сверху)

? затвор (управляющий вход) должен быть снизу

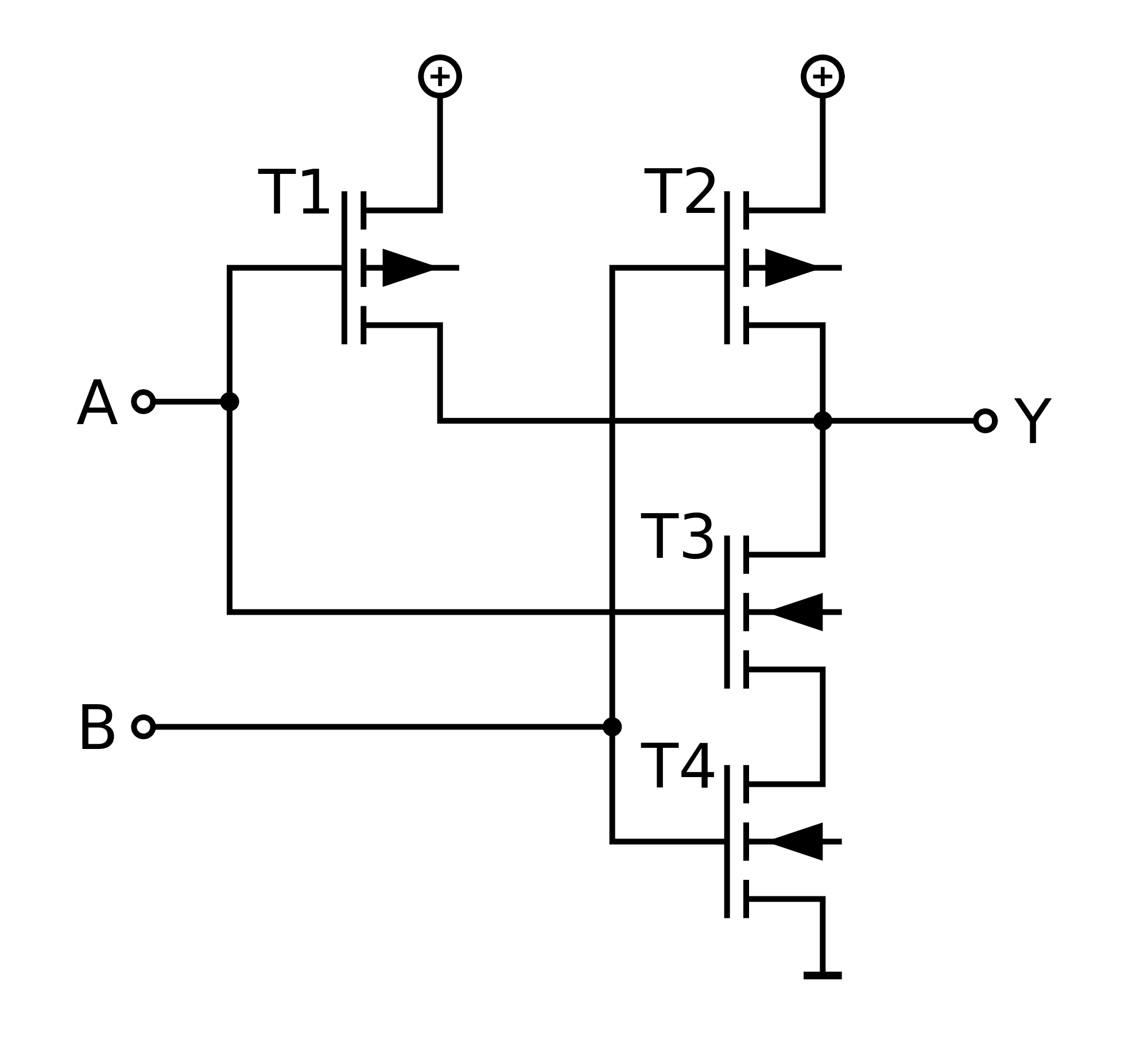

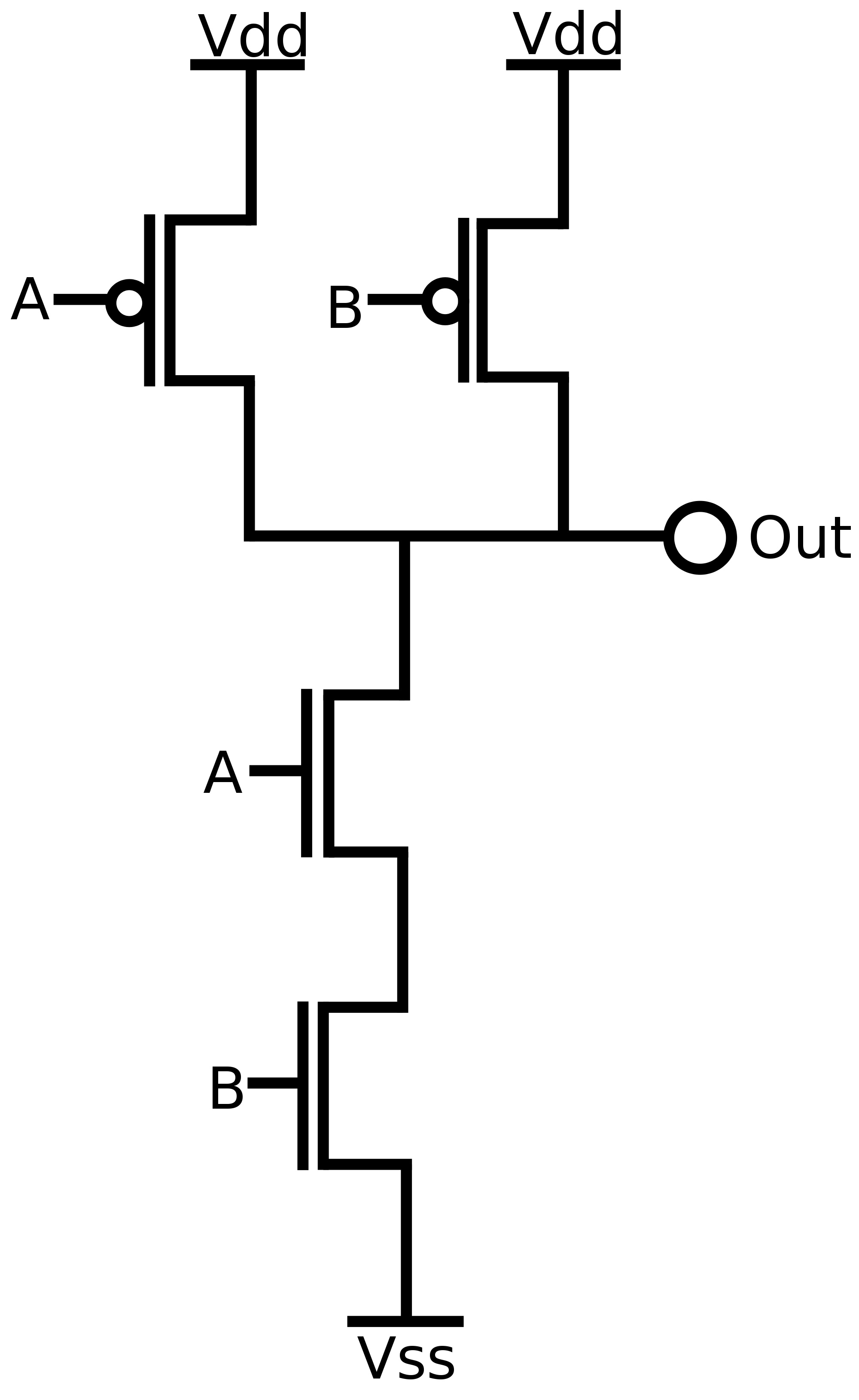

2. Логический элемент (вентиль) 2И-НЕ

а б

Рис. 8. Схема логического элемента 2И-НЕ на КМОП-технологии:

с обычным (а) и упрощенным (б) изображением МОП-транзисторов

- Если на оба входа A и B подан высокий уровень, то оба транзистора снизу на схеме открыты, а оба верхних закрыты, то есть выход соединён с землёй.

- Если хотя бы на один из входов подать низкий уровень, соответствующий транзистор сверху будет открыт, а снизу закрыт. Таким образом, выход будет соединён с напряжением питания и отсоединён от земли.

В схеме нет никаких нагрузочных сопротивлений, поэтому в статическом состоянии через КМОП-схему протекают только токи утечки через закрытые транзисторы, и поэтому энергопотребление очень низкое. При переключениях электрическая энергия тратится в основном на заряд ёмкостей затворов и проводников, так что потребляемая (и рассеиваемая) мощность пропорциональна частоте этих переключений (например, тактовой частоте процессора).

На рис. 8 с топологией микросхемы 2И-НЕ можно заметить, что в ней используются два двухзатворных полевых транзистора разных конструкций.

Верхний двухзатворный полевой транзистор выполняет логическую функцию 2ИЛИ, а нижний двухзатворный полевой транзистор выполняет логическую функцию 2И.

Серии и семейства логических КМОП-микросхем зарубежного производства

На КМОП-транзисторах (CMOS):

- 4000 – CMOS с питанием от 3 до 15В, 200 нс;

- 4000B – CMOS с питанием от 3 до 15В, 90 нс;

- 74C – семейство в серии 7400, аналогичное 4000B;

- 74HC – Высокоскоростное CMOS, по скорости аналогично семействам LS, 12 нс;

- 74HCT – Высокоскоростное, совместимо по выходам с биполярными сериями;

- 74AC – Улучшенное CMOS, скорость в целом между семействами S и F;

- 74ACT – Улучшенное CMOS, совместимо по выходам с биполярными сериями;

- 74AHC – Улучшенное высокоскоростное CMOS, втрое быстрее HC;

- 74AHCT – Улучшенное высокоскоростное CMOS, совместимо по выходам с биполярными сериями;

- 74ALVC – с низким напряжением питания (1,65 – 3,3В), время срабатывания 2 нс;

- 74AUC – с низким напряжением питания (0.8 – 2,7В), время срабатывания < 1,9 нс при Vпит=1,8В;

- 74FC – быстрое CMOS, скорость аналогична F;

- 74FCT – быстрое CMOS, совместимо по выходам с биполярными сериями;

- 74LCX – CMOS с питанием 3В и 5В-совместимыми входами;

- 74LVC – с пониженным напряжением (1,65 – 3.3В) и 5В-совместимыми входами, время срабатывания < 5,5 нс при Vпит=3,3V, < 9 нс при Vпит=2,5В;

- 74LVQ – с пониженным напряжением (3,3В);

- 74LVX – с питанием 3,3В и 5В-совместимыми входами;

- 74VHC – Сверхвысокоскоростное CMOS-семейство – быстродействие сравнимо с S;

- 74VHCT – Сверхвысокоскоростное CMOS, совместимая по выходам с биполярными сериями;

- 74G – Супер-сверхвысокоскоростное для частот выше 1 ГГц, питание 1,65В – 3,3В, 5В-совместимые входы;

BiCMOS

- 74BCT – BiCMOS, TTL-совместимые входы, используется для буферов;

- 74ABT – Улучшенное BiCMOS-семейство, TTL-совместимые входы, быстрее ACT и BCT.

Для более гибкого применения у ряда производителей существуют также особые семейства, в которых каждая ИМС включает всего 1 логический элемент в 5..6-ти пиновом корпусе, что бывает полезно для конструкций с малым количеством разных элементов и минимальным размером платы.

Например: 74LVC1G00GW SOT353-1 Single 2-Input Positive-AND Gate (NXP).

Серии логических КМОП-микросхем отечественного производства

На КМОП-транзисторах (CMOS):

- 164, 176 соответствуют серии 4000, но у 164 и 176 cерий напряжение питания 5…12 В (номинальное значение 9 В);

- 561 и 564 – семейству 4000A из серии 4000;

- 1554 – семейству 74AC из серии 7400;

- 1561 – семейству 4000B;

- 1564 – семейству 74HC;

- 1594 – семейству 74ACT;

- 5564 – семейству 74HCT;

- 5584 – семейству 74НС;

- 5514БЦ – серия отечественных логических микросхем на основе БМК. Предназначена для замены устаревших логических микросхем серий

564, 1564 и их зарубежных аналогов.

Переходные процессы в ключах на МДП-транзисторах

Инерционность ключей на МДП-транзисторах обусловлена главным образом перезарядом суммарной паразитной ёмкости Сп , типичные значения которой составляют 1-10 пФ.

При подаче на вход положительного перепада напряжения uвх = U1 транзистор VT1 в схемах открывается. Начинается разряд ёмкости Сп через открытый транзистор VT1, состояние которого в начале спада соответствует точке В0 (рис. 9, б). Для приближённой оценки длительности спада tc пренебрежём влиянием тока в резисторе Rc и в транзисторе VT2, так как в начале спада этот ток значительно меньше тока управляющего транзистора Ic0 . Тогда на интервале спада справедливо нелинейное дифференциальное уравнение

,

где ic(ucи) – выходная характеристика транзистора VT1 для .

Если принять, что ёмкость Сп разряжается постоянным током Ic0 , то получается заведомо заниженное значение длительности спада:

.

Если предположить, что ёмкость разряжается на постоянное сопротивление , то и получается заведомо завышенное значение:

.

Для расчетов можно принять промежуточное из двух полученных значений

, (4)

где начальное значение тока

.

Когда потенциал на входе ключа uвх становится меньше порогового значения Uпор1, транзистор VT1 запирается и ёмкость Сп начинает заряжаться в ключе с резисторной нагрузкой через резистор Rc (а в ключах с динамической нагрузкой и комплементарном транзисторе – через транзистор VТ2). В ключе с резисторной нагрузкой длительность фронта импульса напряжения определяется выражением

, (5)

где – ток открытого ключа, причем Ic Ic0.

В схеме с динамической нагрузкой при одинаковых значениях Ic заряд ёмкости Сп происходит медленнее, а время tф больше, чем при резисторной нагрузке.

Из сравнения формул (4), (5) следует, что в ключах с резисторной и динамической нагрузками отношение длительности фронта и спада удовлетворяет условию:

,

т.е. длительность фронта намного превышает длительность спада. Попытка уменьшить отношение увеличением тока открытого ключа Ic приводит к увеличению остаточного напряжения.

В комплементарном ключе ёмкость Сп заряжается через открытый транзистор VТ2. С учетом выражения, аппроксимирующего характеристику транзистора VT2 на пологом участке, получаем, что ёмкость Сп заряжается током:

,

где U0 0. Полагая, что процесс заряда емкости завершается при ucи = U1, получаем:

. (6)

Эта формула даёт заведомо заниженное значение длительности фронта, поскольку при уменьшении напряжения ucи2 = Ec – ucи до напряжения насыщения ток транзистора VT2 начинает уменьшаться. Поэтому, как и в формуле (4), рекомендуется вводить поправочный коэффициент, равный 1,5.

Транзисторные Электронные ключи