Основы цифровой схемотехники

PAGE 173

Курс лекций Техническая электроника

Лекция 26

ОСновы цифровой схемотехники

26.1 логические элементы

В цифровых вычислительных машинах, устройствах автоматики и обработки информации используют устройства, осуществляющие логические операции.

Логическая операция - это преобразование по правилам алгебры логики (или булевой алгебры) входной цифровой информации в выходную.

Простейшее в функциональном отношении логическое устройство, выполняющее одну определенную логическую операцию над входными сигналами, называют логическим элементом.

В алгебре логики истинность суждения или высказывания о результатах той или иной логической операции обозначают символом 1, ложность - 0. Таким образом, логические переменные в алгебре логики принимают лишь два значения: единицу и нуль. Их называют двоичными переменными. Чтобы реализовать алгебру логики на электронных элементах, необходимо значение параметров этих элементов перевести на язык алгебры логики (0 или 1). Задавать значения параметров можно уровнем напряжения или полярностью импульсов.

Если сигналы подают в виде высокого (положительной или отрицательной полярности) и низкого (близкого к нулю) уровня напряжения, то такой способ подачи сигнала называют потенциальным. Если высокому уровню напряжения U1 приписывают значение "единица", а низкому U° - "нуль", то логику называют положительной (позитивной), в противном случае - отрицательной (негативной). Разность уровней единицы и нуля называют логическим перепадом Uл = U1 - U0. Он должен быть значительным, иначе нельзя будет четко отделить один уровень от другого.

Если сигналы подают в импульсной форме, то такой способ подачи сигнала называют импульсным. При этом логической единице соответствует наличие импульса, логическому нулю - отсутствие импульса (положительная логика). Сигналы, соответствующие 1 (или 0), могут быть на входе и выходе разными. Наибольшее распространение получили потенциальные логические элементы, так как их можно изготовлять по технологии интегральных микросхем.

Элементарные логические операции и типы логических элементов.

Система логических элементов, на базе которой можно строить логическую схему любой сложности, называется функционально полной. Основными и наиболее простыми логическими элементами являются элементы, выполняющие операции отрицания (НЕ), конъюнкции (И), дизъюнкции (ИЛИ). Они составляют функционально полную систему и являются системой минимального базиса. Каждая из этих операций и логических элементов имеет и другое название (табл. 26.1).

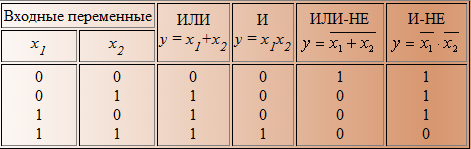

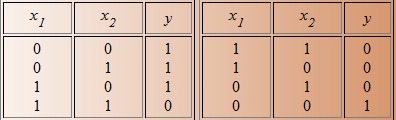

Таблица 26.1 Таблица истинности четырёх логических элементов

В этой таблице даны названия логических элементов, обозначение данной операции, показано, как читается запись операции, обозначаются логические элементы в функциональных схемах, а также таблица истинности для случая, когда имеется два входа и один выход. Таблица истинности содержит правила и результат выполнения операций. В каждой ее строке записывают состояние сигналов на входах (х1, х2) и результат логической операции на выходе (у). В общем случае логический элемент может иметь n входов и n выходов.

Функционально полную систему могут обеспечить составные (комбинированные) логические элементы, выполняющие логические операции И - НЕ, ИЛИ - НЕ. Их названия, обозначения также даны в табл. 26.1.

Логические элементы выполняют как на дискретных приборах, так и методами интегральной технологии. Для большинства серий интегральных микросхем базисной системой являются составные логические элементы И - НЕ или ИЛИ - НЕ. Их выпускают в виде отдельных микроминиатюрных устройств в герметичном корпусе.

Рассмотрим логические элементы на полупроводниковых приборах. Логические элементы И и ИЛИ могут выполняться на резисторах, диодах, биполярных и полевых транзисторах и туннельных диодах. Элемент НЕ выполняется на транзисторах.

Составные логические элементы на разных ступенях могут выполняться на различных приборах (резисторах, диодах, транзисторах, как биполярных, так и полевых), т. е. могут иметь разные схемные варианты. В соответствии с конструкцией их называют логикой типа резисторно-транзисторной (РТЛ); диодно-транзисторной (ДТЛ); транзисторно-транзисторной (на биполярных транзисторах - ТТЛ; на полевых - р-канальная МОПТЛ, n-канальная МОПТЛ; на комплементарных полевых транзисторах - КМОП или КМОПТЛ; на транзисторах с эмиттерными связями - ТЛЭС или ЭСЛ).

Специфической логикой на транзисторах является инжекционная логика - И2Л, она не имеет аналогов в транзисторных схемах на дискретных элементах. Связь между ступенями логических элементов осуществляется либо непосредственно, либо через резистор, либо через RC-цепочку. Тогда в название логики добавляют соответствующие буквенные обозначения: НСТЛ - транзисторная логика с непосредственной связью; НСТЛМ - транзисторная логика с непосредственной связью на МОП-транзисторе; РЕТЛ - транзисторная логика с резистивно-емкостной связью.

Основные логические элементы в дискретном исполнении.

Логический элемент НЕ (табл. 26.1) имеет один вход и один выход и выполняет операцию НЕ. Он представляет собой усилительный каскад на биполярном или полевом транзисторе, работающий в ключевом режиме. На рис. 26.1 показан элемент НЕ на биполярном npn транзисторе, включенном по схеме с ОЭ.

Элемент предназначен для работы с сигналами положительной полярности в положительной логике. Транзистор T закрыт отрицательным потенциалом на базе, подаваемым от источника ЕБ. При подаче на вход элемента сигнала низкого уровня Uвх = U0, соответствующего логическому 0, транзистор остается закрытым, коллекторный ток равен нулю, т. е. через резистор RK ток не проходит и на выходе напряжение Uвых = +EK, т. е. высокого уровня U1, соответствующего логической 1.

При высоком уровне напряжения на входе Uвх = U1 транзистор находится в режиме насыщения, появляется коллекторный ток и на резисторе RK создается падение напряжения, примерно равное EK, а на выходе напряжение примерно равно нулю (Uвых = U0), т. е. будет логический нуль. Итак, если х = 0, то y = 1, если x = 1, то y = 0, т. е. элемент является инвертором - выполняет операцию отрицания.

Замечание: Следует отметить, что если элемент выполнен на кремниевом транзисторе n-р-n-структуры, источник смещения EБ можно не включать, так как и при положительных потенциалах на базе (до 0,6 В) транзистор практически закрыт.

Логический элемент И (табл. 26.1)

может иметь два (или более) входа и один выход и работать как при потенциальных, так и импульсных сигналах. Аналогом его может служить схема из последовательно включенных контактов реле. Рассмотрим работу элемента И, выполненного на диодах.

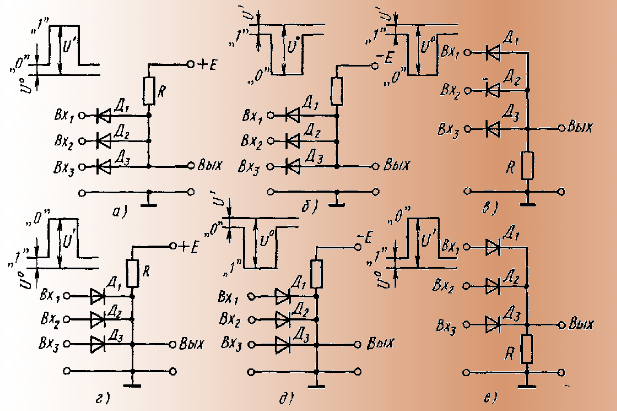

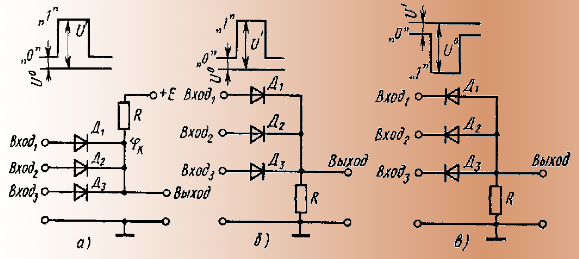

Элемент, предназначенный для работы с сигналами в виде напряжений (или импульсов) положительной полярности в положительной логике, показан на рис. 26.3, а. Он имеет три входа и один выход. Элемент реализует операцию И, если сигнал 1 появляется на выходе только тогда, когда одновременно на всех входах присутствует сигнал 1. При этом, если хотя бы на одном входе присутствует сигнал, соответствующий логическому нулю, он должен передаваться через открытый диод на выход и обеспечивать запирание тех диодов, на которые со стороны входа воздействуют сигналы, соответствующие логической 1. Будем считать, что сопротивление открытого диода Rдоткр << R, а потенциалы сигнала и источника питания E схемы имеют значения, удовлетворяющие соотношению U0 < Е < U1.

Если на одном из входов цепи, например Bх1 действует сигнал U0, то диод Д1 будет открыт и ток пройдет по цепи +E, резистор R, диод Д1, источник U0. Все напряжение источника Е приложится к резистору R и на выходе напряжение окажется равным U0, т. е. сигнал на выходе - логический нуль. На остальных входах действует высокий потенциал U1, поэтому диоды закрыты, так как их анод подсоединен к зажиму на выходе с низким потенциалом U0, а катоды - к высокому положительному потенциалу U1.

Если на всех входах действует напряжение U1, то все диоды будут закрыты, ток в цепи +EK, R, закрытый диод, источник U1 не проходит и падение напряжения на резисторе R равно нулю. На выходе напряжение E > U0, что соответствует логической 1. Таким образом, если хотя бы на один из входов воздействует сигнал, соответствующий логическому нулю, сигнал на выходе также соответствует логическому нулю. Сигнал на выходе соответствует логической 1 только если сигналы на всех входах соответствуют логической единице.

На рис. 26.3,б, г, д показаны элементы, предназначенные соответственно для работы с сигналами отрицательной полярности в положительной логике, положительной (рис. 26.3, г) и отрицательной (рис. 26.3, д) полярности в отрицательной логике. Отметим, что один и тот же элемент может работать как от положительных, так и от отрицательных сигналов, но полярность включения источника питания для положительных сигналов должна быть положительной (+E), для отрицательных сигналов - отрицательной (-E). Работают элементы так же, как и элемент на рис. 26.3, а. Наиболее распространены элементы, показанные на рис. 26.3, а, д.

Элемент И может работать и без источника питания. В этом случае возможны только два варианта включения диода, причем элемент на рис. 26.3, в реализует операцию И только от сигналов отрицательной полярности в положительной логике, а элемент на рис. 26.3, е - только от сигналов положительной полярности в отрицательной логике. Элементы без источника питания менее предпочтительны, чем с источником питания.

Логический элемент ИЛИ (табл. 26.1)

может иметь два (и более) входа, один выход и работать как при потенциальных, так и при импульсных сигналах. Аналогом его может служить схема из параллельно включенных реле.

Рассмотрим элемент ИЛИ, выполненный на диодах и предназначенный для работы от сигналов в виде напряжений (импульсов) положительной полярности в положительной логике. Для того чтобы элемент реализовал операцию ИЛИ, необходимо, чтобы сигнал на выходе имел значение 1 только тогда, когда хотя бы на одном из входов действует сигнал 1. При этом сигнал 1 на входе должен обеспечивать запирание всех диодов, на которые со стороны входа воздействует сигнал 0. Соотношение потенциалов источника сигналов низкого U0 и высокого U1 уровней и источника питания Е схемы такое же, как и в схеме элемента И: U0 < E < U1 (если U1 < E, то диоды будут всегда закрыты и выходное напряжение не будет изменяться). Сопротивление диода в открытом состоянии RДоткр 0.

Если на все входы подано низкое напряжение U0, все диоды закрыты, так как потенциал их анодов ниже потенциала катодов (K = -E); следовательно, напряжение на выходе равно E < U1, т. е. на выходе сигнал соответствует логическому 0. При подаче хотя бы на один из входов, например Вх1, высокого напряжения U1 откроется диод Д1, который подключен к этому входу, а так как сопротивление открытого диода равно нулю, то потенциал K = +U1 и на выходе имеется сигнал U1 (логическая 1). Если в это время на какие-то диоды со стороны входа будет подан низкий потенциал U0, они окажутся закрытыми, так как их катодам сообщится потенциал K = +U1. Таким образом, на выходе сигнал будет соответствовать логической 1, если хотя бы на одном из входов (или первом, или втором, или третьем) сигнал соответствует логической 1.

Сравним рис. 26.5, а, на котором показан элемент ИЛИ, предназначенный для работы от сигналов положительной полярности в отрицательной логике, с рис. 26.3, г. Они одинаковы. Таким образом, можно отметить, что элемент ИЛИ в положительной логике может выполнить операцию И в отрицательной логике, и наоборот. Все элементы И на рис. 26.3 в другой логике, чем для элемента И, реализуют операцию ИЛИ.

Элемент ИЛИ, как и элемент И, может не содержать источника питания. Элемент на рис. 26.5,б предназначен для работы от сигналов положительной полярности в положительной логике, а на рис. 26.5, в - от сигналов отрицательной полярности в отрицательной логике. Сравнение этих элементов ИЛИ с элементами И на рис. 26.3, в, е подтверждает, что оба элемента могут выполнять обе операции: и И, и ИЛИ; элемент И (ИЛИ) - в положительной логике, в отрицательной логике - ИЛИ (И).

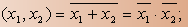

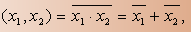

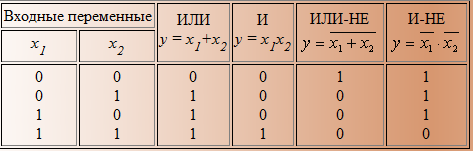

Операции ИЛИ - НЕ и И - НЕ образуются путем инверсии результатов, получаемых при выполнении операции ИЛИ и И соответственно:

ИЛИ - НЕ  (26.1)

(26.1)

И - НЕ  (26.2)

(26.2)

что видно из таблицы истинности для двух входных элементов (табл. 26.2).

Таблица 26.2 - таблица истинности для двух входных элементов

Элемент, выполняющий операцию И - НЕ в положительной логике (табл. 26.3), в отрицательной логике выполнит операцию ИЛИ - НЕ (табл. 26.4).

Таблица 26.3 Таблица 26.4

Логические элементы в интегральном исполнении предназначают для работы с сигналами в потенциальной форме. Они могут выполняться по логике разных типов. Тип логики влияет на характеристики элемента. В интегральных биполярных микросхемах чаще используют кремниевые транзисторы n-p-n-типа (см. замечание к элементу НЕ). В режиме насыщения напряжение между эмиттером и коллектором таких транзисторов сравнительно велико (0,4 В и выше).

Лекция 27

ОСновы цифровой схемотехники

27.1 логические элементы на транзисторах

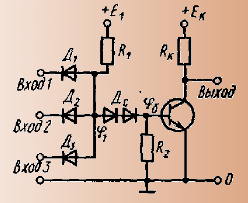

Логический элемент И - НЕ диодно-транзисторной логики (ДТЛ). Входные сигналы подаются на элемент И, выходной сигнал снимается с элемента НЕ. Таким образом, на выходе элемента И - НЕ сигналом будет логическая 1, если на входе элемента НЕ присутствует сигнал, соответствующий логическому 0. Чтобы это имело место, хотя бы на один вход элемента И должен быть подан сигнал, соответствующий логическому 0. Логический элемент И - НЕ для сигналов положительной полярности показан на рис. 27.1. Он представляет собой соединение через диоды Дс двух элементов: диодного элемента И и транзисторного элемента НЕ (см. соответственно рис. 26.3, а и рис. 26.1, на которых показаны элементы НЕ и И). При этом элемент "НЕ" не имеет источника смещения EБ, исходя из сделанного ранее замечания о работе кремниевых транзисторов. Кроме того, значения напряжений, соответствующих логическим 0 и 1, необходимо выбрать должным образом, так как при напряжении на базе, несколько меньшем 0,6В, транзистор будет закрыт, а в режиме насыщения напряжение между эмиттером и коллектором равно 0,4 В (и выше).

Рассмотрим работу элемента. Если на все входы подано напряжение U1 (логическая 1), все диоды (Д1 Д2, Д3) будут закрыты и ток в цепи источник E1, резистор R1, открытые диоды Дc пройдет в базу транзистора. Вследствие падения напряжения на резисторе R1 потенциал 1 окажется несколько ниже потенциала +E1, диод Д1 будет открыт и потенциал базы Б транзистора меньше потенциала 1 на значение падения напряжения на диодах Дc (но выше 0,6В, так что транзистор будет находиться в режиме насыщения). На выходе элемента НЕ установится низкое напряжение U0, соответствующее логическому 0. Если хотя бы на один вход, например Вх1, будет подано напряжение U0, то соответствующий диод Д1 будет открыт и потенциал 1 будет U0. Ток от источника E1 будет проходить через резистор R1. Часть тока замкнется через открытый диод Д1; источник U0, источник E1, часть - через смещающие диоды Дc, резистор R2 и источник E1. Потенциал базы Б = UБЭ будет ниже потенциала 1 на значение падения напряжения на смещающих диодах Дc. При этом элемент рассчитывают таким образом, чтобы падение напряжения на диодах Дc было таким, чтобы Б = UБЭ > 0, но значительно меньше 0,6В. В этом случае транзистор будет закрыт и на выходе элемента НЕ напряжение окажется равным EK > U0, т. е. получим логическую 1.

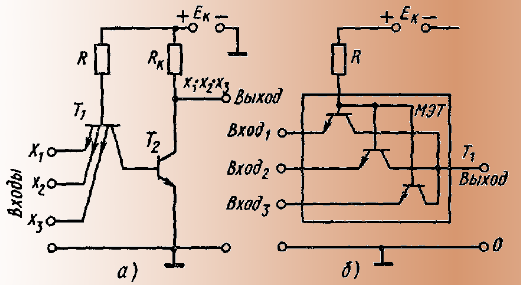

Логический элемент И - НЕ транзисторно-транзисторной логики (ТТЛ). Простейший элемент И - НЕ показан на рис. 27.2, а. Он состоит из двух частей: элемента И на многоэмиттерном транзисторе Т1 и элемента НЕ на транзисторе Т2. Связь непосредственная: коллектор Т1 соединен с базой транзистора Т2. Смещение в цепи базы транзистора Т2 выполняет коллекторный переход Т1. Три эмиттерных перехода Т1 подключенных к входу элемента (рис. 27.2,б), выполняют функции входных диодов в схеме И на диодах.

По сравнению с ДТЛ-элементами элементы ТТЛ обладают более высоким быстродействием. Элемент выполнен по технологии интегральных микросхем, поэтому он не содержит реактивных элементов. Он работает от сигналов в виде напряжений положительной полярности.

Рассмотрим принцип работы подобных элементов. Если на все входы подать напряжение U1, то все эмиттерные переходы сместятся в обратном направлении. Потенциал коллектора транзистора Т2 окажется близким нулю, переход база - коллектор смещен в прямом направлении за счет источника +EK. Транзистор T1 будет в инверсном режиме, транзистор Т2 - в режиме насыщения. Коллекторный ток транзистора T1 втекает в базу транзистора Т2, оставляя последний в режиме насыщения. Таким образом, на выходе будет напряжение низкого уровня U0, т. е. логический 0.

Если на один из входов подано напряжение U0, то потенциал базы транзистора T1 станет выше потенциалов эмиттера и коллектора, поэтому T1 окажется в режиме насыщения и ток базы замкнется через эмиттерные переходы T1 и не поступит в его коллектор, а следовательно, и в базу T2. Поэтому транзистор T2 будет закрыт, а на его выходе - напряжение высокого уровня (логическая 1). Таким образом, элемент выполняет операцию И - НЕ, так как сигнал логического нуля на выходе может быть только тогда, когда на все входы будет подан сигнал логической единицы.

27.2.1 Логический элемент ИЛИ - НЕ п-канальной МОП-транзисторной логики (МОПТЛ). В логических схемах на полевых транзисторах используют только МОП-транзисторы с диэлектриком SiO2. Основные преимущества схем на МОП-транзисторах по сравнению с другими схемами - высокая степень интеграции и повышенная помехоустойчивость.

Рассмотрим схему ИЛИ - НЕ на МОП-транзисторе с индуцированным n-каналом (рис. 27.3). В отличие от рассмотренных ранее схем в ней вместо нагрузочного резистора RK имеется МОП-транзистор (на схеме рис. 27.3 он обозначен ТK). Это связано с тем, что нагрузочный резистор сильно увеличил бы площадь схемы. Логические транзисторы Т1 и Т2 включены параллельно. Входное напряжение на каждом из них равно напряжению затвора: UВХ1 = UЗИ1, UВХ2 = UЗИ2; выходное напряжение равно напряжению стока: UВЫХ = UСИ. Напряжение питания обычно выбирают в три раза большим порогового Uпор (Uпор - напряжение на затворе, при котором образуется канал).

Если Uпор = 2,0В, то логический перепад (разность между входным и пороговым напряжениями) составляет 4 В. Логические уровни соответствуют выходным напряжениям открытого и закрытого транзисторов. Если на оба входа подать напряжение меньше порогового (соответствующее логическому нулю), то транзисторы T1 и Т2 окажутся закрытыми, а ток стока - практически равным нулю. При этом ток стока нагрузочного транзистора ТK тоже будет равен нулю. Поэтому на выходе установится напряжение, близкое к напряжению источника питания ЕC и соответствующее логической 1.

Если на вход хотя бы одного транзистора подать напряжение, превышающее пороговое (соответствующее логической 1), то этот транзистор откроется и появится ток стока. Тогда на выходе схемы будет остаточное напряжение, значительно меньшее порогового, что соответствует логическому 0.

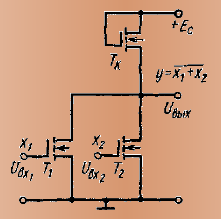

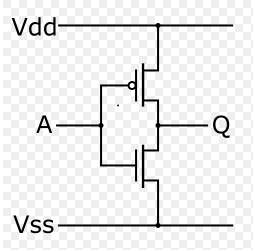

27.2.2 МОП-транзисторная логика на комплементарных транзисторах (КМОП). Отличительной особенностью схем КМОП по сравнению с биполярными технологиями (ТТЛ, ЭСЛ и др.) является очень малое энергопотребление в статическом режиме (в большинстве случаев можно считать, что энергия потребляется только во время переключения состояний). Отличительной особенностью структуры КМОП по сравнению с другими МОП-структурами (N-МОП, P-МОП) является наличие как n-, так и p-канальных полевых транзисторов (рис. 27.4); как следствие, КМОП-схемы обладают более высокой скоростью действия и меньшим энергопотреблением, однако при этом характеризуются более сложным технологическим процессом изготовления и меньшей плотностью упаковки.

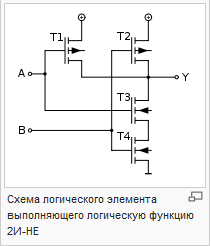

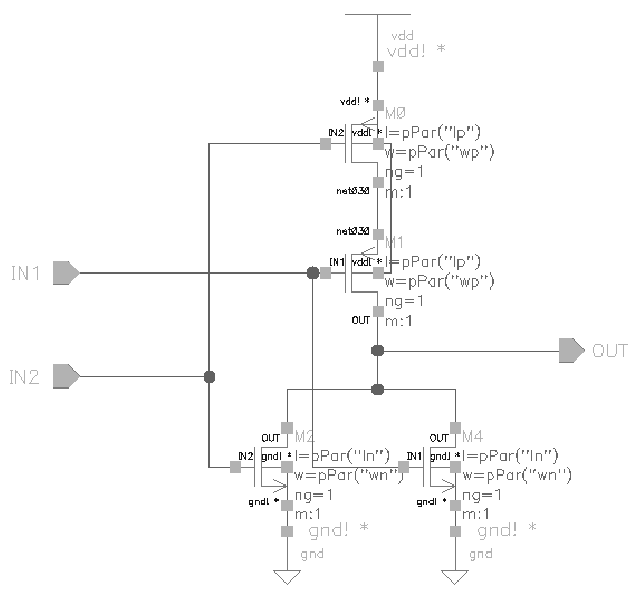

Для примера рассмотрим схему вентиля 2И-НЕ, построенного по технологии КМОП (рисунок 27.5).

Если на оба входа A и B подан высокий уровень, то оба транзистора снизу на схеме открыты, а оба верхних закрыты, то есть выход соединён с землёй.

Если хотя бы на один из входов подать низкий уровень, соответствующий транзистор сверху будет открыт, а снизу закрыт. Таким образом, выход будет соединён с напряжением питания и отсоединён от земли.

В схеме нет никаких нагрузочных сопротивлений, поэтому в статическом состоянии через КМОП-схему протекают только токи утечки через закрытые транзисторы, и энергопотребление очень низкое. При переключениях электрическая энергия тратится в основном на заряд емкостей затворов и проводников, так что потребляемая (и рассеиваемая) мощность пропорциональна частоте этих переключений (например, тактовой частоте процессора).

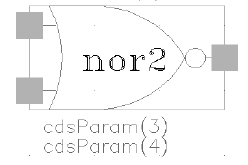

Схема 2ИЛИ-НЕ (рисунок 27.6) работает следующим образом: когда на оба входа подан низкий уровень, оба транзистора вверху открыты и на выход подаётся высокий уровень. Если на один из входов подать высокий уровень, тогда один из транзисторов снизу будет открыт и выход будет соединён с землёй.

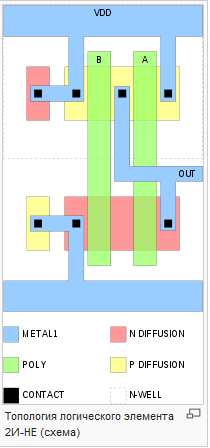

На рисунке с топологией микросхемы 2И-НЕ можно заметить, что в ней используются два двухзатворных полевых транзистора разных конструкций. Верхний двухзатворный полевой транзистор выполняет логическую функцию 2ИЛИ, а нижний двухзатворный полевой транзистор выполняет логическую функцию 2И.

Ниже приведена схема 2ИЛИ-НЕ, применяемая на ОАО "Интеграл".

Все обозначения на рисунке 27.6 взяты с библиотеки вентильного уровня ОАО "Интеграл". Там же (в библиотеке) приведены временные задержки и рассеиваеме мощности при различных нагрузках вентиля и его топоплогическая реализация.

Подавляющее большинство современных логических микросхем, в том числе, процессоров, используют схемотехнику КМОП.

Основы цифровой схемотехники