Синтез цифровой САР на основе аналогового прототипа

ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ

ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ

ВЫСШЕГО ПРОФФЕСИОНАЛЬНОГО ОБРАЗОВАНИЯ

Воронежский государственный технический университет

(ФГБОУВПО «Воронежский государственный технический университет»)

Факультет радиотехники и электроники

Кафедра конструирования и производства радиоаппаратуры

Практическая работа

по дисциплине: «Основы управления техническими системами»

на тему: «Синтез цифровой САР на основе аналогового прототипа »

Разработал студент РК- 112 Нечаев А. Ю.

(группа, подпись, дата, инициалы, фамилия)

Руководитель Самойленко Н. Э

(подпись, дата, инициалы, фамилия)

Члены комиссии ___________________________________________

(подпись, дата, инициалы, фамилия)

Нормоконтролер ____________________________________________

(подпись, дата, инициалы, фамилия)

Работа защищена ______________ Оценка _____________

Воронеж 2014

1 Задание на практическую работу

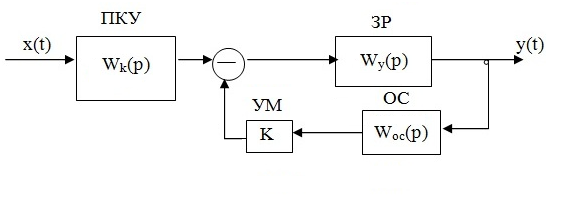

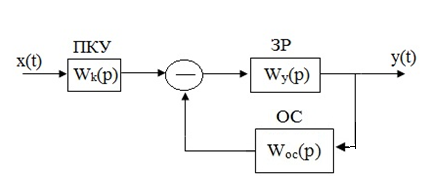

Рисунок 1 – Аналоговая САР,

где ПКУ – последовательное корректирующее устройство; ЗР – звено регулирования (регулятор); ОС – звено обратной связи в цепи коррекции; УМ – умножитель (линейный усилитель) с коэффициентом передачи К.

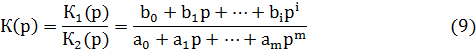

где p – операторная переменная (обозначает действие) – вычисление производно первого порядка.

Для выполнения практической работы необходимо осуществить следующие пункты:

- получить передаточную функцию непрерывной (аналоговой) системы для варианта 24;

- получить передаточную функцию для дискретной системы;

- построить схему микропроцессорной организации управления;

- разработать алгоритм управления и программу на языке ассемблер.

2 Формирование исходных данных

Индивидуальное задание студенту определяется в соответствии с двумя последними цифрами номера зачетной книжки студента (вариант 24). В таблице в ячейках на пересечении старших и младших последних двух разрядов зачетной книжки приведены цифры (для моего варианта 2,1,1), которые обозначают следующие параметры задания:

- первая цифра 2 – вид закона регулирования - пропорционально-дифференциальный с воздействием по 1-ой производной. Выражение в операторной форме для данного закона имеет вид:

где – преобразование Лапласа выходной величины;

– преобразование Лапласа входной величины.

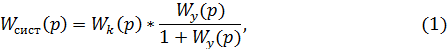

- вторая цифра 1 - тип корректирующего RC-фильтра, электрическая схема которого изображена на рисунке 2. Передаточная функция фильтра для рассчитываемого варианта равна

/(

Рисунок 2 – Электрическая схема RC-фильтра

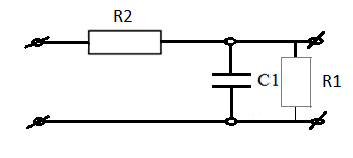

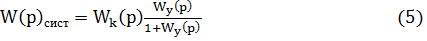

- третья цифра 1 – способ подключения корректирующего звена: 1 – последовательное корректирующее устройство (ПКУ), 2 – звено обратной связи (ОС). Для варианта 2 получим схему (рисунок 3), передаточная функция которой равна

Рисунок 3 – Структурная схема для рассчитываемого варианта

3 Передаточная функция для дискретной системы

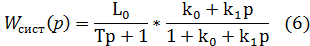

Передаточная функция аналогового прототипа проектируемой дискретной линейной системы (ДЛС) получается подстановкой в (1) выражений (2-5), определяющих передаточные функции отдельных звеньев

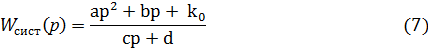

Путем замены переменных выражение 6 может быть представлено в виде

где a =

b = ;

c =;

d = .

Выражение (7) является исходным для последующего синтеза ДЛС.

4 Выбор метода синтеза ДЛС

4.1 Синтез по заданной импульсной реакции

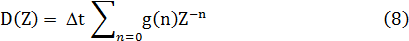

Синтез ДЛС должен осуществляться посредством построения системы, эквивалентной в некотором смысле непрерывной линейной системе с заданной передаточной функцией. Поскольку структурная схема дискретной обработки сигнала предполагает дискретизацию исходного аналогового сигнала, то естественным вариантом дискретного аналога исходной непрерывной системы является такой, когда дискретные значения импульсной весовой функции ДЛС совпадают с соответствующими дискретными выборками импульсной реакции исходного аналогового прототипа. Такой метод называется синтезом по заданной импульсной реакции. Результатом применения этого метода является Z-передаточная функция ДЛС:

где g(n) = g(n t) с точностью до t совпадает с отсчетами g(t) импульсной реакции непрерывной системы.

На практике непрерывная система чаще всего задается передаточной функцией К(р). Поскольку К(р) и g(t) взаимно однозначно связаны преобразованием Лапласа, то очевидно, что D(Z) может быть определена и по известной функции К(р). Для этого передаточную функцию К(р) следует представить в виде

Разложив на простые дроби и применит разложение Лапласа, получим, что передаточная функция равна

В общем случае, когда К(р) имеет различные полюса pi, i=1,2,...,s каждый кратности ri , вычисление D(Z) становится более громоздким. Данный метод точный, но сложно ищутся коэффициенты.

4.2 Синтез по заданной амплитудно-частотной характеристике

Пусть известна передаточная функция W(р) аналогового прототипа системы. Если необходимо перейти к Z - передаточной функции ДЛС так, чтобы АЧХ ДЛС была близка к АЧХ прототипа, то можно воспользоваться связью между переменными Р и Z, которая имеет вид

Откуда

Однако воспользоваться (12) для получения D(Z) затруднительно, так как простая подстановка (12) в W(р) приведет к иррациональной функции D(Z) , которая не может быть реализована в линейных дискретных системах. Для того, чтобы получить возможность непосредственного перехода от W(р) к D(Z) следует аппроксимировать функцию (12) рациональной функцией, воспользовавшись разложением в ряд Тейлора

Если ограничиться в (13) одним первым слагаемым, то получится преобразование

которое называется билинейным и широко используется в практике синтеза ДЛС. Получили, что метод менее точен, но легче в расчете.

Для дальнейшего расчета воспользуемся методом синтез по заданной амплитудно-частотной характеристике.

5 Определение Z-передаточной функции и синтез функциональной схемы ДЛС

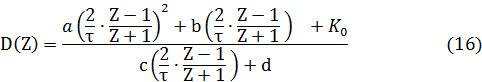

Воспользуемся методом билинейного преобразования. Для этого в (7) заменим

где - период дискретизации.

В результате получим

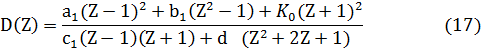

Умножая числитель и знаменатель в (16) на (Z+1)2, получим

где ;

;

;

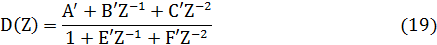

Далее, пользуясь формулой бинома Ньютона, раскрываем скобки в числителе и знаменателе (17), приводим подобные члены и приходим к выражению

где обозначено.

Разделив числитель и знаменатель в (20) на AZ2 , окончательно получим

где

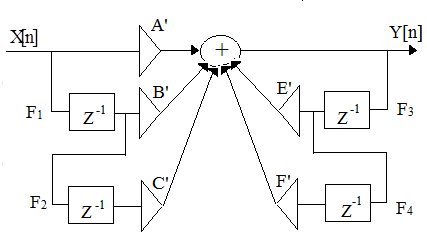

Выражение D(Z) в форме (19) является основой для последующего синтеза ДЛС. Функциональная схема ДЛС, имеющей Z-передаточную функцию (19), приведена на рисунке 4.

Рисунок 4 - Функциональная схема ДЛС

6 Синтез алгоритма микропроцессорной реализации дискретной САР

Как видно из функциональной схемы ДЛС (рисунок 4), рекурсивная процедура формирования текущего значения выходного управляющего воздействия включает в себя ограниченный набор действий:

- задержка на время, равное интервалу дискретизации ;

- умножение на константу;

- суммирование.

Считаем, что гипотетический процессор (МП) может выполнять требуемые операции умножения и суммирования с необходимой разрядностью операндов.

Кроме того, предполагается, что в составе МП имеется таймер, обладающий возможностью реализации прерывания по вектору.

Будем полагать, что таймер настраивается (программируется) на интервал дискретизации , а подпрограмма обслуживания прерывания содержит все операторы, реализующие последовательный алгоритм, адекватный «жесткой» логике функциональной схемы. Задержка на интервал осуществляется путем временного хранения в ячейке памяти (регистре) предыдущего значения дискретного отсчета. Задержки на интервалы, кратные , (т.е., 2, 3 и др.) обеспечиваются путем последовательных пересылок (продвижения) предыдущих выборок в специально выделенные для этих целей ячейки.

С учетом высказанных соображений, распределение требуемых ячеек оперативной памяти (или регистров общего назначения РОНов) может быть таким, как это представлено в таблице 2.

На рисунке 5 показана схема алгоритма, реализующего ДЛС с Z-передаточной функцией (19).

Таблица 2 – Распределение ячеек памяти (РОНов)

|

Обозначение

ячейки

|

Назначение

|

|

F0

|

Текущее (очередное) значение отсчета

|

|

F1, F2

|

Ячейки для временного хранения предыдущих значений отсчетов входного сигнала с целью обеспечения задержек на величины t, 2t, (функции Z-1, Z-2).

|

|

F3, F4

|

Ячейки для временного хранения предыдущих дискретных значений выходного сигнала с целью обеспечения задержек на величины t, 2t, (функции Z-1, Z-2для ветвей суммирования выходного сигнала)

|

|

F5

|

Ячейка для временного хранения результата текущего цикла (вывод y[n])

|

|

F6

|

Ячейка для временного хранения произведения

|

|

F7

|

Ячейка-аккумулятор для накопления суммы

|

Нет

Да

Рисунок 5 – Схема алгоритма, реализующего ДЛС с Z-передаточной функцией

Код программы на языке ассемблер 8086:

Int:

clr F0; обнуление F0

clr F1;

clr F2;

clr F3;

clr F4;

clr F5;

Timer:

sub dt,tpr; вычитание t-tпр и результат сохраняется в t

mov T,dt; пересылает t в T

brne Timerloop; оператор условия для Timer

clr F7;

Start:

in F7,F0; считывание значения входного сигнала

mulF0,A';

mov F6,F0; пересылка в F6

add F7,F6; сложение и сохранение в F7

mulF1,B';

mov F6,F1;

add F7,F6;

mulF2,C';

mov F6,F2;

add F7,F6;

mulF3,E';

mov F6,F3;

add F7,F6;

mulF4,F';

mov F6,F4;

add F7,F6;

out F7,F5; вывод выходного сигнала, пересылает F7 в F5

mov F1,F2; пересылка из F1 в F2

mov F0,F1;

mov F7,F8;

mov F6,F7;

mov F5,F6;

mov F11,F5;

jmp Timer; возврат к метке Timer

Синтез цифровой САР на основе аналогового прототипа