Адресный пороговый извещатель

ВВЕДЕНИЕ

Курсовой проект представляет собой самостоятельную работу, которая выполняется для углубления и закрепления теоретических знаний по применению наиболее распространенных цифровых элементов и узлов; приобретения навыков работы с цифровыми интегральными схемами и устройствами, построенными на их основе; развития навыков инженерной деятельности.

Объектом проектирования является адресный пороговый извещатель, функционирующий согласно заданным техническим условиям и обеспечивающий прием информации в цифровом виде, обработку принятой информации в соответствии с заданными требованиями, выдачу результата.

Проектируемое устройство содержит в своем составе блоки ввода, вывода, операционный и индикации.

1 ВНЕШНИЙ ВИД УСТРОЙСТВА И ОПИСАНИЕ ПОСЛЕДОВАТЕЛЬНОСТИ ЕГО РАБОТЫ

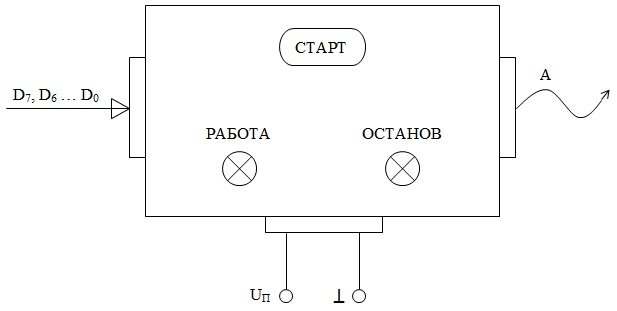

Согласно заданию по курсовому проекту был разработан адресный пороговый извещатель, внешний вид устройства смотрите на рисунке 1.

Измеряемый сигнал является цифровым, с разрядностью данных – 8, и вводится последовательно с младшего разряда.

Вывод информации, при превышении порога, осуществляется аналоговым сигналом, передается адрес датчика.

На лицевой панели устройства расположены:

- кнопка «СТАРТ»;

- индикатор «РАБОТА»;

- индикатор «ОСТАНОВ».

На левой боковой панели устройства расположен разъём для подключения шины 3С.

На правой боковой панели устройства расположен разъём для вывода аналогового сигнала.

Кроме этого устройство имеет выводы питания: общий (земля) и напряжения питания (UП).

Рисунок 1 – Внешний вид устройства

Алгоритм работы устройства приведен на рисунке 2. Запуск устройства осуществляется кнопкой «СТАРТ».

Происходит гашение индикатора «ОСТАНОВ», для этого вырабатывается команда «ГАШЕНИЕ “ОСТАНОВ”».

Происходит включение индикатора «РАБОТА», для этого вырабатывается команда «ВКЛЮЧЕНИЕ РАБОТА».

Загорается индикатор «РАБОТА».

Сохраняется адрес, который храниться в извещателе, для этого вырабатывается команда «СОХРАН. A».

Сохраняется порог, который также храниться в извещателе, для этого вырабатывается команда «СОХРАН. P».

Ввод данных будет осуществлен путём подключения к шине ввода, для этого вырабатывается команда «ПОДКЛ. К ШВв». Затем осуществляется последовательный ввод данных путем выработки команд «ВВОД D0» … «ВВОД D7». В результате чего восьмиразрядный двоичный измеряемый сигнал с ШВв (шина ввода) поступает в устройство.

Введенная информация сохраняется, для чего вырабатывается команда «СОХРАН. D».

Происходит отключение от шины ввода данных (ШВв), путем вырабатывания команды «ОТКЛ. ОТ ШВв».

Далее следует операция сравнения измеряемого сигнала с порогом, который храниться в извещателе. При данной операции сравнения возможны следующие два варианта:

- Если введенный измеряемый сигнал оказывается больше порога, то следует преобразование адреса из цифрового в аналоговый сигнал, посредством цифро-аналогового преобразователя, для этого вырабатывается команда «ПРЕОБРАЗ. A». Далее следует передача аналогового сигнала, путем осуществления команды «РАЗРЕШ. ВЫВОД». После этого действия алгоритма повторяются с команды «ПОДКЛ. К ШВв», и далее сравнивается следующий вводимый измеряемый сигнал.

Рисунок 2 – Алгоритм работы устройства

-

Если введенный измеряемый сигнал оказывается меньше либо равным порогу, то действия алгоритма повторяются с команды «ПОДКЛ. К ШВв», и далее сравнивается следующий вводимый измеряемый сигнал.

2 ФУНКЦИОНАЛЬНАЯ СХЕМА УСТРОЙСТВА

Схема электрическая функциональная БНТУ113010.036 Э2 адресного порогового извещателя приведена в приложении 1.

Ввод измеряемого сигнала осуществляется блоком ввода (БВв). Сравнение измеряемого сигнала с пороговым значением осуществляется в операционном блоке (ОБ). Управление устройством осуществляется блоком управления (БУ). Все индикаторы находятся в блоке индикации (БИ).

Функциональный состав блоков в соответствии с алгоритмом работы устройства:

1. Блок ввода (БВв). Обеспечивает подключение к внешней шине последовательного ввода данных на момент получения измеряемого сигнала D; отключение от шины последовательного ввода данных; хранение измеряемого цифрового сигнала D, передачу D в операционный блок.

В функциональный состав БВв входит модуль, обеспечивающий подключение/отключение от шины последовательного ввода данных D (ZВв), модуль хранения введенного цифрового сигнала D (МХрD).

2. Операционный блок (ОБ). Обеспечивает сравнение введенного цифрового сигнала D с пороговым значением P. На основе этого сравнения могут формироваться два признака, которые передаются в блок управления: D>P; D<=P.

В функциональный состав ОБ входит модуль сравнения (МСрDиP), модуль хранения порогового значения P (МХрP), модуль формирования признака того что сигнал D больше порога P (МФПрD>P), модуль формирования признака того что сигнал D меньше либо равен порогу P (МФПрD<=P).

3. Блок вывода (БВыв). Обеспечивает хранение адреса извещателя A; преобразование данного адреса в аналоговый сигнал; вывод аналогового сигнала.

В функциональный состав БВыв входит модуль хранения адреса извещателя (МХрA), модуль цифроаналогового преобразования (МПрЦА).

4. Блок индикации (БИ). Имеет два индикатора, которые загораются при соответствующих сигналах, вырабатываемых устройством. Индикатор «ОСТАНОВ» горит при неработающем состоянии устройства. Индикатор «РАБОТА» загорается при включении устройства и горит на протяжении его работы.

5. Блок управления (БУ). Обеспечивает прием признаков D<=P и D>P от операционного блока, формирование управляющих сигналов, в том числе с учетом признаков D<=P и D>P передачу управляющих сигналов в последовательности, обеспечивающей алгоритм работы устройства, на соответствующие блоки. С признаком D<=P или D>P формируются команды «ПОДКЛ. К ШВв»; «ВВОД D0», «ВВОД D1» … «ВВОД D7»; «СОХРАН. D»; «ОТКЛ. ОТ ШВв»; «СРАВНЕНИЕ D и P». Также с признаком D>P формируются команды «ПРЕОБРАЗ. A» и «РАЗРЕШ. ВЫВОД». Без учета признаков формируются команды «ГАШЕНИЕ “ОСТАНОВ”»; «ВКЛЮЧЕНИЕ “РАБОТА”»; «СОХРАН. A» и «СОХРАН. P». Работа блока управления обеспечивается некоторой последовательностью тактовых импульсов, передаваемых генератором тактовых импульсов (ГТИ).

Предусмотрена кнопка «СТАРТ», обеспечивающий начало работы устройства. Также для работы устройства необходим блок питания (БП).

3 ВЫБОР ЭЛЕМЕНТНОЙ БАЗЫ

В зависимости от внешней среды эксплуатации выпускаются семейства интегральных схем для применения в военной промышленности, автомобильной промышленности, общего назначения. В нашем случае, для проектирования адресного порогового извещателя выбираем семейства общего назначения.

Важным критерием выбора элементной базы для адресного порогового извещателя является быстродействие и малое энергопотребление. В соответствии с этим условием выбираем стандартную технологию ТТЛ, учитывая доступность элементной базы и достаточное быстродействие. Напряжение питания у них Uип = 5В ± 10%. Отличаются полной электрической и конструктивной совместимостью однотипных ИС.

3.1 Общие сведения о ТТЛ. Основы схемотехники элементов ТТЛ

Конструктивно-технологическая реализация цифровых интегральных схем во многом определяет их основные технические параметры – быстродействие, потребляемую мощность, устойчивость к внешним дестабилизирующим фактором[1, с. 23-25].

Существуют следующие разновидности ИС ТТЛ:

- три ранние разновидности микросхем без применения p - n - переходов с барьером Шотки (стандартные или среднего быстродействия - С ТТЛ; маломощные - Мм ТТЛ; мощные - МТТЛ);

- две со структурами Шотки - ТТЛШ;

- три новые, перспективные, усовершенствованные ТТЛШ.

В настоящее время в аппаратуре можно встретить все перечисленные варианты микросхем ТТЛ. Напряжение питания у них одинаковое Uип = 5 В± 10%, а входные и выходные логические уровни совместимы. Микросхемы ТТЛШ имеют улучшенные электрические параметры, расположение выводов на корпусе остается прежним. Полная электрическая и конструктивная совместимость однотипных ИС из разных серий снимает многие проблемы развития и улучшения параметров аппаратуры и стимулирует наращивание степени внутренней интеграции вновь выпускаемых микросхем, когда на одном кристалле размещается все большее число функциональных узлов. Основная часть применяемых сейчас микросхем ТТЛ имеет средний уровень интеграции.

Быстродействие микросхем принято сравнивать по времени задержки распространения сигнала t зд.р, т.е. по интервалу времени от подачи входного импульса до появления выходного. Основная часть экономии энергии, затрачиваемой в элементе ТТЛ, получена за счет уменьшения времени t зд.р, т.е. увеличения быстродействия.

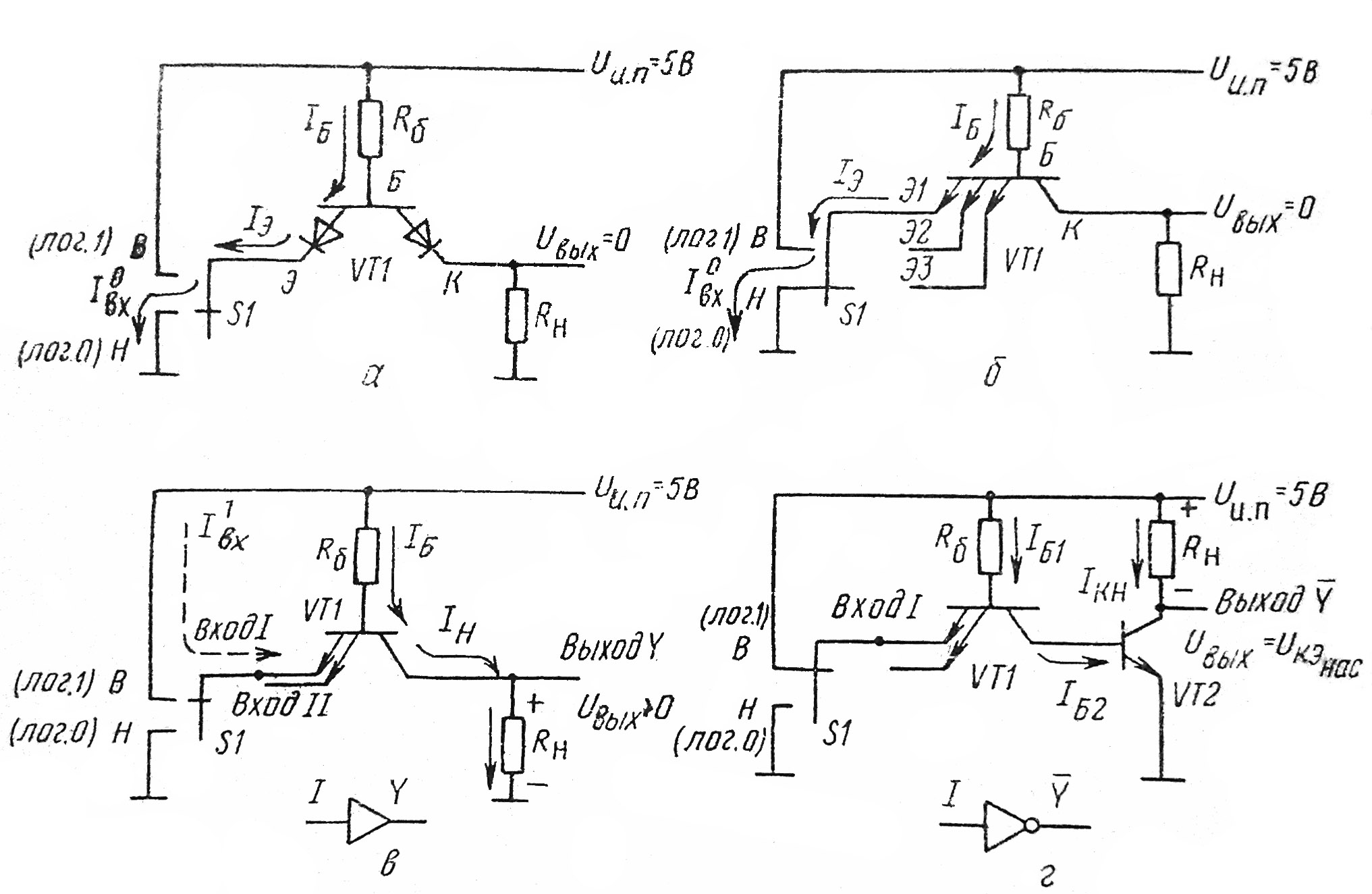

Основную логическую операцию в элементе ТТЛ выполняет многоэмиттерный транзистор (рисунок 3). Для удобства рассмотрения переключения логического элемента к входу подключим управляющий переключатель S1, движок которого может занимать два положения - В и Н, а к выходу подключим резистор Rн. В положении В на вход поступит напряжение высокого уровня, т.е. питающее напряжение Uн.п., а в положении Н - напряжение низкого уровня, соответствующее нулю (вход заземляем). Если на вход (рисунок 3.а) подано низкое напряжение (переключатель S1 поставлен в положение Н) , то появится входной ток низкого уровня I0вх, который будет протекать от источника питания Uип = 5 В через резистор RБ, переход база-эмиттер многоэмиттерного транзистора VТ1, контакт Н переключателя S1 на корпус. Величина этого тока определяется сопротивлением резистора RБ:

I0вх = IБ (Uип – UБЭ) / RБ.

В быстродействующих и экономичных ИС ТТЛ сопротивления резисторов RБ отличаются примерно на порядок. Переход база-коллектор транзистора VТ1 открыться не может, так как на нем нет избыточного напряжения более чем 0,7 В = UБЭ. Напряжение Uвых близко к нулю. Таким образом, переход база-эмиттер транзистора VТ1 открыт, а переход база-коллектор VТ1 закрыт, т. е. многоэмиттерный транзистор VТ1 находится в активном режиме, напряжение на выходе равно нулю Uвых = 0. Если число входов транзистора VТ1 более одного (рисунок 3.б) (два из них не присоединены), то величина тока I0вх не изменится. Если все три эмиттера VТ1 соединить вместе, ток I0вх практически не изменится. Следовательно, неиспользуемые входы можно оставлять разомкнутыми. Если заземлен хотя бы один из входов транзистора VТ1 (рисунок 3.б), смена логических уровней на остальных входах не влияет на выходное напряжение Uвых.

Рисунок 3 – Простейшие логические элементы ТТЛ:

а – путь входного тока Iвх.0; б – токи в транзисторе VT1 при низком входном уровне; в – токи в транзисторе VT1 при высоком входном уровне; г – токи в простейшем инверторе при высоком входном уровне

Переведем движок переключателя S1 в положение В (рисунок 3.в) (подано на вход напряжение высокого уровня), тогда переход база-эмиттер транзистора VТ1 будет закрыт, так как напряжение между базой и эмиттером меньше или равно нулю UБЭ 0. Оба электрода (база и эмиттер) подключены к источнику питания Uип = 5 В. Большой ток базы IБ течет от источника питания Uип через резистор RБ, открытый переход база-коллектор, а затем через резистор нагрузки Rн к нулевому потенциалу (рисунок 3.в). На коллекторе VТ1 появляется напряжение высокого уровня:

U1вых Uип(Rн / (Rн + RБ))

На вход 1 поступает лишь входной ток утечки высокого уровня I1вх, не превышающий при нормальной температуре нескольких наноампер (направление тока I1вх, показано на рисунке 3.в)

Таким образом, переход база-эмиттер транзистора VT1 закрыт, а переход база-коллектор VT1 открыт, т. е. многоэмиттерный транзистор VT1 находится в инверсном активном режиме, напряжение на выходе больше нуля: Uвых > 0 (имеет высокий уровень).

Следовательно, на рисунке 3.в приведен одновходовый элемент ТТЛ, реализующий логическую операцию И и не изменяющий фазу входного сигнала. Такой элемент назовем неинвертирующим. В такой схеме активным включающим является напряжение низкого уровня и через переключатель S1 на корпус стекает большой входной ток Iвх0 (для стандартных элементов ТТЛ, серия К155, ток одного входа I0вх 1,6 мА).

Для получения инвертирующего логического элемента, реализующего логическую операцию И-НЕ, необходимо к многоэмиттерному транзистору VT1 добавить инвертор, выполненный на транзисторе VT2 (рисунок 3.г).

Если на вход I логического элемента поступает напряжение высокого уровня (переключатель S1 в положении В), то многоэмиттерный транзистор VT1 находится в инверсном активном режиме, а транзистор VT2 насыщается базовым током IБ и выходное напряжение, снимаемое с коллектора VT2, будет иметь низкий уровень, что соответствует логическому нулю U0вых (не превышает 0,3 В). Это напряжение является напряжением насыщения коллектор-эмиттер UКЭ.нас для кремниевого транзистора VT2.

Если на вход I логического элемента подать напряжение низкого уровня (переключатель S1 в положения Н), то транзистор VT2 практически закрыт, а во входной цепи течет большой ток I0вх. Выходное напряжение, снимаемое с коллектора VT2, близко к напряжению источника питания Uип, т. е. имеет высокий уровень, что соответствует логической единице U1вых.

3.2 Схемотехнические решения при выборе элементной базы

1. Блок ввода (БВв) схемы электрической функциональной БНТУ113010.036 Э2.

Блок ввода содержит дав модуля ZВв и МХрD. Модуль ZВв в режиме работы устройства должен обеспечивать подключение и отключение от шины ввода. Шина должна иметь 3 состояния. Для организации модуля ZВв ввода используется буферный элемент с тремя состояниями. Для последовательной передачи данных необходим буферный элемент с одним входом, ввиду того что такого элемента нет применяется буферный элемент на 8 двунаправленных шинных усилителей с тремя состояниями выходов. Незадействованные входы заземляются.

Модуль хранения МХрD должен обеспечивать прием последовательно вводимого восьмиразрядного сигнала D, его хранение и параллельную передачу на операционный блок (ОБ). Для обеспечения этих функций используется восьмиразрядный синхронный реверсивный регистр сдвига.

2. Операционный блок (ОБ) схемы электрической функциональной БНТУ113010.036 Э2.

В адресном пороговом извещателе осуществляется сравнение введённого измеряемого сигнала D с пороговым значением P, которое хранится в извещателе. По результатам сравнения формируется определенный признак, который передается в блок управления (БУ). Операционный блок (ОБ) содержит 4 модуля: МХрP, МСрDиP, МФПрD>P, МФПрD<=P.

Модуль хранения МХрP должен хранить восьмиразрядное пороговое значение и обеспечивать параллельную передачу этого значения на модуль сравнения МСрDиP. Для организации этих функций также используется восьмиразрядный синхронный реверсивный регистр сдвига как и в модуле МХрD. Пороговое значение задается соответствующей подачей напряжений уровней логических нулей и единиц на входы регистра.

Для осуществления функций выполняемых модулями МСрDиP, МФПрD>P, МФПрD<=P используется каскад компараторов двух четырехразрядных чисел, ввиду того что компаратора двух восьмиразрядных чисел нет. Каскад компараторов обеспечивает параллельный прием восьмиразрядных сигналов D и P, их сравнение, а также формирование признаков D>P и D<=P, в зависимости от результата сравнения и последующую передачу этих признаков в блок управления (БУ).

3. Блок вывода (БВыв) схемы электрической функциональной БНТУ113010.036 Э2.

В случае превышения порогового значения, т.е. формирования признака D>P, устройство должно обеспечить передачу своего адреса, сигнала A, предварительно преобразовав его из цифровой формы в аналоговый сигнал. Эти шаги работы устройства обеспечивают модули МХрA и МПрЦА.

Модуль хранения МХрA обеспечивает хранение восьмиразрядного значения адреса извещателя по такому же принципу как и МХрP операционного блока. МХрA построен на восьмиразрядном синхронном реверсивном регистре сдвига. Регистр также осуществляет параллельную передачу цифрового кода на модуль преобразования МПрЦА.

МПрЦА – это модуль осуществляющий цифроаналоговое преобразование и дальнейшую передачу преобразованного сигнала. Для построения данного модуля используется цифроаналоговый преобразователь (ЦАП), совместно с операционным усилителем (ОУ). Операционный усилитель позволяет получить качественный, хорошо регистрируемый аналоговый сигнал, несущий в себе информацию, содержащую адрес извещателя.

4. Блок индикации (БИ) схемы электрической функциональной БНТУ113010.036 Э2.

Блок индикации состоит из двух индикаторов «РАБОТА» и «ОСТАНОВ». Каждый из этих индикаторов несет определенное сообщение. Принцип построения индикаторов одинаков. Для реализации индикатора используется светоизлучающий диод, работа которого осуществляется под действием команд из блока управления. Обработку команд выполняет триггер и логический элемент с открытым коллектором. Для формирования нужного уровня тока протекающего через светодиод используется резистор.

3.3 Выбор интегральных микросхем (ИМС)

1. Буферный элемент. В качестве буферного элемента соответствующего схемотехническим решениям, выбираем ту ИМС, которая имеет наибольшее быстродействие – ИМС 533АП6 [1, с. 126-129]. ИМС содержит восемь двунаправленных шинных усилителей с тремя состояниями выходов. Она имеет два входа разрешения EAB (переключение направления каналов) и инверсный EO (перевод выхода канала в третье состояние - z). У данной микросхемы нет запрещенных комбинаций сигналов управления, таблица 1.

Таблица 1 – Состояния ИМС 533АП6

|

Входы

|

Выходы

|

|

EO

|

EAB

|

An

|

Bn

|

|

0

|

0

|

A=B

|

вход

|

|

0

|

1

|

вход

|

B=A

|

|

1

|

X

|

Z

|

Z

|

Цоколевка микросхемы 533АП6 и условное обозначение приведены на рисунке 4.

Рисунок 4 – УГО и цоколевка ИМС 533АП6

Вывод 10 – общий, 20 – напряжение питания +5 В.

Основные параметры приведены в таблице 2.

Таблица 2 – Основные параметры ИМС 533АП6

|

,

В

|

,

В

|

,

В

|

,

мА

|

,

мА

|

,

мА

|

,

мА

|

,

нс

|

,

нс

|

|

5

|

0,4

|

2

|

-0,2

|

0,02

|

90

|

70

|

18

|

18

|

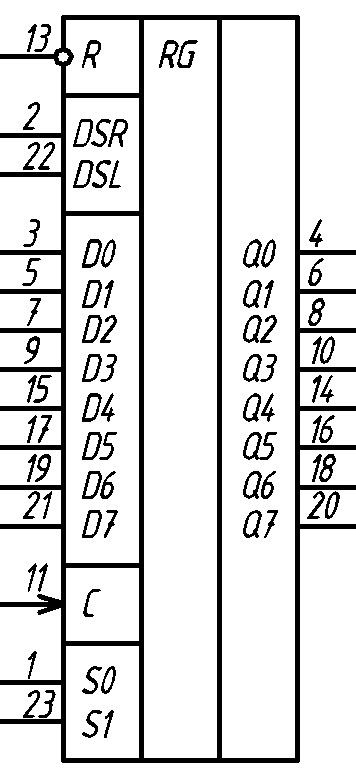

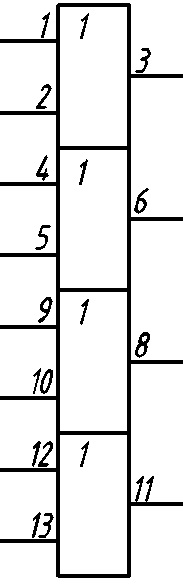

2. Регистр. В качестве соответствующего схемотехническим решениям регистра выбираем ИМС 133ИР13 [1, с. 191-192, 224]. Данная ИМС наиболее оптимально подходит, по быстродействию и потребляемой мощности, из имеющихся в справочнике. Микросхема 133ИР13 – это восьмиразрядный синхронный реверсивный регистр сдвига. Цоколевка и условное обозначение приведены на рисунке 5.

Синхронную работу регистру обеспечивают входы выбора режима S0 и S1: режим хранения (входы S0=S1=0), параллельной загрузки (входы S0=S1=1), сдвиг влево (входы S0=0, S1=1), сдвиг вправо (входы S0=1, S1=0).

Кроме параллельных входов D0…D7, первый и последний разряды регистра имеют дополнительные входы: DSR – для сдвига вправо, DSL – для сдвига влево.

Рисунок 5 – Условное обозначение и цоколевка ИМС 133ИР13

Вывод 12 – общий, 24 – напряжение питания +5 В.

На входы S0 и S1 отрицательный перепад можно подавать, когда на входе C действует напряжение высокого уровня.

При параллельной загрузке данные подготовленные на входах D0…D7, появятся на выходах Q0…Q7 после прихода очередного положительного перепада тактового импульса на вход C.

Для обнуления регистра (на выходах Q0…Q7 будет низкий уровень) необходимо на асинхронный, инверсный вход сброса R подать низкий уровень напряжения. Состояния ИМС 133ИР13 приведены в таблице 3, основные параметры в таблице 4.

Таблица 3 – Состояния ИМС 133ИР13

|

Режим

работы

|

Входы

|

Выходы

|

|

|

C

|

R

|

S0

|

S1

|

DSR

|

DSL

|

Dn

|

Q0

|

Q1…Q6

|

Q7

|

|

Сброс

|

|

0

|

X

|

X

|

X

|

X

|

X

|

0

|

0…0

|

0

|

|

Хранение

|

|

1

|

0

|

0

|

X

|

X

|

X

|

Q0

|

Q1 … Q6

|

Q7

|

|

Сдвиг

влево

|

|

1

|

1

|

0

|

X

|

0

|

X

|

Q1

|

Q2 … Q7

|

0

|

|

|

|

1

|

1

|

0

|

X

|

1

|

X

|

Q1

|

Q2 … Q7

|

1

|

|

Сдвиг

вправо

|

|

1

|

0

|

1

|

0

|

X

|

X

|

0

|

Q0 … Q5

|

Q6

|

|

|

|

1

|

0

|

1

|

1

|

X

|

X

|

1

|

Q0 … Q5

|

Q6

|

|

Параллельная

загрузка

|

|

1

|

1

|

1

|

1

|

X

|

dn

|

d0

|

d1 … d6

|

Q7

|

Таблица 4 – Основные параметры ИМС 133ИР13

|

,

В

|

,

В

|

,

В

|

,

мА

|

,

мА

|

,

мА

|

,

мА

|

,

нс

|

,

нс

|

|

5

|

0,4

|

2,4

|

-1,6

|

0,04

|

104

|

30

|

26

|

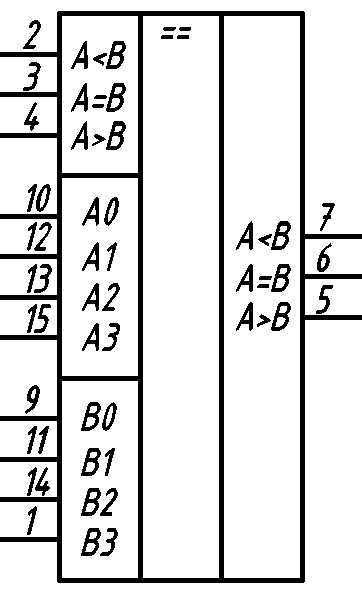

3. Компаратор. В качестве соответствующего схемотехническим решениям компаратора выбираем ИМС 533СП1 [1, с. 268, 272-273, 279]. Данная ИМС наиболее оптимально подходит по быстродействию и потребляемой мощности из имеющихся в используемом справочнике.

ИМС 533СП1 – это схема сравнения (компаратор) двух четырехразрядных чисел. Она имеет 11 входов: четыре пары (восемь входов) из них принимают два четырехразрядных числа A0…A3 и B0…B3, а три входа A<B, A=B, A>B необходимы для увеличения емкости схемы (соединения нескольких ИМС типа 533СП1). Компаратор имеет три выхода: A>B, A=B, A<B. Цоколевка и условное обозначение ИМС 533СП1 приведены на рисунке 6, основные параметры в таблице 5, состояния работы в таблице 6.

Рисунок 6 – Условное обозначение и цоколевка ИМС 533СП1

Вывод 8 – общий, 16 – напряжение питания +5 В.

Таблица 5 – Основные параметры ИМС 533СП1

|

,

В

|

,

В

|

,

В

|

,

мА

|

,

мА

|

,

мА

|

,

мА

|

,

нс

|

,

нс

|

|

5

|

0,4

|

2,4

|

-0,4

|

0,06

|

20

|

30

|

20

|

Таблица 6 – Состояния работы ИМС 533СП1

|

Входы сравнения данных

|

Входы

наращивания

каскадов

|

Выходы

|

|

A3,B3

|

A2,B2

|

A1,B1

|

A0,B0

|

A>B

|

A<B

|

A=B

|

A>B

|

A<B

|

A=B

|

|

A3>B3

|

X

|

X

|

X

|

X

|

X

|

X

|

1

|

0

|

0

|

|

A3<B3

|

X

|

X

|

X

|

X

|

X

|

X

|

0

|

1

|

0

|

|

A3=B3

|

A2>B2

|

X

|

X

|

X

|

X

|

X

|

1

|

0

|

0

|

|

A3=B3

|

A2<B2

|

X

|

X

|

X

|

X

|

X

|

0

|

1

|

0

|

|

A3=B3

|

A2=B2

|

A1>B1

|

X

|

X

|

X

|

X

|

1

|

0

|

0

|

|

A3=B3

|

A2=B2

|

A1<B1

|

X

|

X

|

X

|

X

|

0

|

1

|

0

|

|

A3=B3

|

A2=B2

|

A1=B1

|

A0>B0

|

X

|

X

|

X

|

1

|

0

|

0

|

|

A3=B3

|

A2=B2

|

A1=B1

|

A0<B0

|

X

|

X

|

X

|

0

|

1

|

0

|

|

A3=B3

|

A2=B2

|

A1=B1

|

A0=B0

|

1

|

0

|

0

|

1

|

0

|

0

|

|

A3=B3

|

A2=B2

|

A1=B1

|

A0=B0

|

0

|

1

|

0

|

0

|

1

|

0

|

|

A3=B3

|

A2=B2

|

A1=B1

|

A0=B0

|

0

|

0

|

1

|

0

|

0

|

1

|

|

A3=B3

|

A2=B2

|

A1=B1

|

A0=B0

|

X

|

X

|

1

|

0

|

0

|

1

|

|

A3=B3

|

A2=B2

|

A1=B1

|

A0=B0

|

1

|

1

|

0

|

0

|

0

|

0

|

|

A3=B3

|

A2=B2

|

A1=B1

|

A0=B0

|

0

|

0

|

0

|

1

|

1

|

0

|

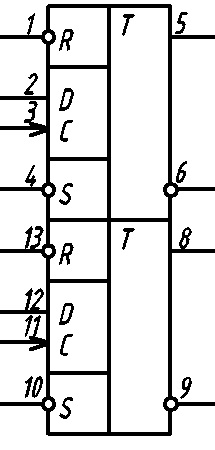

4. Триггер. В качестве триггера используем ИМС 533ТМ2 [1, с. 98, 107-109]. Данная ИМС имеет относительно малую потребляемую мощность и средние параметры быстродействия из имеющихся в используемом справочнике.

ИМС 533ТМ2 содержит два независимых комбинированных D-триггера, имеющих общую цепь питания. У каждого триггера имеется один информационный вход D, вход синхронизации С и два дополнительных инверсных входа S и R независимой асинхронной установки триггера в единичное и нулевое состояния, а также комплементарные выходы Q и инверсный Q, рисунок 7.

Рисунок 7 – Условное обозначение и цоколевка ИМС 533ТМ2

Вывод 7 – общий, 14 – напряжение питания +5 В.

Асинхронная установка D-триггера в единичное или нулевое состояния осуществляется подачей взаимопротивоположных логических сигналов на инверсные входы S и R. В это время входы D и С не влияют на работу.

Если на инверсные входы S и R одновременно подать сигнал низкого уровня (логический нуль), то на обоих выходах триггера Q и Q будет высокий уровень (логическая единица). Однако после снятия этих сигналов с инверсных входов S и R состояние триггера будет неопределенным. Поэтому комбинация S = R = 0 для этих инверсных входов является запрещенной.

Загрузить в триггер логические 1 или 0 можно, если на инверсные входы S и R подать напряжение высокого, т.е. неактивного уровня: S = R = 1. Сигнал от входа D передается на выходы триггера при поступлении положительного перепада импульса на вход С (изменение от низкого к высокому). Однако, чтобы D-триггер переключался правильно (согласно таблице состояний, таблица 7), необходимо уровень на входе D зафиксировать заранее, т. е. до прихода перепада на вход С. Причем этот защитный временной интервал должен быть больше времени задержки распространения сигнала в триггере.

Основные параметры ИМС 533ТМ2 приведены в таблице 8.

Таблица 7 – Состояния ИМС 533ТМ2

|

Режим работы

|

Входы

|

Выходы

|

|

|

S

|

R

|

D

|

C

|

Q(прям.)

|

Q(инв.)

|

|

Асинхронная установка

|

0

|

1

|

X

|

X

|

1

|

0

|

|

Асинхронный сброс

|

1

|

0

|

X

|

X

|

0

|

1

|

|

Неопределенность

|

0

|

0

|

X

|

X

|

1

|

1

|

|

Загрузка “1” (установка)

|

1

|

1

|

1

|

|

1

|

0

|

|

Загрузка “0” (сброс)

|

1

|

1

|

0

|

|

0

|

1

|

Таблица 8 – Основные параметры ИМС 533ТМ2

|

,

В

|

,

В

|

,

В

|

,

мА

|

,

мА

|

,

мА

|

,

мА

|

,

нс

|

,

нс

|

|

5

|

0,4

|

2,5

|

-0,4

|

0,06

|

8

|

40

|

25

|

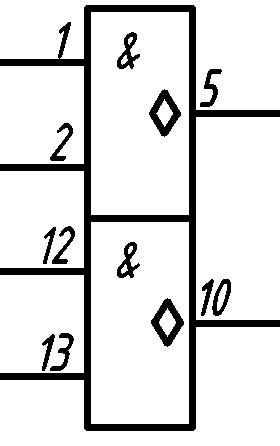

5. Логический элемент (ЛЭ) 2-И с открытым коллектором. Для реализации блока индикации необходимо 2 ЛЭ с открытым коллектором, этим требованиям отвечает ИМС 155ЛИ5, имеющая наилучшее быстродействие [1, с. 47, 56].

Цоколевка и условное обозначение ИМС 155ЛИ5 изображены на рисунке 8. Состояния ИМС 155ЛИ5 приведены в таблице 9, а основные параметры в таблице 10.

Рисунок 8 – Условное обозначение и цоколевка ИМС 155ЛИ5

Вывод 7 – общий, 14 – напряжение питания +5 В.

Таблица 9 – Состояния ИМС 155ЛИ5

|

Входы

|

Выходы

|

|

1,12

|

2,13

|

5,10

|

|

0

|

0

|

0

|

|

0

|

1

|

0

|

|

1

|

0

|

0

|

|

1

|

1

|

1

|

Входы 3, 4, 6, 8, 9, 11 в ИМС 155ЛИ5 являются свободными, 7 – вход общий, 14 – напряжение питания.

Таблица 10 – Основные параметры ИМС 155ЛИ5

|

,

В

|

,

В

|

,

В

|

,

мА

|

,

мА

|

,

мА

|

,

мА

|

,

нс

|

,

нс

|

|

5

|

0,2

|

2,4

|

-1,6

|

0,04

|

65

|

11

|

25

|

25

|

6. ЛЭ 2-ИЛИ. Имеются микросхемы типа ЛЛ1 и ЛЛ2 содержащие по 4 и 2 соответственно логических элемента 2-ИЛИ. Из имеющихся в справочнике ИМС данного типа по критериям быстродействия и потребляемой мощности лучше всего выбрать ИМС КР1531ЛЛ1 [1, с. 62, 64]. Данная ИМС имеет высокое быстродействие и малую потребляемую мощность. Потребляемая мощность корпуса ИМС КР1531ЛЛ1, состоящая из 4 ЛЭ 2-ИЛИ, меньше потребляемой мощности корпусов микросхем типа ЛЛ2, состоящих из 2 ЛЭ 2-ИЛИ. В схеме требуется один ЛЭ 2-ИЛИ.

Цоколевка и условное обозначение ИМС КР1531ЛЛ1 изображены на рисунке 9. Состояния ИМС КР1531ЛЛ1 приведены в таблице 11, а основные параметры в таблице 12.

Рисунок 9 – Условное обозначение и цоколевка ИМС КР1531ЛЛ1

Вывод 7 – общий, 14 – напряжение питания +5 В.

Таблица 11 – Состояния ИМС КР1531ЛЛ1

|

Входы

|

Выходы

|

|

1,4,9,12

|

2,5,10,13

|

3,6,8,11

|

|

0

|

0

|

0

|

|

0

|

1

|

1

|

|

1

|

0

|

1

|

|

1

|

1

|

1

|

Таблица 12 – Основные параметры ИМС КР1531ЛЛ1

|

,

В

|

,

В

|

,

В

|

,

мА

|

,

мА

|

,

мА

|

,

мА

|

,

нс

|

,

нс

|

|

5

|

0,5

|

2,7

|

-0,6

|

0,02

|

15,5

|

8,3

|

5

|

5,5

|

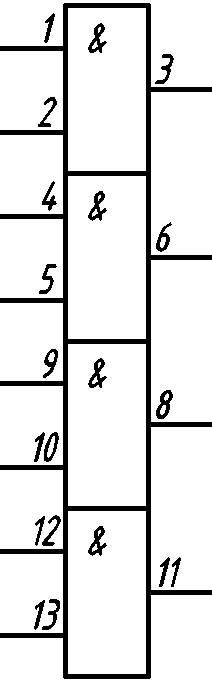

7. ЛЭ 2-И. Имеется микросхема типа ЛИ1 содержащая 4 логических элемента 2-И. Из имеющихся в справочнике ИМС данного типа по критериям быстродействия и потребляемой мощности лучше всего подходит ИМС КР1531ЛИ1 [1, с. 47, 55]. Данная ИМС имеет высокое быстродействие и малую потребляемую мощность.

Цоколевка и условное обозначение ИМС КР1531ЛИ1 изображены на рисунке 10. Состояния ИМС КР1531ЛИ1 находятся в таблице 13, а основные параметры в таблице 14.

Рисунок 10 – Условное обозначение и цоколевка ИМС КР1531ЛИ1

Вывод 7 – общий, 14 – напряжение питания +5 В.

Таблица 13 – Состояния ИМС КР1531ЛИ1

|

Входы

|

Выходы

|

|

1,4,9,12

|

2,5,10,13

|

3,6,8,11

|

|

0

|

0

|

0

|

|

0

|

1

|

0

|

|

1

|

0

|

0

|

|

1

|

1

|

1

|

Таблица 14 – Основные параметры ИМС КР1531ЛИ1

|

,

В

|

,

В

|

,

В

|

,

мА

|

,

мА

|

,

мА

|

,

мА

|

,

нс

|

,

нс

|

|

5

|

0,5

|

2,7

|

-0,6

|

0,02

|

12,9

|

8,3

|

5,0

|

5,5

|

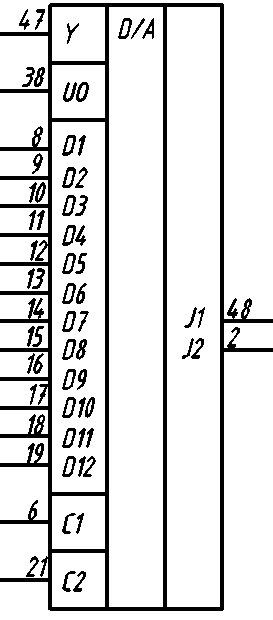

8. Цифроаналоговый преобразователь (ЦАП). В качестве ЦАП выбираем ИМС 572ПА2 [2, с. 79-82; 3]. Данная ИМС предназначена для преобразования двенадцатиразрядного прямого двоичного кода на цифровых входах в ток на аналоговом выходе, который пропорционален значениям входного кода и (или) опорного напряжения. Условное обозначение и цоколевка ИМС 572ПА2 приведены на рисунке 11, основные параметры в таблице 15.

Рисунок 11 – Условное обозначение и цоколевка ИМС 572ПА2

Выводы 4 и 22 аналоговая и цифровая земля соответственно, 20 и 24 напряжение питания UCC1 и UCC2 соответственно, 30 – вывод конечного резистора матрицы, неуказанные выводы не используются.

Таблица 15 – Основные параметры ИМС 572ПА2

|

UCC1,

В

|

UCC2,

В

|

UОП,

В

|

Iпот,

мА

|

Время установления

выходного тока,

мкс

|

|

5

|

15

|

10,24

|

2

|

10

|

Для работы с выходом по напряжению ЦАП 572ПА 2 требуется источник опорного напряжения и операционный усилитель в режиме суммирования токов.

Метод преобразования в ИМС 572ПА2 предполагает суммирование всех разрядных токов, взвешенных по двоичному закону и пропорциональных значению опорного напряжения на входе в соответствии с заданным значением двоичного кода на цифровых входах ЦАП.

Преобразователь рассчитан на работу от двух источников питания UCC1 = 5В ± 5% и UCC2 = 15В ± 5% при опорном напряжении UОП = 10,24В ± 20мВ. Наличие отдельного вывода для питания входных усилителей-инверторов от источника 5В ± 5% позволяет подключить его к ТТЛ схемам без дополнительных резисторов. Точность преобразования при этом не ухудшается.

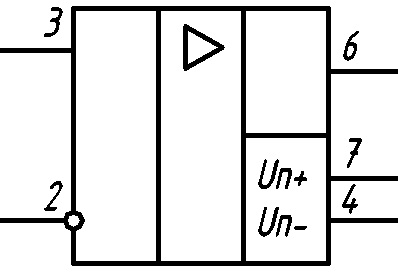

9. Операционный усилитель (ОУ). Для сохранения точности ЦАП следует использовать ИМС ОУ с напряжением смещения до 5 мВ. Выберем ОУ ИМС К153УД3, обладающая напряжением смещения нуля 2 мВ. Данная ИМС относится к группе общего применения, ОУ которой универсальны и имеют средние значения параметров. Условное обозначение и цоколевка приведены на рисунке 12, а основные параметры ИМС 153УД3 в таблице16 [4].

Рисунок 12 – Условное обозначение и цоколевка ИМС 153УД3

Выводы 1, 5, 8 – используются для коррекции, в нашем случае они остаются свободными.

Таблица 16 – Основные параметры ИМС 153УД3

|

Uпит.,

В

|

Iпот, мА

|

Uсм, мВ

|

Iвх, нА

|

Uдф max, В

|

Uсф max, В

|

Kсф, дБ

|

f1, МГц

|

VU, В/мкс

|

|

15

|

4

|

2

|

200

|

5

|

8

|

80

|

1

|

0,2

|

10. Светоизлучающие диоды. При выборе светодиодов необходимо учесть выходное напряжение уровня единицы элемента, оно должно быть меньше максимально-допустимого обратного напряжения светодиода. Т.к. у элементов ТТЛ выходное напряжение уровня единицы обычно не превышает 3 В, то максимально-допустимое обратное напряжение светодиода должно быть больше либо равным 3 В. Также нужно предусмотреть чтобы прямое падение напряжения на светодиоде, при номинальном прямом токе, не превышало напряжение питания UП = 5 В. Для реализации сообщения “ОСТАНОВ” на блоке индикации будем использовать светодиод красного цвета свечения КИПМ02А-1К, а для реализации сообщения “РАБОТА” светодиод желто-зеленого цвета свечения КИПМ03В-1Л. Основные параметры данных диодов приведены в таблице 17 [5].

Таблица 17 – Основные параметры светодиодов АЛ307БМ и АЛ341Г

|

Тип

прибора

|

Цвет

свечения

|

Значения параметров при Т=25°С,

Iпр ном, мА

|

Iпр max,

мА

|

Uобр max,

В

|

|

|

|

Iv, мккд

(L), кд/м2

|

Uпр,

B

|

Iпр ном,

мА

|

lmax,

мкм

|

|

|

|

КИПМ02А-1К

|

красный

|

400

|

2

|

10

|

0,65...0,675

|

30

|

5,0

|

|

КИПМ03В-1Л

|

желт.-зел.

|

400

|

2,8

|

20

|

0,55...0,57

|

30

|

5,0

|

11. Резисторы. Резисторы используются для формирования токов протекающих через светодиоды, а также формирования токов уровня логической единицы. Выберем резисторы С2-36 [6].

Резисторы С2-36 – это резисторы постоянные непроволочные общего применения, всеклиматического неизолированного исполнения, предназначенные для работы в электрических цепях постоянного, переменного и импульсного токов.

4 РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ УСТРОЙСТВА. ОПИСАНИЕ ЕЁ РАБОТЫ. ДИАГРАММА РАБОТЫ УСТРОЙСТВА

4.1 Схемотехнические решения при разработке принципиальной схемы устройства

Разработанная принципиальная схема БНТУ113010.036 Э3 представлена в приложении 2.

Данная схема содержит реализацию блока ввода (БВв), операционного блока (ОБ), блока вывода (БВыв) и блока индикации (БИ). Рассмотрим схемотехнические решения по каждому блоку.

Блок ввода (БВв) реализован на следующих элементах DD1.3, DD2.1, DD3, DD6 и R1.

Модуль ZВв БВв реализован на элементах DD1.3, DD2.1, DD3 и R1. Элемент R1 формирует логическую единицу и подключен к входу 1 (EAB) буферного элемента DD3, что обеспечивает прием информации по каналу A (внешняя шина ввода) и передачу ее в канал B (внутренняя шина устройства). Входы 3-9 (A1-A7) DD3 не используются и подключены к общему. На вход 2 (A0) DD3 последовательно поступает информация с внешней шины данных (разряды вводимого числа начиная с младшего). Инверсный вход 19 (E0) DD3 подключен к инверсному выходу 6 триггера DD2.1, который обеспечивает подключение БВв к внешней шине на время ввода данных.

Триггер DD2.1 включен в режиме работы по установочным входам, входы 2 (D) и 3 (C) DD2.1 подключены к общему. Управляющий сигнал «ПОДКЛ. К ШВв» (уровень логического нуля) переключает триггер в состояние единицы, что обеспечивает наличие нуля на инверсном выходе 6 DD2.1 и соответственно подключение буферного элемента DD3 к шине ввода. В состоянии единицы триггер находится до момента окончания ввода.

Третье состояние устанавливается подачей сигнала «ОТКЛ. ОТ ШВв» (уровень логического нуля). Данный сигнал подается на вход 9 ЛЭ И DD1.3, что обеспечивает ноль на выходе 8 DD1.3, который подключен к инверсному входу 1 (R) DD2.1 что влечет за собой переключение триггера DD2.1 в нулевое состояние и соответственно входа 6, данного триггера в единичное. Единица входа 6 DD2.1 устанавливает третье состояние буферного элемента DD3, что отключает DD3 от внешней шины ввода.

Также на вход 10 ЛЭ DD1.3 поступает сигнал «ОСТАНОВ» (уровень логического нуля), который также как и сигнал «ОТКЛ. ОТ ШВв» устанавливает третье состояние буферного элемента DD3. Сигнал «ОСТАНОВ» запрещает подключение к внешней шине ввода когда устройство находится в нерабочем режиме, т.е. в режиме «ОСТАНОВ».

ЛЭ DD1.3 обеспечивает состояние нуля на выходе при наличии хотя бы одного нуля на входе. Согласно условию последовательности работы устройства, управляющие сигналы «ОСТАНОВ» и «ОТКЛ. ОТ ШВв» одновременно поданы быть не могут, поэтому схемотехническое решение по исключению подачи запрещенной комбинации предусматривать не имеет смысла.

Модуль МХрD реализован на элементах DD6 и R1, которые обеспечивают последовательный ввод информации.

Ввод информации последовательно разряд за разрядом передается из буферного элемента в регистр. Такое решение выполнено соединением выхода 18 (B0) DD3 c входом 22 (DSL) регистра DD5 и подачей уровня логической единицы от резистора R1 к входу 23 (S1) DD5, к инверсному 13 (R) DD5, а также подключением входа 1 (S0) DD5 к общему, т.е. к уровню логического нуля. Таким образом реализуется подключение регистра при сдвиге влево, согласно состояниям работы ИМС 133ИР13 (таблица 3). Входы 2, 3, 5, 7, 9, 15, 17, 19 и 21 можно оставить свободными при таком включении, т.к. они не будут влиять на работу регистра.

Ввод последовательно каждого разряда из выхода 18 (B0) DD3 будет осуществлятся при подаче высокого тактового сигнала на синхровход 11 (C) DD5. При этом вводимый разряд записывается в регистр и доступен по выходу 20 (Q7) DD5. Разряд который хранился на выходе 20 (Q7) до прихода синхроимпульса перезаписывается и доступен по выходу 18 (Q6). Таким образом при каждом синхроимпульсе происходит запись вводимого разряда и сдвиг влево, т.е. к выходу 4 (Q0) ранее записанных разрядов.

На синхровход 11 (C) DD5 подается команда «ВВОД i» (уровень логической единицы). Команда «ВВОД i» объединяет в себе команды «ВВОД D0», «ВВОД D1» … «ВВОД D7». Данное объединение происходит в блоке управления (БУ).

Введенная информация (сигнал D) поступает с выходов регистра DD5 в шестнадцатиразрядную шину.

Операционный блок (ОБ) реализован на элементах DD4, DD6, DD7, DD9, R1 и R2.

Модуль МХрP реализован на регистре DD4 и резисторе R1.

Пороговое значение P, хранящееся в устройстве формируется соответствующей подачей уровня логических единиц от резистора R1 и подачей уровня логических нулей (т.е. заземление) на входы 3, 5, 7, 9, 15, 17, 19 (D0, D1, D2, D3, D4, D5, D6, D7 соответственно) регистра DD4. Регистр включен в режиме параллельной загрузки данных. Этот режим задается подачей сигналов уровня логической единицы на инверсный вход 13 (R) и входы 1 (S0), 23 (S1), согласно состояниям работы ИМС 133ИР13 (таблица 3). Сигналы уровня логической единицы формируются резистором R1. Входы 2 и 22 DD4 можно оставить свободными, они не несут влияния на работу регистра при параллельной загрузке.

Параллельная загрузка данных подготовленных на входах 3, 5, 7, 9, 15, 17, 19 DD5 происходит при подаче высокого перепада на вход 11 (C) DD4. Т.е. при подаче синхроимпульса (команда «СОХРАН. P» уровня логической единицы) данные подготовленные на входах загружаются в регистр и доступны на выходах 4, 6, 8, 10, 14, 16, 18, 20 (Q0, Q1, Q2, Q3, Q4, Q5, Q6, Q7 соответственно) DD4.

Сохраненная информация (сигнал P) поступает с выходов регистра DD4 в шестнадцатиразрядную шину.

Модуль МСрDиP реализован на DD6, DD7 и R2.

ИМС 533СП1 предназначена для сравнения двух четырехразрядных чисел, но каскадированием можно добиться и большей разрядности чисел сравнения. Для сравнения восьмиразрядных чисел используют последовательный способ наращивания разрядности, т.е. когда выходы компаратора младших разрядов подключены к управляющим входам компаратора старших разрядов. Таким образом выходы 7, 6 и 5 DD6 подключаются к входам 2, 3 и 4 DD7 соответственно. В компараторе DD6, сравнения младших разрядов, разряды D0, D1, D2, D3 из шестнадцатиразрядной внутренней шины устройства подаются на входы 10, 12, 13, 15 DD6 соответственно, а разряды P0, P1, P2, P3 на входы 9, 11, 14, 1 DD6. В компараторе DD7, сравнения старших разрядов, разряды D4, D5, D6, D7 из шестнадцатиразрядной внутренней шины устройства подаются на входы 10, 12, 13, 15 DD7 соответственно, а разряды P4, P5, P6, P7 на входы 9, 11, 14, 1 DD7.

На управляющие входы компаратора, осуществляющего сравнение младших разрядов, т.е. DD6, необходимо подать сигналы, соответствующие равенству еще более младших разрядов, т.е. сигналы якобы о равенстве несуществующих еще более младших разрядов. Для этого на вход 3 DD6 подается уровень логической единицы от резистора R2, а входы 2 и 4 DD6 заземляются, т.е. на них подается уровень нуля.

Компаратор DD7 может выдавать три результата сравнения, на этих результатах и строятся модули МФПрD<=P и МФПрD>P. Если сигнал D превышает порог P, то уровень сигнала на выходе 5 DD7 будет единицей, в противном случае нулем. Выход 5 DD7 и является формированием признака D>P (уровень логической единицы), в зависимости от результатов сравнения. Для формирования признака D<=P используются выходы 7 и 6 DD7, которые подключены ко входам 1 и 2 ЛЭ ИЛИ DD9.1 соответственно. При наличии единицы на выходе 7 или 6 DD7 формируется признак D<P или D=P соответственно, т.е. при наличии одного из этих признаков ЛЭ DD9.1 будет формировать признак D<=P. Таким образом выход 3 DD9.2 является формированием признака D<=P (уровень логической единицы).

Неиспользуемые в корпусе DD9 ЛЭ 2, 3 и 4 выводятся в состояние наименьшей потребляемой мощности. Состоянием наименьшей потребляемой мощности для ЛЭ ИМС КР1531ЛЛ1 является единица, т.к. ток потребления в состоянии единицы меньше тока потребления в состоянии логического нуля (таблицу 12). Для вывода ЛЭ ИЛИ в состояние единицы нужно подать хотя бы одну единицу на вход. На входы 5 DD9.2, 10 DD9.3 и 12 DD9.4 подается логическая единица от резиcтора R2, а входы 4, 9 и 13 этих ЛЭ подключаются к общему.

Блок вывода (БВыв) реализован на следующих элементах DD1.4, DD2.2, DD8, DD10, DD11 и R2.

Модуль МХрA организован аналогично модулю МХрP операционного блока (ОБ) на регистре DD8.

Адрес извещателя, хранящийся в устройстве формируется соответствующей подачей уровня логических единиц от резистора R2 и подачей уровня логических нулей (т.е. заземление) на входы 3, 5, 7, 9, 15, 17, 19 (D0,D1,D2,D3,D4,D5,D6,D7 соответственно) регистра DD9. Регистр включен в режиме параллельной загрузки данных. Этот режим задается подачей сигналов уровня логической единицы на инверсный вход 13 (R) и входы 1 (S0), 23 (S1), согласно состояниям работы ИМС 133ИР13 (таблица 3). Сигналы уровня логической единицы формируются резистором R2. Входы 2 и 22 DD8 можно оставить свободными, они не несут влияния на работу регистра при параллельной загрузке.

Параллельная загрузка данных подготовленных на входах 3, 5, 7, 9, 15, 17, 19 DD8 происходит при подаче высокого перепада на вход 11 (C) DD8. Т.е. при подаче синхроимпульса (команда «СОХРАН. A» уровня логической единицы) данные подготовленные на входах загружаются в регистр и доступны на выходах 4, 6, 8, 10, 14, 16, 18, 20 (Q0, Q1, Q2, Q3, Q4, Q5, Q6, Q7 соответственно) DD8.

Модуль МПрЦА реализован на элементах DD1.4, DD2.2, DD10 и DD11.

Входы 8-19 (D1-D12 соответственно) DD10 используются для принятия цифрового кода, который будет преобразован в аналоговый. Т.к. цифровой код имеет восемь разрядов, а DD10 рассчитана на 12 цифровых разрядов, входы 16, 17, 18, 19, т.е. входы старших разрядов необходимо заземлить (подать на них логический ноль). Входы 8, 9, 10, 11, 12, 13, 14, 15 DD10 подключаются к выходам 4, 6, 8, 10, 14, 16, 18, 20 DD9 соответственно, на которых находится адрес в виде цифрового кода.

Вход 38 (U0) ЦАП DD10 – это вход для подачи опорного напряжения, опорное напряжение для данной ИМС +10,24 В.

Прием подготовленных на входах DD10 цифровых данных во внутренние регистры ЦАП производится подачей единицы на входы 6 (С1) и 21 (С2). Входы 6 и 21 DD10 подключены к выходу 8 триггера DD2.2. Триггер DD2.2 включен в режиме работы по установочным входам, входы 12 (D) и 11 (C) DD2.2 подключены к общему. Управляющий сигнал «РАЗРЕШ. ВЫВОД» (уровень логического нуля) переключает триггер в состояние единицы, что обеспечивает наличие единицы на выходе 8 DD2.2 и соответственно прием подготовленных на входах DD10 цифровых данных во внутренние регистры ЦАП. Триггер находится в состоянии единицы в течение определенного времени, достаточного для преобразования и передачи адреса извещателя. После этого поступает команда «ЗАПРЕТ. ВЫВОД» (уровень логического нуля) на вход 12 ЛЭ И DD1.4, выход 11 которого подключен к входу 13 триггера DD2.2. Команда «ЗАПРЕТ. ВЫВОД» дает на выходе 11 ЛЭ И DD1.4 ноль, который устанавливает триггер DD2.2 в нулевое состояние, что обеспечивает окончание приема цифрового кода в регистры ЦАП и соответственно прекращает преобразование и передачу аналогового сигнала, который несет информацию с адресом извещателя. Команда «ЗАПРЕТ. ВЫВОД» была организована при разработке принципиальной схемы устройства. Она необходима для того чтобы отключать вывод аналогового сигнала A, т.к. при её отсутствии, когда осуществлялось бы превышение порогового значения, аналоговый сигнал передавался бы постоянно без какой-либо зависимости от последующих результатов сравнения операционного блока.

Также на вход 13 ЛЭ DD1.4 поступает сигнал «ОСТАНОВ» (уровень логического нуля), который также как и сигнал «ЗАПРЕТ. ВЫВОД» устанавливает триггер DD2.2 в нулевое состояние, что обеспечивает окончание приема цифрового кода в регистры ЦАП и соответственно прекращает преобразование и передачу аналогового сигнала, который несет информацию с адресом извещателя. Сигнал «ОСТАНОВ» запрещает преобразование и передачу адреса извещателя когда устройство находится в нерабочем режиме, т.е. в режиме «ОСТАНОВ».

ЛЭ DD1.4 обеспечивает состояние нуля на выходе при наличии хотя бы одного нуля на входе. Согласно условию последовательности работы устройства, управляющие сигналы «ОСТАНОВ» и «ЗАПРЕТ. ВЫВОД» одновременно поданы быть не могут, поэтому схемотехническое решение по исключению подачи запрещенной комбинации предусматривать не имеет смысла.

Неиспользуемые в корпусе DD1 ЛЭ 1 и 2 выводятся в состояние наименьшей потребляемой мощности. Состоянием наименьшей потребляемой мощности для ЛЭ ИМС КР1531ЛИ1 является единица, т.к. ток потребления в состоянии единицы меньше тока потребления в состоянии логического нуля (таблица 14). Для вывода ЛЭ И в состояние единицы нужно подать единицу на все имеющиеся входы. На входы 1,2 DD1.1 и 4,5 DD1.2 подается логическая единица от резиcтора R1.

ЦАП DD10 осуществляет преобразование и усиление сигнала адреса совместно с ИМС ОУ 153УД3. Вход 47 (Y) DD10 – это вход для обратной связи ОУ. К входу 47 DD10 подключается выход 6 ОУ DD11. Выходы 48 (J1) и 2 (J2) DD10 необходимо объединить и подать на инверсный вход 2 ОУ DD11. Прямой вход 3 DD11 заземляется. Усиление сигнала производиться ИМС относительно напряжения равного нулю. На входы 7 и 4 ОУ DD11 необходимо подать напряжение питания для данной ИМС +15 В и -15 В соответственно.

На выходе 6 DD11 будет получен требуемый аналоговый сигнал A, несущий адрес извещателя.

Блок индикации (БИ) реализован на элементах DD12, DD13, R3, R4, HL1 и HL2.

Индикация ОСТАНОВ реализована на элементах DD12.1, DD13.1, R3 и HL1. Триггер DD12.1 включен в работу по установочным входам, входы 2 и 3 DD12.1 данного триггера заземляются. На инверсный вход 4 триггера подается команда «ВКЛЮЧЕНИЕ “ОСТАНОВ”» (уровень логического нуля). При данной команде триггер переключается в единицу и инверсный выход 6 DD12.1 имеет состояние нуля. Выход 6 DD12.1 подключен к входам 1 и 2 ЛЭ И DD13.1 с открытым коллектором. При этом нули на входах ЛЭ И обеспечивают нулевое состояние на выходе 5 данного ЛЭ. К выходу 5 DD13.1 подключен светодиод HL1 (обратное включение) на который через резистор R3 подается соответствующий ток. При нуле на выходе 5 DD13.1 ток от резистора протекает через светодиод в коллектор ЛЭ И. При протекании тока светодиод испускает свечение красного цвета, что сигнализирует о том что устройство находится в режиме ОСТАНОВ.

При подаче команды «ГАШЕНИЕ “ОСТАНОВ”» (уровень логического нуля) на вход 1 триггера DD12.1, триггер переключается в состояние нуля и инверсный выход 6 имеет состояние единицы. Напряжение с выхода 5 DD13.1 запирает p-n-переход светодиода HL1, ток через светодиод не протекает и соответственно свечения нет.

Индикация РАБОТА реализована на элементах DD12.2, DD13.2, R4 и HL2. Индикация РАБОТА реализована аналогично индикации ОСТАНОВ. Триггер DD12.2 включен в работу по установочным входам, входы 12 и 11 DD12.2 данного триггера заземляются. На инверсный вход 10 триггера подается команда «ВКЛЮЧЕНИЕ “РАБОТА”» (уровень логического нуля). При данной команде триггер переключается в единицу и инверсный выход 9 DD12.2 имеет состояние нуля. Выход 9 DD12.2 подключен к входам 12 и 13 ЛЭ И DD13.2 с открытым коллектором. При этом нули на входах ЛЭ И обеспечивают нулевое состояние на выходе 10 данного ЛЭ. К выходу 10 DD13.2 подключен светодиод HL2 (обратное включение) на который через резистор R4 подается соответствующий ток. При нуле на выходе 10 DD13.1 ток от резистора протекает через светодиод в коллектор ЛЭ И. При протекании тока светодиод испускает свечение зеленого цвета, что сигнализирует о том что устройство находится в режиме РАБОТА.

При подаче команды «ГАШЕНИЕ “РАБОТА”» (уровень логического нуля) на вход 13 триггера DD12.2, триггер переключается в состояние нуля и инверсный выход 9 имеет состояние единицы. Напряжение с выхода 10 DD13.2 запирает p-n-переход светодиода HL2, ток через светодиод не протекает и соответственно свечения нет.

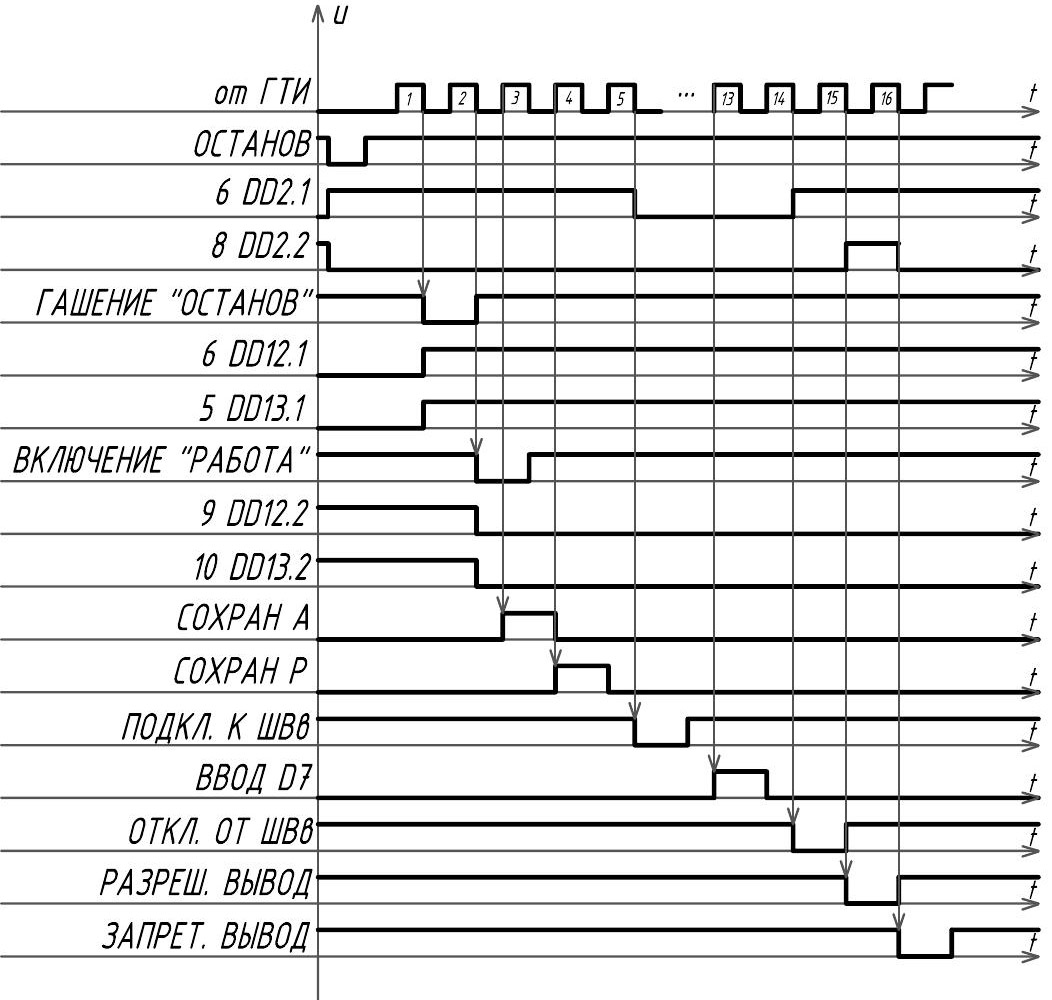

4.2 Описание работы. Диаграмма работы устройства

В разрабатываемом устройстве есть два режима ОСТАНОВ и РАБОТА.

При подаче питания устройство находится в режиме ОСТАНОВ. Блоком управления вырабатывается команда «ОСТАНОВ» уровня логического нуля, (рисунок 13, ось диаграммы ОСТАНОВ), которая поступает на вход 10 DD1.3 и через выход 8 DD1.3 устанавливает выход 6 триггера DD2.1 в единицу (ось диаграммы 6 DD2.1). Единица на выходе 6 DD2.1 устанавливает третье состояние буферного элемента DD3, что запрещает подключение к шине ввода данных во время режима ОСТАНОВ. Также команда «ОСТАНОВ» подается на вход 13 DD1.4 и через выход 11 DD1.4 устанавливает выход 8 триггера DD2.2 в состояние нуля (ось диаграммы 8 DD2.2). Ноль на выходе 8 триггера DD2.2 запрещает прием данных в регистры ЦАП DD10 и соответственно преобразование и передачу адреса извещателя. Также блоком управления формируется команда «ВКЛЮЧЕНИЕ “ОСТАНОВ”», поступающая на вход 4 триггера DD12.1. Данная команда устанавливает выход 6 триггера DD12.1 в ноль, который также формирует ноль на выходе 5 DD13.1, что позволяет протекать току через светодиод HL1. При протекании тока через HL1 происходит свечение индикатора “ОСТАНОВ” красным цветом, что информирует о не рабочем состоянии устройства.

Рисунок 13 – Диаграмма работы устройства

Устройство запускается в режим РАБОТА нажатием кнопки «СТАРТ».

В данном режиме работа блока управления обеспечивается некоторой последовательностью тактовых импульсов, передаваемых генератором тактовых импульсов (ГТИ).

При поступлении первого тактового импульса формируется команда «ГАШЕНИЕ “ОСТАНОВ”» (ось диаграммы ГАШЕНИЕ “ОСТАНОВ”). Данная команда устанавливает выход 6 триггера DD12.1 (ось диаграммы 6 DD12.1) в состояние единицы, который в свою очередь устанавливает состояние единицы на выходе 5 DD13.1 (ось диаграммы 5 DD13.1). Напряжение с выхода 5 DD13.1 запирает p-n-переход светодиода HL1, ток через светодиод не протекает и соответственно свечения нет.

При поступлении второго тактового импульса формируется команда «ВКЛЮЧЕНИЕ “РАБОТА”» (ось диаграммы ВКЛЮЧЕНИЕ “РАБОТА”). Данная команда устанавливает выход 9 триггера DD12.2 (ось диаграммы 9 DD12.2) в состояние нуля, который в свою очередь устанавливает состояние нуля на выходе 10 DD13.2 (ось диаграммы 10 DD13.2), что позволяет протекать току через светодиод HL2. При протекании тока через HL2 происходит свечение индикатора “РАБОТА” зеленым цветом, что информирует о работе устройства.

При поступлении третьего тактового импульса формируется команда «СОХРАН. A» (ось диаграммы СОХРАН. A). Данная команда осуществляет параллельную загрузку цифрового кода (адреса A) в регистр DD8.

При поступлении четвертого тактового импульса формируется команда «СОХРАН. P» (ось диаграммы СОХРАН. P). Данная команда осуществляет параллельную загрузку цифрового кода (порогового значения P) в регистр DD4.

При поступлении пятого тактового импульса формируется команда «ПОДКЛ. К ШВв» (ось диаграммы ПОДКЛ. К ШВв), которая поступает на вход 4 триггера DD2.1 и устанавливает выход 6 триггера DD2.1 в ноль (ось диаграммы 6 DD2.1). Ноль на выходе 6 DD2.1 подключает буферный элемент DD3 к шине ввода данных.

Далее при поступлении, с шестого по тринадцатый тактовых импульсов, блоком управления формируется 8 управляющих команд ввода «ВВОД D0» … «ВВОД D7». На диаграмме эти сигналы показаны на примере одного сигнала «ВВОД D7». Команда ввода каждого разряда вводимого числа «ВВОД i» подается на синхровход 11 регистра DD5.

При поступлении четырнадцатого тактового импульса формируется команда «ОТКЛ. ОТ ШВв» (ось диаграммы «ОТКЛ. ОТ ШВв»). Эта команда устанавливает на 6 выходе DD2.1 (ось диаграммы 6 DD2.1) единичное состояние и переводит буферный элемент в третье состояние.

Для процедуры сравнения команда от блока управления не вырабатывается. При поступлении данных на входы DD6 и DD7, т.е. компараторов, автоматически начинается процедура сравнения D и P.

Если после процедуры сравнения формируется признак D>P, то при поступлении пятнадцатого тактового импульса вырабатывается команда «РАЗРЕШ. ВЫВОД» (ось диаграммы РАЗРЕШ. ВЫВОД). Эта команда подается на вход 10 триггера DD2.2 и устанавливает на выходе 8 DD2.2 (ось диаграммы 8 DD2.2) уровень единицы. Единица на выходе 8 DD2.2 позволяет ЦАП DD10 принять данные на входах и начать преобразование и передачу адреса A.

При поступлении шестнадцатого тактового импульса формируется команда «ЗАПРЕТ. ВЫВОД» (ось диаграммы «ЗАПРЕТ. ВЫВОД»), которая подается на вход 12 триггера DD1.4 и устанавливает на выходе 8 DD2.2 (ось диаграммы 8 DD2.2) уровень нуля. Ноль на выходе 8 DD2.2 не позволяет ЦАП DD10 принимать данные на входах, преобразовывать и передавать адрес A до следующего прихода команды «РАЗРЕШ. ВЫВОД». После этого от блока управления приходит команда «ПОДКЛ. К ШВв» и описанная выше работа устройства повторяется.

Если после сравнения D и P формируется признак D<=P, то от блока управления также приходит команда «ПОДКЛ. К ШВв» и работа устройства повторяется.

5 РАСЧЕТНАЯ ЧАСТЬ

5.1 Расчет и выбор номиналов резисторов

Для формирования токов уровня логической единицы, подаваемой на элементы ТТЛ(Ш,) при наличии напряжении питания UП = 5 В, используются резисторы. У элементов ТТЛ(Ш) уровень U1 на 1,5-2 В ниже UП, поэтому для предотвращения пробоев, вход на котором нужно сформировать единицу, подключают к источнику питания UП через резистор R (обычно 1 кОм), причем к одному резистору разрешается подключить до 20 входов [7]. В соответствии с этим условием, выбираем резисторы R1 и R2 из ряда E12 номиналом в 1 кОм ±10%.

Светодиод КИПМ02А-1К (ОСТАНОВ) имеет значение номинального прямого тока Iпр ном = 10 мА = 0.01 А и прямое падение напряжения на светодиоде при данном токе Uпр = 2 В (таблица 17). Учитывая напряжение питания UП = 5 В, найдем токоограничивающее сопротивление R3, для светодиода HL1, по формуле:

R3 = UП - Uпр / Iпр ном = 5 – 2 / 0.01 = 300 Ом.

Из ряда E12 выбираем резистор R3 номиналом в 330 Ом ± 10%.

Светодиод КИПМ03В-1Л (РАБОТА) имеет значение номинального прямого тока Iпр ном = 20 мА = 0.02 А и прямое падение напряжения на светодиоде при данном токе Uпр = 2.8 В (таблица 17). Учитывая напряжение питания UП = 5 В, найдем токоограничивающее сопротивление R4, для светодиода HL2, по формуле:

R4 = UП - Uпр / Iпр ном = 5 – 2.8 / 0.02 = 110 Ом.

Из ряда E12 выбираем резистор R4 номиналом в 120 Ом ± 10%.

5.2 Расчет времени задержки

Для корректной работы всего устройства необходимо, чтобы импульсы, поступающие от генератора тактовых импульсов, имели длительность больше, чем средняя задержка распространения сигнала по схеме.

Для этого необходимо определить самую длинную цепочку последовательных элементов схемы, то есть совокупность элементов схемы, через которые последовательно проходят информационные сигналы, обрабатываемые схемой, после формирования конкретного управляющего сигнала.

Самая длинная цепочка определяется путем анализа работы устройства по каждому управляющему сигналу.

При расчете временной задержки последовательно включенных элементов используется средняя задержка распространения сигнала каждым элементом схемы (tЭСХзд р ср), определяемая по формуле:

tЭСХзд р ср = (t10зд р + t01зд р)/2.

Параметры t10зд р и t01зд р являются справочными данными.

Среднее время распространения сигнала по всей цепочке рассчитывается по формуле

где N – количество элементов в самой длинной цепочке схемы, tЭСХзд р ср – средняя задержка распространения сигнала элементом цепочки схемы.

Проведя анализ данных, а конкретно задержки (времени) распространения сигнала (таблица 2, 4, 5, 8, 10, 12, 14, 15), использовавшихся элементов, очевидно, что время установления выходного тока ЦАП DD10 на 3 порядка выше средних задержек распространения остальных элементов. Тогда однозначно можно утверждать, что самая длительная цепочка распространения сигнала по схеме, это цепочка содержащая ЦАП DD10 и триггер DD2.2 (команда «РАЗРЕШ. ВЫВОД»).

Так как время установления выходного тока (т.е. сигнала) ЦАП DD10 равно tDD10зд р ср = 10 мкс (таблица 15) и задержка распространения сигнала на триггере DD2.2: tDD2.2зд р ср = (40 + 25) / 2 = 32.5 нс = 0.0325 мкс (таблица 8), то средняя задержка распространения сигнала по схеме равна:

tСХзд р ср = 10 + 0.0325 = 10.0325 мкс.

Тогда длительность тактового импульса должна соответствовать условию tи > tСХзд р ср, т.е. tи > 10.0325 мкс.

5.3 Расчет потребляемой мощности

Мощность, потребляемая устройством, складывается из мощностей, потребляемых всеми элементами, включенными в схему.

Если токи потребления в состоянии 0 и 1 равны, то расчет потребляемой мощности логического элемента осуществляется по формуле

PЛЭпот = (Uпит·Iпот).

Если токи потребления в состоянии 0 и 1 не равны, то

PЛЭпот = (I0пот+I1пот)/2 · Uпит.

Для всего корпуса потребляемая мощность рассчитывается по формуле

где n – количество элементов в корпусе, РЛЭ – мощность, потребляемая одним логическим элементом.

Для всей схемы потребляемая мощность рассчитывается как

где N– количество корпусов в схеме, РК – мощность, потребляемая одним корпусом.

На основании таблиц 2, 4, 5, 8, 10, 12, 14, 15 и 16, для корректности расчета составим сводную таблицу следующего вида, таблица 18.

Таблица 18 – Сводная таблица значений Iпот

|

№№

|

Типы микросхем

|

Кол-во корпусов

|

Кол-во элементов в корпусе

|

Всего элементов для расчета

|

Iпот1,

А

|

Iпот0,

А

|

Iпот,

А

|

|

1

|

533АП6

|

1

|

1

|

1

|

0.070

|

0.090

|

0.080

|

|

2

|

133ИР13

|

3

|

1

|

3

|

-

|

-

|

0.104

|

|

3

|

533СП1

|

2

|

1

|

2

|

-

|

-

|

0.020

|

|

4

|

533ТМ2

|

2

|

2

|

4

|

-

|

-

|

0.008

|

|

5

|

155ЛИ5

|

1

|

2

|

2

|

0.011

|

0.065

|

0.038

|

|

6

|

КР1531ЛЛ1

|

1

|

4

|

4

|

0.0083

|

0.0155

|

0.0119

|

|

7

|

КР1531ЛИ1

|

1

|

4

|

4

|

0.0083

|

0.0129

|

0.0106

|

|

8

|

572ПА2

|

1

|

1

|

1

|

-

|

-

|

0.002

|

|

9

|

153УД3

|

1

|

1

|

1

|

-

|

-

|

0.004

|

Рассчитаем мощность, потребляемую ИМС под пунктами 1-7 таблицы 18, в схеме. Напряжение питания у этих ИМС одинаковое и равно Uпит = +5В.

Для ИМС 533АП6:

P533АП6пот = (Uпит·Iпот) = 5 · 0.080 = 0.4 Вт.

Т.к. в схеме 1 ИМС 533АП6, то общая мощность, потребляемая этими ИМС равна:

PСХ 533АП6пот = P533АП6пот · 1 = 0.4 Вт.

Для ИМС 133ИР13:

P133ИР13пот = (Uпит·Iпот) = 5 · 0.104 = 0.52 Вт.

Т.к. в схеме 3 ИМС 133ИР13, то общая мощность, потребляемая этими ИМС равна:

PСХ 133ИР13пот = P133ИР13пот · 3 = 0.52 · 3 = 1.56 Вт.

Для ИМС 533СП1:

P533СП1пот = (Uпит·Iпот) = 5 · 0.020 = 0.1 Вт.

Т.к. в схеме 2 ИМС 533СП1, то общая мощность, потребляемая этими ИМС равна:

PСХ 533СП1пот = P533СП1пот · 2 = 0.1 · 2 = 0.2 Вт.

Для ИМС 533ТМ2:

PЛЭ 533ТМ2пот = (Uпит·Iпот) = 5 · 0.008 = 0.04 Вт.

Т.к. в корпусе ИМС 533СП1 2 элемента, то мощность, потребляемая корпусом этой ИМС равна:

P533ТМ2пот = PЛЭ 533ТМ2пот · 2 = 0.04 · 2 = 0.08 Вт.

Т.к. в схеме 2 ИМС 533ТМ2, то общая мощность, потребляемая этими ИМС равна:

PСХ 533ТМ2пот = P533ТМ2пот · 2 = 0.08 · 2 = 0.16 Вт.

Для ИМС 155ЛИ5:

PЛЭ 155ЛИ5пот = (Uпит·Iпот) = 5 · 0.038 = 0.19 Вт.

Т.к. в корпусе ИМС 155ЛИ5 2 элемента, то мощность, потребляемая корпусом этой ИМС равна:

P155ЛИ5пот = PЛЭ 155ЛИ5пот · 2 = 0.19 · 2 = 0.38 Вт.

Т.к. в схеме 1 ИМС 155ЛИ5, то общая мощность, потребляемая этими ИМС равна:

PСХ 155ЛИ5пот = P155ЛИ5пот · 1 = 0.38 Вт.

Для ИМС КР1531ЛЛ1:

Т.к. в схеме используется один ЛЭ ИМС КР1531ЛЛ1, а остальные 3 выведены в режим наименьшей потребляемой мощности то:

PЛЭ СР КР1531ЛЛ1пот = (Uпит·Iпот) = 5 · 0.0119 = 0.0595 Вт.

Для 3 ЛЭ которые выведены в состояние единицы:

PЛЭ 1 КР1531ЛЛ1пот = (Uпит·Iпот1) = 5 · 0.0083 = 0.0415 Вт.

PК ЛЭ 1 КР1531ЛЛ1пот = PЛЭ 1 КР1531ЛЛ1пот · 3 = 0.0415 · 3 = 0.1245 Вт.

Т.к. в схеме 1 ИМС КР1531ЛЛ1, то мощность потребляемая корпусом и соответственно такими ИМС в схеме равны:

PСХ КР1531ЛЛ1пот = PКР1531ЛЛ1пот =

= PК ЛЭ 1 КР1531ЛЛ1пот + PЛЭ СР КР1531ЛЛ1пот = 0.1245 + 0.0595 = 0.184 Вт.

Для ИМС КР1531ЛИ1:

Т.к. в схеме используется два ЛЭ ИМС КР1531ЛЛ1, а остальные 2 выведены в режим наименьшей потребляемой мощности то:

PЛЭ СР КР1531ЛИ1пот = (Uпит·Iпот) = 5 · 0.0106 = 0.053 Вт.

PК ЛЭ СР КР1531ЛИ1пот = PЛЭ СР КР1531ЛЛ1пот · 2 = 0.053 · 2 = 0.106 Вт.

Для 2 ЛЭ которые выведены в состояние единицы:

PЛЭ 1 КР1531ЛИ1пот = (Uпит·Iпот1) = 5 · 0.0083 = 0.0415 Вт.

PК ЛЭ 1 КР1531ЛИ1пот = PЛЭ 1 КР1531ЛИ1пот · 2 = 0.0415 · 2 = 0.083 Вт.

Т.к. в схеме 1 ИМС КР1531ЛИ1, то мощность потребляемая корпусом и соответственно такими ИМС в схеме равны:

PСХ КР1531ЛИ1пот = PКР1531ЛИ1пот =

= PК ЛЭ 1 КР1531ЛИ1пот + PК ЛЭ СР КР1531ЛЛ1пот = 0.106 + 0.083 = 0.189 Вт.

Рассчитаем максимальную мощность потребляемую ИМС 572ПА2, учитывая максимальное напряжение питания Uпит = 15 В (таблица 15) и ток потребления (таблица 18):

P572ПА2пот = (Uпит·Iпот) = 15 · 0.002 = 0.03 Вт.

Т.к. в схеме 1 ИМС 572ПА2, то общая мощность, потребляемая этой ИМС равна:

PСХ 572ПА2пот = P572ПА2пот · 1 = 0.03 Вт.

Рассчитаем мощность потребляемую ИМС 153УД3, учитывая напряжение питания Uпит = 15 В (таблица 16) и ток потребления (таблица 18):

P153УД3пот = (Uпит·Iпот) = 15 · 0.004 = 0.06 Вт.

Т.к. в схеме 1 ИМС 153УД3, то общая мощность, потребляемая этой ИМС равна:

PСХ 153УД3пот = P153УД3пот · 1 = 0.06 Вт.

Рассчитаем общую мощность для всех ИМС в схеме, используя ранее рассчитанные данные мощности:

PСХпот = PСХ 533АП6пот + PСХ 133ИР13пот + PСХ 533СП1пот + PСХ 533ТМ2пот +

+ PСХ 155ЛИ5пот + PСХ КР1531ЛЛ1пот + PСХ КР1531ЛИ1пот + PСХ 572ПА2пот + PСХ 153УД3пот =

= 0.4 + 1.56 + 0.2 + 0.16 + 0.38 + 0.184 + 0.189 + 0.03 + 0.06 = 3.163 Вт

Мощность потребляемая устройством (не учитывая блок управления) равна PСХпот = 3.163 Вт.

ЗАКЛЮЧЕНИЕ

В ходе курсового проектирования осуществлена частичная разработка адресного порогового извещателя. Создан алгоритм работы данного устройства, разработана функциональная схема. При разработке принципиальной схемы адресного порогового извещателя спроектированы блоки ввода, вывода, операционный и индикации. Реализация блока управления устройства при разработке принципиальной схемы не проводилась.

Курсовой проект выполнен в соответствии с поставленной задачей. Учтены все исходные данные, приведенные в задании по курсовому проектированию.

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

- Богданович, М.И. Цифровые интегральные схемы. Справочник/ М.И. Богданович. – Минск: Беларусь, 1991. – 23-25, 47, 55, 56, 62, 64, 98, 107-109, 126-129, 191-192, 224, 268, 272-273, 279 с.

- Федорков Б.Г. Микросхемы ЦАП и АЦП: функционирование, параметры, применение/ Б.Г. Федорков. – Москва: Энергоатомиздат, 1990. – 79-82 с.

- Little home system www.asvcorp.ru / Цифровая археология , Электронные компоненты, Микросхема 572ПА2. – Режим доступа: http://www.asvcorp.ru/darch/electronics/572pa2/index.html – Дата доступа: 28.10.2012.

- Портал для радиолюбителей www.radioman-portal.ru / Отечественные операционные усилители - полные справочные данные. – Режим доступа: http://www.radioman-portal.ru/sprav/pp/oa – Дата доступа: 28.10.2012.

- Интернет-ресурс www.radiosvalka.narod.ru / Справочник, Отечественные излучающие диоды. – Режим доступа: http://www.radiosvalka.narod.ru/spravka/diodes/diodes_ik.htm – Дата доступа: 01.11.2012.

- Справочники по отечественным электронным компонентам с Datasheets www.trzrus.narod.ru / Резисторы, Постоянные, Резисторы непроволочные общего применения. – Режим доступа: http://trzrus.narod.ru/rec/recany.htm?6../res.htm – Дата доступа: 01.11.2012.

- Электроника (цифровая электроника). Лабораторные работы для студентов дневной формы обучения/ Г.Ф. Жердева. – Минск: БНТУ, 2012. – Л.Р.3 5-6 с.

PAGE \* MERGEFORMAT49

Адресный пороговый извещатель