Вычислительные системы и микропроцессорная техника

МОСКОВСКИЙ ОРДЕНА ЛЕНИНА И ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ

АВИАЦИОННЫЙ ИНСТИТУТ имени СЕРГО ОРДЖОНИКИДЗЕ

_______________

Кафедра 4 0 3

Р А i Е Т Н О - П О Я С Н И Т Е Л Ь Н А Я З А П И С К А

к курсовой работе по дисциплине

тАЬВычислительные системы и микропроцессорная техникатАЭ

Выполнял

студент группы 04-415 ______________ Телятников И.А.

Консультировал _______________ Герасимов А.Л.

Москва

1996 г.

1. ЗАДАНИЕ НА ПРОЕКТИРОВАНИЕ

На вход устройства подается код X{1:16}. Спроектировать устройство, формирующее код Y{1:16}, количество нулей которого равно количеству единиц кода X. Все нули располагаются в младших разрядах кода Y. Остальные разряды кода Y заполняются единицами.

Примем, что источник входного кода гарантирует правильность выставленной информации во время действия стробирующего импульса СТРОБ, а само устройство подтверждает выдачу выходного кода генерацией импульса считывания УiИТ.

Синхронизацию выберем внешнюю с частотой ГТИ - 5 МГц.

Будем считать, что смена кодов X и Y осуществляется по положительному фронту ГТИ, длительность импульсов СТРОБ и УiИТ равна периоду тактовой последовательности и положительные фронты этих импульсов появляются вслед за положительным фронтом импульсов ГТИ.

Примем, что в разрабатываемом устройстве не требуется внутренняя индикация, и не будем накладывать ограничений на потребляемую мощность.

2. КОМБИНАЦИОННАЯ РЕАЛИЗАЦИЯ УСТРОЙСТВА.

При построении устройства в виде комбинационной схемы надо решить задачу синтеза системы шестнадцати логических функций 16 переменных. Решение задачи с использованием логических элементов приведет к очень объемной реализации. В связи с этим рассмотрим два варианта решения: с использованием ПЗУ для записи значений искомых логических функций или с позиций операционного синтеза, построив устройство, реализующее цепочку простых преобразований.

2.1. КОМБИНАЦИОННАЯ РЕАЛИЗАЦИЯ С ПЗУ.

В качестве ПЗУ будем использовать РПЗУ с ультрафиолетовым стиранием К573РФ7. Организация этих РПЗУ 32Кх8. Для реализации операционной части устройства потребуется 4 микросхемы К573РФ7 и одна микросхема К155ЛА3. Управляющая часть, формирующая сигнал УiИТ, будет представлять собой устройство задержки импульса СТРОБ на время, необходимое для выборки адреса. Такое устройство можно использовать в системах, в которых допустимое время формирования выходного кода не превышает 500 нс: действительно, задержка выходного кода t может быть вычислена по формуле:

t=t(РПЗУ)+t(CS)=t(K573РФ7)+t(К155ЛА3)=450+22=472 нс, где

t(РПЗУ) - время выборки адреса,

t(CS) - задержка формирования сигнала CS.

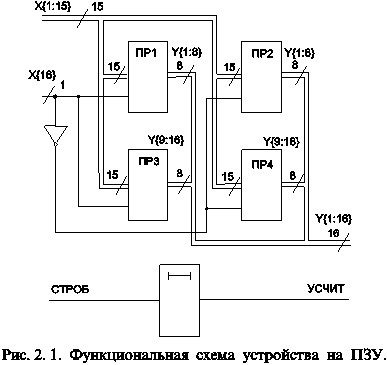

Функциональная схема устройства представлена на рис. 2.1.

Входной код Х{1:15} используется в качестве адреса и подается параллельно на все микросхемы РПЗУ (ПР1-ПР4). Разряд Х{16} используется для выбора пары микросхем (ПР1, ПР3 или ПР2, ПР4). Микросхемы ПР1, ПР2 хранят младшие 8 бит выходного кода (Y{1:8}), а ПР3, ПР4 - старшие (Y{9:16}). Сигнал УiИТ образуется путем задержки сигнала СТРОБ на максимально возможное время формирования выходного кода. Для частоты ГТИ в 5 МГц потребуется задержка на три такта.

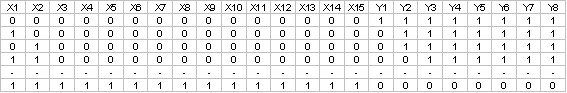

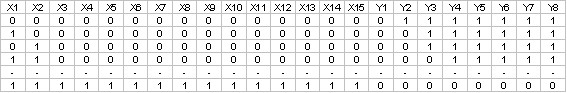

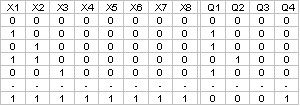

Программирование микросхем ПР1 - ПР4 будем проводить, соответственно, по таблицам 2.1 - 2.4.

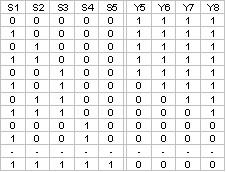

Таблица 2.1. Кодировка ПЗУ ПР1

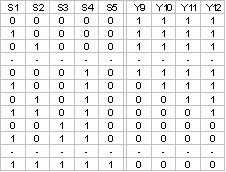

Таблица 2.2. Кодировка ПЗУ ПР2

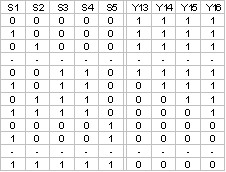

Таблица 2.3. Кодировка ПЗУ ПР3

Таблица 2.4. Кодировка ПЗУ ПР4

Управляющая часть устройства, представляющая собой схему задержки входного сигнала СТРОБ для получения сигнала УiИТ, реализована на основе двоичного счетчика, подсчитывающего число тактов задержки. Принципиальная схема управляющей части представлена на рис. 2. 2, а временная диаграмма работы - на рис. 2. 3.

На элементе DD1 (Рис. 2. 2) реализована схема формирования сигнала разрешения счета (РАЗР), а на DD3.1 - схема определения конца счета. Элемент DD3. 2 используется для получения заданной полярности выходного сигнала.

Принципиальная схема операционной части устройства, построенная на основе функциональной схемы рис. 2.1, изображена на рис. 2. 4.

Граф - схемы алгоритмов и графы переходов для этих схем не приводятся в связи с простотой реализации и будут представлены для регистровой реализации устройства.

2. 2. КОМБИНАЦИОННАЯ РЕАЛИЗАЦИЯ НА ОСНОВЕ ОПЕРАЦИОННОГО СИНТЕЗА.

Рассмотренное в предыдущем подразделе устройство при всей его простоте обладает двумя недостатками - большим временем формирования выходного кода и относительной дороговизной применяемых микросхем.

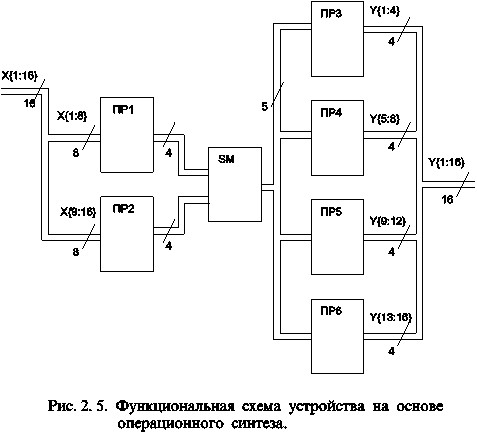

С позиций операционного синтеза функциональная схема устройства может представлять из себя набор из двух преобразователей входного кода в число содержащихся в нем единиц, сумматора, получающего число единиц во входном коде и преобразователя полученного числа в выходной позиционный код.

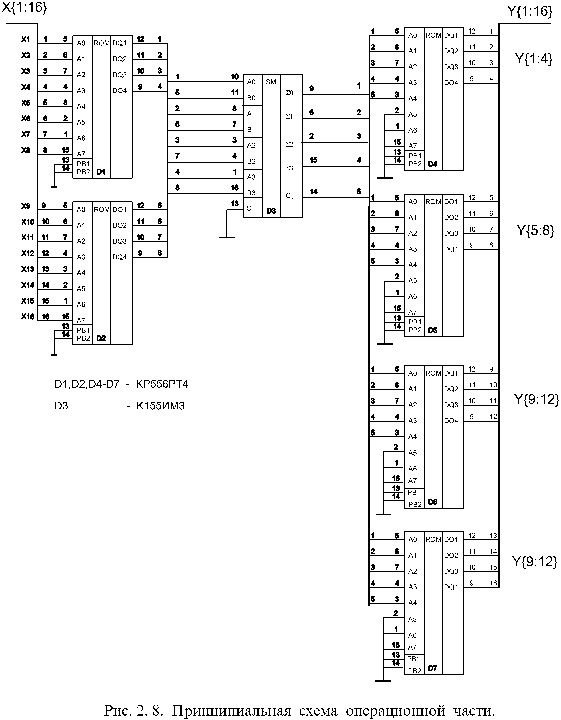

Функциональная схема устройства представлена на рис. 2. 5.

Разбив входной код на две части (разряды Х{1:8} и X{9:16}) можно использовать ППЗУ с организацией 256х4 бит (К556РТ4) для создания преобразователей тАЬкод-число едиництАЭ (ПР1, ПР2). Сумму будем формировать как выходной код сумматора и разряд переноса. Полученный 5 - разрядный двоичный код будем использовать для получения на преобразователе тАЬчисло - позиционный кодтАЭ (ПР3 - ПР6) выходного кода. Выбор 4 микросхем для этого преобразователя обусловлен разрядностью выходного кода.

Такое устройство можно использовать в системах, в которых допустимое время формирования выходного кода не превышает 200 нс: действительно, задержка выходного кода t может быть вычислена по формуле:

t=t(ППЗУ)+t(SM)+t(ППЗУ)=2*t(K556РТ4)+t(К155ИМ3)= =70+40+70=180 нс, где

t(ППЗУ) - задержка в ППЗУ, t(SM) - задержка сумматора.

Управляющая часть устройства, представляющая собой схему задержки входного сигнала СТРОБ для получения сигнала УiИТ, реализована по схеме, аналогичной предыдущей. Сигнал УiИТ образуется путем задержки сигнала СТРОБ на максимально возможное время формирования выходного кода. Для частоты ГТИ в 5 МГц потребуется задержка на один такт.

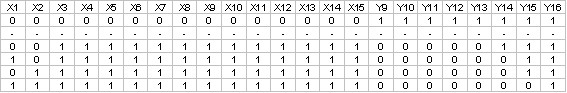

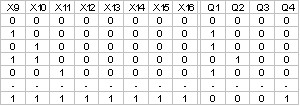

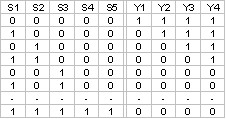

Программирование микросхем ПР1, ПР2 будем проводить, соответственно, по таблицам 2.5, 2.6, а ПР3-ПР6 - по таблицам 2.7 - 2.10.

Таблица 2.5. Кодировка ПЗУ ПР1 Таблица 2.6. Кодировка ПЗУ ПР2

Таблица 2.7. Кодировка ПЗУ ПР3

Таблица 2.8. Кодировка ПЗУ ПР4

Таблица 2.9. Кодировка ПЗУ ПР5

Таблица 2.10. Кодировка ПЗУ ПР6

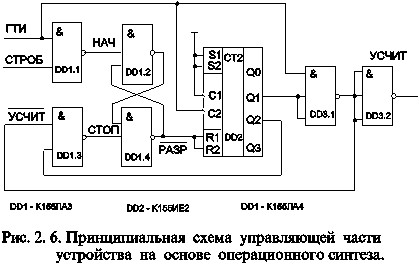

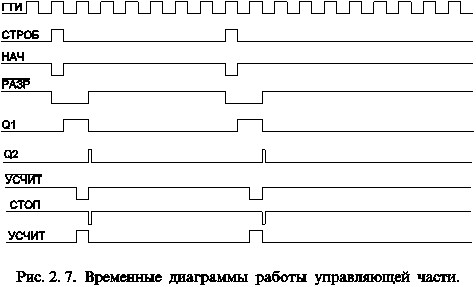

Принципиальная схема управляющей части представлена на рис. 2.6, а временная диаграмма работы - на рис. 2. 7.

На элементе DD1 (Рис. 2. 2) реализована схема формирования сигнала разрешения счета (РАЗР), а на DD3.1 - схема определения конца счета. Элемент DD3. 2 используется для получения заданной полярности выходного сигнала.

Принципиальная схема операционной части устройства, построенная на основе функциональной схемы рис. 2.5, изображена на рис. 2. 8.

Вместе с этим смотрят:

Вычитание в позиционных системах счисленияГазозарядные мониторыГенератор случайных чиселГибкие магнитные диски