Расчёт элементов эмиттерно-связанной логики

Министерство образования Украины Харьковский государственный технический университет радиоэлектроникиКУРСОВОЙ ПРОЕКТ

По курсу: ВлАналоговая и цифровая электроникаВ»

На тему: ВлРасчёт элемента эмиттерно-связанной логикиВ»

Выполнил: Руководитель проекта:

ст. гр. БТМАС 97-1 Борзенков Б.И.

Нагайченко М.В.

Харьков

1999

РЕФЕРАТКурсовой проект о расчёте ЭСЛ: 18 с., 5 рис., 1 приложение, 4 источника.

Объект разработки тАУ элемент эмиттерно-связанной логики.

Цель работы тАУ научиться применять полученные знания на практике.

Данный элемент эмиттерно-связанной логики (ЭСЛ) применяется в аппаратуре собранной на интегральных микросхемах, а также во всей области аппаратуры, которая использует для обработки сигналов двоичный код тАУ логический Вл0В» и Вл1В».

Данный элемент ЭСЛ потребляет намного меньше энергии, чем аналогичные элементы других типов.

Логический элемент ЭСЛ становиться всё более популярней, так как имеет высокую скорость обработки информации.

ЭМИТТЕРНО-СВЯЗАННАЯ ЛОГИКА, ИНТЕГРАЛЬНАЯ МИКРОСХЕМА, ЭМИТТЕРНО-ЭМИТТЕРНАЯ -СВЯЗАННАЯ ЛОГИКА,ПОЛУПРОВОДНИКОВАЯ ЦИФРОВАЯ СХЕМА, ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

СОДЕРЖАНИЕ Задание на курсовое проектирование 2 Реферат 3 Введение 5- Выбор схемы логического элемента ЭСЛ 6

- Расчетная часть 9

Выводы 16

Список используемых источников 17Приложение А 18

ВВЕДЕНИЕСхемы первых интегральных элементов были такие же, как при использовании дискретных компонентов. Однако очень скоро были обнаружены новые возможности интегральной техники, позволяющие создавать схемы с очень выгодными параметрами на совершенно новых принципах. Появились разнообразные ряды интегральных цифровых схем, из которых в настоящее время наиболее распространён ряд ТТЛ (транзисторно-транзисторные логические схемы), а для систем с большим быстродействием наиболее перспективен ряд ЭСЛ (логические схемы с эмиттерной связью).

Наиболее интенсивно развивались не только базовые интегральные схемы. Самые распространённые серии ЦИС дополнены в настоящее время различными интегральными субсистемами, например счётчиками, регистрами, дешифраторами, выпускаются интегральные полупроводниковые запоминающие устройства ёмкостью в несколько миллиардов бит и т.д.

В схемах ЭСЛ транзисторы работают вне области насыщения, поэтому автоматически исключается задержка, вызванная избыточными зарядами. Основным свойством и достоинством схем ЭСЛ является небольшая задержка, величина которой у самых последних типов составляет около 0.01 нс. Принцип действия схем ЭСЛ тАУ логических схем с эмиттерной связью тАУ заключается в переключении точно определённого тока малыми изменениями управляющего напряжения, порядка десятых вольта. Поэтому первоначально их называли переключателями тока и обозначали CML и CSL. Эти схемы были хорошо известны в системах на дискретных элементах, но в связи с большим числом необходимых транзисторов они нашли широкое применение только после внедрения интегральной техники. Последовательно были созданы серии: ЭСЛРЖ, ЭСЛРЖРЖ, ЭСЛРЖРЖРЖ и Э2СЛ (ЭЭСЛ).

С появлением транзистора в 1948 г. началась эпоха полупроводниковой цифровой техник, которая обусловила развитие самых разнообразных систем и устройств обработки информации. Где-то до 70-х годов в этих системах применялись полупроводниковые цифровые схемы на дискретных и пассивных элементах. Однако при использовании этих схем в больших и сложных системах возникли большие проблемы, касающиеся надёжности, экономичности и максимального быстродействия. Решить эти проблемы позволили новые открытия и производственные процессы в полупроводниковой технике, результатом которых явилась реализация интегральных схем.

- ВЫБОР СХЕМЫ ЛОГИЧЕСКОГО ЭЛЕМЕНТА ЭСЛ

Модификацию базового логического элемента ЭСЛ условно можно отнести к следующим группам:

- С улучшенными эксплуатационными характеристиками;

- С увеличенными логическими возможностями;

- Используемые в схемах средней и большой степени интеграции.

- На рисунке 1.1 приведена схема с повышенным напряжением статической помехоустойчивости

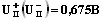

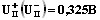

. Это достигается за счет увеличения логического перепада. Реализация последнего осуществляется включением эмиттерных повторителей на входе и выходе схемы ЭСЛ. В результате логический перепад в схеме увеличивается и становится равным

. Это достигается за счет увеличения логического перепада. Реализация последнего осуществляется включением эмиттерных повторителей на входе и выходе схемы ЭСЛ. В результате логический перепад в схеме увеличивается и становится равным  , в то время как в схеме базового логического элемента ЭСЛ он составит

, в то время как в схеме базового логического элемента ЭСЛ он составит  . В этой же схеме величина

. В этой же схеме величина  , а в схеме базового логического элемента

, а в схеме базового логического элемента  .

.

Находит применение также элемент Э2СЛ (эмиттерно-эмиттерно-связанная логика), являющаяся частью элемент, показанного на рисунке 1.1 с выходами y4 и y3 (без выходных эмиттерных повторителей на транзисторах VT7, VT8). Указанная схема элемента имеет определённые преимущества по сравнению со схемой базового логического элемента: более высокое входное сопротивление и, следовательно, Краз; эквивалентная входная ёмкость почти в 2 раза меньше; меньше суммарная ёмкость коллекторного узла и за счёт этого выше быстродействие.

Рисунок 1.1 тАУ Элемент Э2СЛ

- Для увеличения логических возможностей элемента ЭСЛ используют различные схемотехнические приёмы. На рисунке 1.2 выходы двух элементов (допускается больше двух выходов) объединены по прямым и инверсным выходам соответственно на нагрузочных резисторах. Для получения логической функции И-ИЛИ применяют схему с коллекторным объединением, рисунок 1.3. В этом случае прямые выходы двух элементов ЭСЛ объединяют на одной коллекторной нагрузке. Чтобы при этом из-за двойного тока не возросла вдвое амплитуда напряжения и, как следствие, транзисторы прямого плеча не оказались в режиме насыщения, предусмотрена специальная цепочка, отводящая избыточный ток и ограничивающая амплитуду напряжения.

Рисунок 1.2 - Схему с коллекторным объединением

Рисунок 1.3 - И-ИЛИ элемент

- Специфические требования схемотехники средней и большей степени интеграции ЭСЛ тАУ повышение быстродействия и снижение мощности потребления для составляющих элементов. Эти требования достаточно хорошо выполняются элементами МЭСЛ (малосигнальной эмиттерно-связанной логики). На рисунке 1.4 приведена схема элемента МЭСЛ. В такой схеме напряжение питания Uип=2.3 В. Напряжение логического перепада Uл=0.3.0.4 В; уровни напряжений U0=-IкRк; U1=-

Rк (Iк тАУ ток нагрузки).

Rк (Iк тАУ ток нагрузки).

Благодаря снижению напряжения питания и исключению эмиттерных повторителей мощность потребления этой схемой в 3.5 раз меньше, чем в базовом элементе ЭСЛ. Типовое значение средней задержки распространения составляет ![]() ; при мощности Р= мВт работа переключения Апер=5.10 пДж.

; при мощности Р= мВт работа переключения Апер=5.10 пДж.

Недостатком элемента МЭСЛ тАУ снижение помехоустойчивости и уменьшение коэффициента разветвления до Краз=4.5. Однако, несмотря на указанные недостатки, элемент МЭСЛ перспективен для использования в схемах БИС.

Рисунок 1.4 - схема элемента МЭСЛ

- РАiЕТНАЯ ЧАСТЬ

Для расчёта ЭСЛ воспользуемся параметрами, взятыми из части курсового проекта ВлЗАДАНИЕВ». Логика построения ЭСЛ тАУ положительная. Рисунок схемы ЭСЛ приведен в приложении А, эпюры напряжения входного сигнала приведены на рисунке 2.1.

Рисунок 2.1 тАУ Эпюра напряжения входного сигнала.

Принимаем падение напряжения на открытом p-n переходе транзисторов (в том числе транзистора нагрузки) диодов одинаковой, т.е. UбэТ=UбэТн=Uд=U*=0.7 В.

Расчет статических параметров.![]()

(Rк/Rэп)опт=0.2÷0.4, (2.1)

где Rк тАУ сопротивление коллектора,

Rэп тАУ сопротивление эмиттерного повторителя.

Выбираем из (2.1) 0,3 и преобразуя найдём:

Rэп=Rк/0,3 (2.2)

R4=(2÷4)Rк; R5=Rк; R8=R3=R6=R7;

и получим;

R3=Rэп; R4=3Rк; R5=Rк; R6=R7=Rэп; R8=Rэп. (2.3)

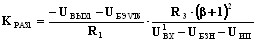

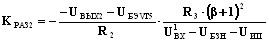

, (2.4)

, (2.4)

где Краз тАУ коэффициент разделения по входу;

Uоп тАУ среднее значение между уровнями Вл1В» и Вл0В», равный тАУ1.2 В

и по известным значениям определяем Rк:

![]()

![]()

подставляем в (2.2) и получим:

![]()

R1=708 Ом R3=2360 Ом R5=708 Ом R7=2360 Ом

R2=708 Ом R4=2124 Ом R6=2360 Ом R8=2360 Ом Rб=50 кОм

![]() , (2.5)

, (2.5)

определяем входной ток логической единицы (через каждый открытый эмиттерный переход): ![]()

![]() , (2.6)

, (2.6)

Определить ток логического Вл0В» определяемый сопротивлением Rб в цепи базы закрытого транзистора.

![]()

![]() , (2.7)

, (2.7)

определяем напряжение порога переключения:

![]()

![]() , (2.8)

, (2.8)

определяем ширину активной зоны:

![]()

![]() , (2.9)

, (2.9)

определяем логический перепад:

![]()

![]()

![]() , (2.10)

, (2.10)

определяем напряжение статической помехоустойчивости по уровню тАЬ0тАЭ и тАЬ1тАЭ.

![]()

![]() , (2.11)

, (2.11)

определяем ток логической части элемента :![]()

![]() (2.12)

(2.12)

и

![]() , (2.13)

, (2.13)

определяем точки эмиттерных повторителей:

![]()

![]()

![]() (2.14)

(2.14)

и

![]() , (2.15)

, (2.15)

определяем ток источника опорного напряжения:

![]()

![]()

![]() , (2.16)

, (2.16)

определяем общий ток, потребляемый элементом в состоянии тАЬ0тАЭ и (тАЬ1тАЭ):

![]()

![]() , (2.17)

, (2.17)

определяем мощность потребляемым логической частью элемента:

![]()

![]()

![]() , (2.18)

, (2.18)

определяем мощность эмиттерных повторителей:

![]()

![]() , (2.19)

, (2.19)

определяем мощность потребляемую источником опорного напряжения:

![]()

![]()

, (2.20)

, (2.20)

, (2.21)

, (2.21)

определяем и :

![]()

![]()

![]() , (2.22)

, (2.22)

определяем входное сопротивление элемента, когда на входе действует напряжение логического тАЬ0тАЭ:![]()

![]() , (2.23)

, (2.23)

определяем входное сопротивление элемента, когда на его входе действует напряжение логической тАЬ1тАЭ:![]()

![]() , (2.24)

, (2.24)

определяем входное сопротивление элемента, когда на выходе действует напряжение логического тАЬ0тАЭ:![]()

Расчёт динамических параметров

![]() , (2.25)

, (2.25)

где fT тАУ граничная частота усиления транзистора.

При fT=11 МГц определяем:

![]()

![]() , (2.26)

, (2.26)

и

![]() , (2.27)

, (2.27)

где М тАУ количество транзисторов в схеме VT1÷VT3, VT6; Ск - ёмкость коллекторных переходов транзисторов; Сп1 тАУ паразитная ёмкость металлических соединений и изоляции транзисторов и резистора R1; С2 тАУ ёмкость на выходе транзистора VT6; В тАУ статическое значение коэффициента усиления транзистора VT6; Сн тАУ ёмкость нагрузки; Сп2 тАУ паразитная ёмкость изоляции резистора R6 и металлических соединений подключенных к выходу схемы.

При М=4, Ск=2 пФ, Сп1= 1 пФ, Сн=30 пФ, Сп2= 2 пФ.

![]()

![]()

![]() , (2.28)

, (2.28)

![]()

![]() , (2.29)

, (2.29)

![]()

![]() , (2.30)

, (2.30)

определяем время спада:![]()

![]() , (2.31)

, (2.31)

определяем время наростания потениала:![]()

![]() , (2.32)

, (2.32)

определяем задержку при включении:![]()

![]() , (2.33)

, (2.33)

определяем задержку при выключении:![]()

![]() , (2.34)

, (2.34)

определяем среднюю задержку распространения:

![]()

![]() , (2.35)

, (2.35)

определяем время перехода из состояния тАЬ1тАЭ в состояние тАЬ0тАЭ:![]()

![]()

![]() , (2.36)

, (2.36)

определяем время перехода из состояния тАЬ0тАЭ в состояние тАЬ2тАЭ:![]()

![]() , (2.37)

, (2.37)

![]()

![]() , (2.38)

, (2.38)

найдем работу переключения: ![]()

Целью данного курсового проекта являлась разработка логического элемента эмиттерно-связанной логики. В выборе схемы логического элемента был произведен краткий обзор существующих схем серий ЭСЛ.

По заданным данным определил основные статические характеристики разрабатываемой схемы. Расчет показал, что средняя потребляемая мощность не превышает заданного значения. В этом же разделе определил номинальные значения резисторов и конденсаторов, используемых в схеме. Это позволило рассчитать динамические параметры схемы ЭСЛ.

СПИСОК ИСПОЛЬЗУЕМЫХ ИСТОЧНИКОВ- Соломатин Н.М. Логические элементы ЭВМ: Практ. пособие для вузов, 2-е изд., перераб. И доп. тАУ М .: Высш. шк., 1990.-160с.

- Ушаков В.Н. Основы радиоэлектрники и радиотехнические устройства. Учеб. Пособие для радиотехнических вузов., - М.: Высш. шк., 1976.-424с.

- Будинский И.В. Логические цепи в цифровой электронике. тАУ М.: Высш. шк., 1977.-323с.

- ДСТУ 3008-95. тАУ Видання офiцiйне

Вместе с этим смотрят:

Реверсная магнитная фокусирующая система мощного многолучевого клистронаРемонт и обслуживание СВЧ-печей

Рождение телевидения

Рубиновый оптический квантовый генератор