Триггеры

ТРИГГЕРЫ

1. Общие сведения

Устройство, имеющее два устойчивых состояния, называют триггером. Он имеет два выхода, один из них называют прямым, а другой тАФ инверсным. Потенциалы на них взаимно инвертированы: лог. 1 на одном выходе соответствует лог. 0 на другом. С прихоВндом переключающих (запускающих) сигналов переход триггера из одного состояния в другое происходит лавинообразно, и потенВнциалы на выходах меняются на противоположные.

В интервале между переключающими сигналами состояние триггера не меняется, т. е. триггер "запоминает" поступление сигнаВнлов, отражая это величиной потенциала на выходе. Это дает возможность использовать его как элемент памяти.

При лавинообразных переключениях на выходе триггера формируются прямоугольные импульсы с крутыми фронтами. Это поВнзволяет использовать триггер для формирования прямоугольных импульсов из напряжения другой формы (например, из синусоиВндального).

При двух последовательных переключениях триггера на выходе формируется один импульс, т.е. триггер можно использовать как делитель частоты переключающих сигналов с коэффициентом, равным двум.

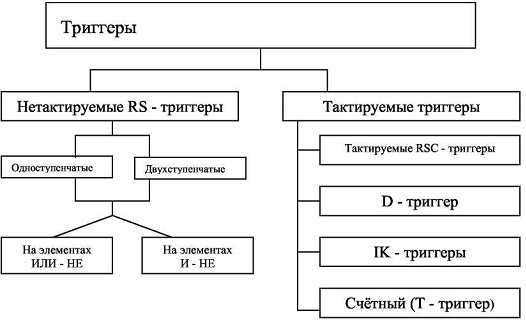

Триггеры можно разделить на не тактируемые и тактируемые. Не тактируемый (асинхронный) триггер может менять свое состояние

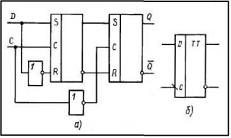

Рис.1

переключающими сигВнналами в любое время. ТакВнтируемый (синхронный) триггер переключается синВнхронно с поступлением спеВнциального тактирующего импульса. Эти и другие тиВнпы триггеров, показанные в таблице классификации, подробно рассмотрены даВнлее.

Промышленность выпусВнкает разнообразные типы триггеров в интегральном исполнении. Кроме того, они могут быть выполнены на цифровых интегральных микросхемах, операционных усилителях и на транзистоВнрах. Рис.1.

2. Не тактируемые триггеры

На выходе элемента И-НЕ (ИЛИ-НЕ) имеется инвертор (усилитель). В структуре из двух таких элементов можно обеспечить поВнложительную обратную связь, если вход одного элемента соединить с выходом другого, и баланс амплитуд. Такой структурой явВнляется RS-триггер. Он имеет два выхода: прямой ( ) и инверсный (

) и инверсный ( ) и два входа: S тАФ установки прямого выхода в 1 (говорят: "установки триггера в 1") и R тАФ установки триггера в 0. Такой триггер является асинхронным RS-триггером. Он применяется самоВнстоятельно, а также в качестве запоминающей ячейки входит в состав более сложных интегральных триггеров.

) и два входа: S тАФ установки прямого выхода в 1 (говорят: "установки триггера в 1") и R тАФ установки триггера в 0. Такой триггер является асинхронным RS-триггером. Он применяется самоВнстоятельно, а также в качестве запоминающей ячейки входит в состав более сложных интегральных триггеров.

2.1. Структуры триггеров

RS-триггер на элементах ИЛИ-НЕ (рис. 2,а). Прежде всего рассмотрим воздейВнствие на такой триггер комбинаций сигналов S=1, R=1 и S=0, R=0. Сочетание S=1, R=1 является запрещенным, так как при нем на обоих выходах триггера устанавлиВнваются логические 0 и после снятия входных сигналов состояние его неВнпредсказуемо.

Для элемента ИЛИ-НЕ логический 0 является пассивным сигналом: с его поступВнлением на вход состояние выхода элемента не изменяется. Поэтому появление комВнбинации S=0, R=0 не изменяет состояния триггера.

Логическая 1 для элемента ИЛИ-НЕ является активным сигналом: наличие ее на входе элемента однозначно определяет на его выходе логический 0 вне зависимости от сигнала на другом входе. Отсюда следует, что переключающим сигналом для рассматриваемого триггера является логическая 1, а также то, что вход S (установки триггера в состояние Q=1) должен быть связан с элементом, выход которого принят за  .

.

Из сказанного ясно, что для переключения триггера в состояние Q=1 на его входы следует подать комбинацию S=1, R=0, а для переключения в состояние Q=0 тАФ комбинацию S=0,R=1.

Пусть триггер (рис. 2,а) находится в состоянии 0 (Q=0,  =1), а на входах действуют сигналы S=0, R=0. Для его переключения в состояние Q=1 подадим на входы комбинацию о S=1, R=0. Тогда на выходе элемента Э2 установится логический 0, на входах элемента Э1 будут одновременно присутствовать, логические 0, и на выходе Q установится логическая 1 тАФ триггер переключается в новое состояние (Q=1,

=1), а на входах действуют сигналы S=0, R=0. Для его переключения в состояние Q=1 подадим на входы комбинацию о S=1, R=0. Тогда на выходе элемента Э2 установится логический 0, на входах элемента Э1 будут одновременно присутствовать, логические 0, и на выходе Q установится логическая 1 тАФ триггер переключается в новое состояние (Q=1,  =0). Для его переключения из этого состояния на входы должна поступить комбинация S=0, R=1. После этого на выходе Q будет логический 0, на входах элемента Э2 одновременно окажутся логические 0 и его выход примет потенциал, соответствующий

=0). Для его переключения из этого состояния на входы должна поступить комбинация S=0, R=1. После этого на выходе Q будет логический 0, на входах элемента Э2 одновременно окажутся логические 0 и его выход примет потенциал, соответствующий  =1, тАФтриггер переключается в состояние Q=0,

=1, тАФтриггер переключается в состояние Q=0,  =1.

=1.

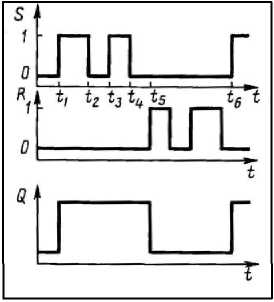

Рис.3.

Из изложенного следует, что время переключения триггера (tпер) равно удвоенному времени переключения логического элеменВнта (удвоенному времени задержки тАФ 2tз). Часто, предусматривая запас, принимают tпер=3tз. Для надежного переключения триггера длительность входного переключающего сигнала не должна быть меньше tпер. Условное изображение RS-триггера приведено на рис. 2,б. На рис.3 приведена идеализированная временная диаграмма RS-триггера, на которой время переключения триггера принято равным нулю. ПредполаВнгается, что до момента t1 S=0, R=0, а триггер находится в состоянии Q=0. В момент t1 комбинация S=1, R=0 переВнключает триггер в состояние Q=1. При t=t2 на входах устаВннавливается сочетание S=0, R=0, при котором состояние триггера сохраняется прежним. Комбинация S=1, R=0, появляющаяся в момент t3, и комбинация S=0, R=0 в момент t4 никаких изменений не вносят, по-прежнему Q=1. Только в момент t5 сочетание S=0, R=1 вызывает переключение триггера в состояние Q=0. Вслед за этим изменение логической переменной на входе R состояВнния триггера не меняет. Новое переключение происходит в момент t6 при поступлении на входы комбинации S=1, R=0. Заметим, что запрещенное сочетание сигналов S=1, R=1 на диаграмме отсутствует.

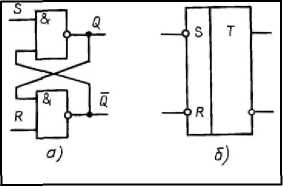

Рис.4.

RS -триггер на элементах И-НЕ (рис. 4,а). Для элемента И-НЕ активным сигналом является логический 0: наличие его хотя бы на одном входе обусловливает на выходе логическую 1 независимо от сигналов на других входах. Логическая 1 для такого элеменВнта является пассивным сигналом: с ее поступлением на вход состояние выхода элемента не изменяется. В силу сказанного триггер на элементах И-НЕ переключается логическим 0. На условном изображении такого триггера (рис. 4,б) это отражают инверсными входами.

Нетрудно понять, что для данного триггера комбинация входных сигналов S=0, R=0 является запрещенной, а комбинация S=1, R=1 не меняет его предыдущего состояния.

3 Тактируемые триггеры

На входы логического элемента или устройства сигналы не всегда поступают одновременно, так как перед этим они могут проВнходить через разное число элементов, не обладающих к тому же одинаковой задержкой. Это явление описывают как состязания или гонки сигналов. В результате в течение некоторого времени на входах создается непредвиденная ситуация: новые значения одВнних сигналов сочетаются с предыдущими значениями других, что может привести к ложному срабатыванию элемента (устройства). Последствия гонок можно устранить временным стробированием, когда на элемент, кроме информационных сигналов, подаются тактирующие (синхронизирующие) импульсы, к моменту прихода которых информационные сигналы заведомо успевают устаноВнвиться на входах.

Тактируемый триггер, кроме информационных входов, имеет синхронизирующий (тактирующий, тактовый) вход; сигналы на информационных входах воздействуют на такой триггер только с поступлением сигнала на синхронизирующий вход.

3.1. Структуры триггеров

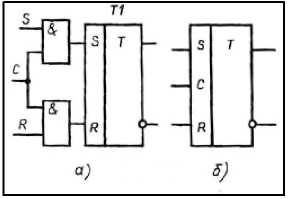

Рис.5.

Тактируемый RS-триггер (рис.5,а). Схема такого триггера (собранного на элементах ИЛИ-НЕ) содержит асинхронный RS-триггер T1 и два конъюнктура входной логики. Последние передают переключающую логическую 1 с информационного S- или R-входа на соответстВнвующие входы Т1 только при наличии на синхронизирующем входе С логической 1. При С=0 информация с S- и R-входов на триггер Т1 не передается.

Рассматриваемый триггер может быть выполнен и на запоминающей ячейке, реализованВнной на элементах И-НЕ.

Условное изображение тактируемого триггера приведено на рис. 5,б. В тексте тактируеВнмый RS-триггер сокращенно обозначают как RSC-триггер.

Синхронизирующие входы триггера могут быть статическими и динамическими. СтатичеВнский вход не теряет своего управляющего действия, пока на нем присутствует тактовый (синхро) импульс. Такие входы имеет триггер, изображенный на рис. 5,а. В присутствии тактового импульса эти триггеры будут менять свое состояние при каждой смене комбинаций логических потенциалов на входах S и R. Динамический синхровход воздействует на состояние выходов тригВнгера в момент своего появления (передним фронтом) или окончания (задним фронтом).

Рис.6.

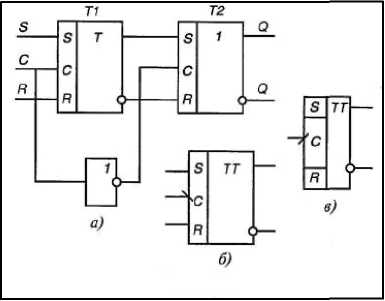

Двухступенчатый тактируемый RS-триггер (рис.6,а). Каждая ступень такого триггера представляет собой тактируемый RS-триггер. При появлении на входе С логической 1 триггер Т1 воспринимает информацию на входах S и R, определяюВнщую его состояние. В это время на С-входе триггера Т2 за счет инвертора тАФ логический 0, и информация с выходов Т1 не воздействует на Т2. В момент оконВнчания действия логической 1 на входе С (С=0) на выходе инвертора появляется логическая 1, разрешающая перезапись в Т2 информации из Т1. Таким образом, в первую ступень информация с входов S и R записывается с поступлением тактоВнвого импульса, т. е. по его переднему фронту; состояние первой ступени передаВнется второй с окончанием тактового импульса, т. е. по его срезу. По этому внешВннему проявлению тактирующего импульса C-вход описанного триггера можно рассматривать как динамический.

Условное изображение двухступенчатого RS-триггера, в котором переключение выходов второй ступени триггера происходит перепадом входного сигнала из 1 в 0 (перепадом 1 / 0), приведено на рис.6,б. Условное изображение триггера с C-входом, переключающим триггер перепадом 0/1, приведено на рис. 6, в.

Тактируемый (синхронный) триггер обычно имеет дополнительные асинхронные входы, но которым он вне зависимости от сигВннала на тактовом входе переключается в состояние 1 (по входу S) или в 0 (по входу R). Такие входы называют не тактируемыми или асинхронными. Логические потенциалы на них воздействуют на запоминающие ячейки триггера непосредственно (для чего эти ячейки триггера выполнены на трехвходовых элементах), минуя входную логику.

Условное изображение двухступенчатого триггера с инверсными асинхронными входами приведено на рис. 7.

Рис.8.

Рис.7.

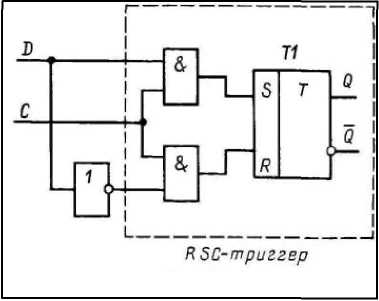

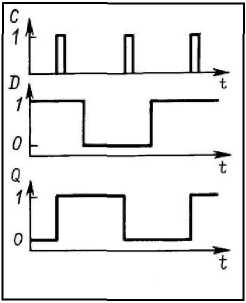

D -триггер (триггер задержки) тАУ рис. 8 . D-триггер имеет один информационный D-вход и тактовый С-вход. Он состоит из синхронного RSC-триггера, дополненного инвертором. При С=1 потенциал D-входа передается на S-вход триггера T1 (S=D), а на входе R устанавливается потенциал R= : сигналы на входах оказываются взаимно инвертированными. Это приводит к тому, что любой сигнал на входе D создает на S- и R-входах комбинацию (S=1, R=0 или S=0, R=1), способную переключить триггер в состояние Q=S=D. Таким образом, при С=1 D-триггер является повторителем: на выходе Q повторяется потенциал входа D. Однако это повторение начинается только с поступлением тактового импульса на вход С, т. е. с задержкой относительно сменившегося потенциала на D-входе. При С=0 триггер Т1 и D-вход разобщены, поэтому S=0 и триггер хранит информацию, поступившую с D-входа при С = 1. Так как в D - триггере информация поступает по одной линии тАУ на D-вход, то явление гонок не проявляется. Поэтому в быстродействующих цифровых устройствах используют D-триггеры.

: сигналы на входах оказываются взаимно инвертированными. Это приводит к тому, что любой сигнал на входе D создает на S- и R-входах комбинацию (S=1, R=0 или S=0, R=1), способную переключить триггер в состояние Q=S=D. Таким образом, при С=1 D-триггер является повторителем: на выходе Q повторяется потенциал входа D. Однако это повторение начинается только с поступлением тактового импульса на вход С, т. е. с задержкой относительно сменившегося потенциала на D-входе. При С=0 триггер Т1 и D-вход разобщены, поэтому S=0 и триггер хранит информацию, поступившую с D-входа при С = 1. Так как в D - триггере информация поступает по одной линии тАУ на D-вход, то явление гонок не проявляется. Поэтому в быстродействующих цифровых устройствах используют D-триггеры.

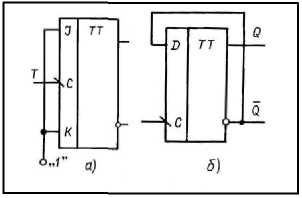

Рис.9.

На рис.9 приведены временные диаграммы D-триггера. Выход Q повторяет состояние D-входа с поступлением очередного тактового импульса на вход С, т. е. с задержкой.

D-триггер можно выполнить двухступенчатым. При этом его первая ступень представляет собой одноступенчатый D-триггер, а вторая может быть синхронным RSC-триггером (рис. 10,а). Состояние D-входа передается первой ступени с приходом тактового импульса, т. е. по его переднему фронту; вторая ступень (триггер в целом) принимает состояние первой с окончанием тактового импульса, т. е. по его заднему фронту. Условное изображение двухтактного D-триггера, переключающегося перепадом 1/ 0 приведено на рис. 10,б.

JK - триггер. Такой триггер имеет информационные входы J и К, которые по своему влиянию аналогичны входам S и R тактируемого RSС-триггера: при J=1, K=0 триггер по тактовому импульсу устанавливается в состояние Q=1; при J= 0, К=1тАУ переключается в состояние Q=0, а при J = K= 0 тАУ хранит ранее принятую информацию. Но в отличие от RSС-триггера одновременное присутствие логических 1 на информационных входах не является для JK-триггера запрещенной комбинацией.

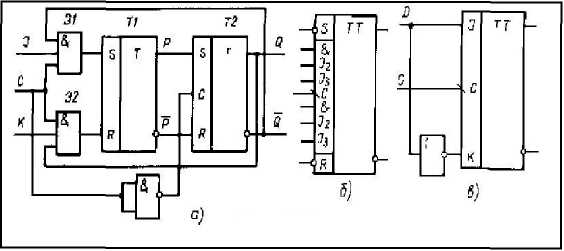

Рис.11.

На рис. 6.11,а изображена одна из функциональных схем JK-триггера. Ее отличительной особенностью являются пеВнрекрестные связи выходов триггера с входами конъюнкторов входной логики. Благодаря им на эти входы после кажВндого переключения триггера передаются потенциалы, обВнратные тем, какие были перед предыдущим переключениВнем, и которые поэтому в состоянии обеспечить новое переВнключение триггера в противоположное состояние.

Для создания информационных входов J и K элементы Э1 и Э2 входной логики первой ступени выбраны трехвходовыми. Переключение выходов второй ступени триггера происходит перепадом 1/0 на C-входе.

При J=K=0 на входах элементов Э1 и Э2 устанавливаются логические 0, которые для триггеров с прямыми входами являются пассивными сигналами - триггер Т1 и, следовательно, JK-триггер в целом сохраняют прежнее состояние. Чтобы на выходе элемента Э1 появилась логическая 1 (которой триггер Т1 может переключаться в состояние Р= 1), на его входах необходимо присутствие сигналов J =1, С=1, а также логической 1 с выхода  . Аналогично, логическая 1 будет на выходе элемента Э2, когда K=1, С=1 и Q=1. Таким образом, комбинация J=1, К=0 обеспечивает по тактовому импульсу переключение JK-триггера в целом в состояние Q=1, а комбинация J=0, K=1тАФ в состояние Q=0.

. Аналогично, логическая 1 будет на выходе элемента Э2, когда K=1, С=1 и Q=1. Таким образом, комбинация J=1, К=0 обеспечивает по тактовому импульсу переключение JK-триггера в целом в состояние Q=1, а комбинация J=0, K=1тАФ в состояние Q=0.

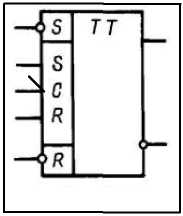

На рис.11,б приведено изображение JK- триггера с тремя объединенными конъюнкцией входами J, с тремя объединенными конъюнкцией входами K и с входами S и R асинхронной установки. На рис. 11,в показана реализация D-триггера на базе JK-триггера.

Рис.12.

4. Счетные триггеры

Счетный триггер (Т-триггер) отличается тем, что он переключается с поступлением каждоВнго импульса на тактовом входе, называемом в таком триггере счетным. Счетный триггер можно реализовать на базе JK-триггера. Логическая 1 на одном из входов элемента И не опВнределяет потенциал на его выходе, поэтому сочетание J=K=1 не влияет на входную логику первой ступени триггера. Теперь она получает информацию только с выходов триггера (рис.11,а), которая устанавливает ее в положение, когда с приходом счетного импульса начнется очередное переключение - JK-триггер работает в счетном режиме. Реализация счетного режима на JK- триггере приведена на рис 12,а.

Счетный триггер просто реализуется и на D-триггере (рис. 12, б). Если после каждого переключения обеспечить автоматическую смену уровня потенциала на D-входе, то с каждым импульсом на C-входе триггер будет менять свое состояние. Указанная смена потенциала будет осуществляться, если D-вход соединить с выходом  . Вторая перекреВнстная связь (аналогичная связи в JK- триггере) обеспечивается за счет соединения D-входа с R-входом запоминающей ячейки тригВнгера через инвертор (см.рис.8).

. Вторая перекреВнстная связь (аналогичная связи в JK- триггере) обеспечивается за счет соединения D-входа с R-входом запоминающей ячейки тригВнгера через инвертор (см.рис.8).

5. Триггер Шмитта

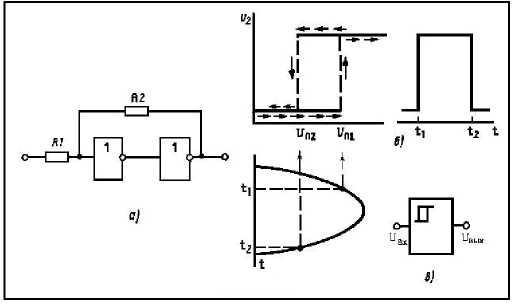

Рис.13.

Этот триггер (рис. 13,a) стоит особняком в семействе триггеВнров: он имеет один вход, один выход и не обладает свойствами заВнпоминающего элемента. Триггер содержит два инвертора, охваВнченных положительной обратной связью, за счет чего выход схеВнмы может изменять свое состояние лавинообразно.

На выходе инвертора потенциал с лог. 0 на лог. 1 изменяется при большем входном напряжении, чем при изменении с лог.1 на лог. 0. Поэтому схема (рис.13,а) обладает гистерезисом (рис. 13,б). Это позволяет использовать ее в качестве формироВнвателя прямоугольных импульсов из входного напряжения, в чаВнстности, из синусоидального.

Условное изображение триггера Шмитта приведено на рис. 13,в.

Литература

- Калабеков Б.А. Цифровые устройства и микропроцессорные системы тАФМ.: Телеком, 2000г.

- Потемкин И.С. Функциональные узлы цифровой автоматики тАФМ.: Энергоатомиздат, 1988 г., c. 166тАж. 206.

- Сайт в интернете: " onclick="return false">

- Сайты в интернете : rff.tsu.ru, pub. mirea. ac. ru, foroff. phys. msu.ru

Вместе с этим смотрят:

Туннелирование в микроэлектроникеУниверсальный блок питанияУправление ДПЛА через ретрансляторУправление тюнером спутникового телевидения