Электронное устройство счета и сортировки

Министерство Российской Федерации по атомной энергии

Северский технологический институт

Томского политехнического университета

Кафедра ЭиАФУ

Электронное устройство счета и сортировки

Пояснительная записка

ЭУ.200.600. ПЗ

Руководитель: Соловьёв Ю.А.

Вл___В»_____________200_г.

Студент: Пономарёв В.В.

Вл___В»_____________200_г.

Северск 2002г.

Задание на курсовое проектирование студенту Пономарёву В.В.

1. Тема проекта: Сортировочное устройство, вариант №24

2. Срок сдачи студентом законченного проекта 20.12.2002г.

3. Исходные данные к проекту.

3.1. Устройство питается от однофазной промышленной сети переменного тока 220 В, частотой 50 Гц.

3.2. Устройство должно обеспечивать работу при отклонениях напряжения питающей сети от номинального в пределах от плюс 10 до минус 15 %.

3.3. Устройство предназначено для работы в закрытых стационарных помещениях при температуре окружающего воздуха в пределах от плюс 5 до плюс 40 °С.

3.4. Устройство должно производить сортировку предметов по трем параметрам Х1, Х2, Х3 в соответствии с программой, заданной в таблице 1.

Таблица 1.Программа сортировки

Номер набора

|

Х1

|

Х2

|

Х3

|

Y

|

0

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

1

|

0

|

2

|

0

|

1

|

0

|

0

|

3

|

0

|

1

|

1

|

1

|

4

|

1

|

0

|

0

|

1

|

5

|

1

|

0

|

1

|

0

|

6

|

1

|

1

|

0

|

1

|

7

|

1

|

1

|

1

|

0

|

3.5. Устройство должно производить счет и отображение числа отсортированных предметов до значения N= 789

3.6. Параметры пороговых значений входных сигналов ФЛУ и точность сравнения приведены в таблице 2.

Таблица 2.Исходные данные.

Номер варианта

|

Uд1min

|

Uд1max

|

Uд2min

|

Uд2max

|

Uд3min

|

Uд3max

|

Uср

|

24

|

3,8

|

9,3

|

5,6

|

8,7

|

5,8

|

7,3

|

0,01

|

3.7.Длительность сигналов управления исполнительными механизмами: ПДимп1=19 (мс), ПДимп2=19 (мс).

3.8.Принципиальная схема должна обеспечить выполнение всех функций, перечисленных в п. 1.2 пособия.

Руководитель .А. Соловьёв тАЭ_______________200_г.

Задание принял к исполнению

Пономарёв В.В. тАЭ_______________200_г.

Содержание

1. Общие вопросы проектирования 5

1.1. Описание технологического процесса 5

1.2. Функции, выполняемые сортировочным устройством. 5

1.3. Обоснование выбора блочной схемы СУ. 6

2. Разработка формирователей логических уровней (ФЛУ). 8

2.1. Разработка принципиальной схемы ФЛУ. 8

2.2. Выбор типа компаратора. 11

2.3. Расчет параметров элементов принципиальной схемы. 12

2.4. Определение мощности и тока, потребляемых ФЛУ. 16

3. Проектирование цифрового автомата. 18

3.1. Минимизация логической функции автомата. 18

3.2. Разработка принципиальной схемы автомата. 19

3.3. Определение мощности и тока, потребляемых цифровым автоматом. 20

4. Разработка двоично-десятичного счетчика. 21

4.1. Обоснование и выбор типа интегральной микросхемы двоично-десятичного счетчика. 21

4.2. Проектирование счетчика предметов на заданное число. 21

4.3. Разработка дешифратора конца счета. 22

4.4. Разработка схемы установки счетчика в исходное (нулевое) состояние 23

4.5. Определение мощности и тока, потребляемых счетчиком. 24

5. Проектирование схемы индикации в десятичной форме. 26

5.1. Выбор типа дешифраторов и семисегментных индикаторов. 26

5.2. Разработка принципиальной схемы индикации. 27

5.3. Расчет мощности и тока, потребляемых схемой индикации. 28

6. Проектирование схем управления исполнительными механизмами. 29

6.1. Выбор типа интегральной микросхемы ждущего мультивибратора. 29

6.2. Расчет параметров элементов времязадающих цепей 29

6.3. Расчет мощности и тока, потребляемых схемой. 30

7. Разработка источника питания. 31

7.1. Определение исходных данных (количество источников напряжения, требуемые величины напряжений и токов нагрузки). 31

7.2. Выбор схемы выпрямления и типа диодов. 31

7.3. Расчет и выбор параметров схемы сглаживания пульсаций. 32

7.4. Разработка принципиальной схемы стабилизаторов, расчет параметров схемы и выбор типа применяемых элементов. 33

8. Разработка и описание принципиальной схемы сортировочного устройства. 34

9. Заключение. 35

10. Список литературы. 36

Приложение 1 37

Введение

Быстрое расширение областей применения электронных устройств одна из особенностей современного научно тАУ технического прогресса. Этот процесс связан с внедрением интегральных микросхем в управляющие устройства. Применение интегральных микросхем позволило усовершенствовать и создать новые методы проектирования, конструктирования и производства радиоэлектронной аппаратуры различного назначения. Использование цифровой микроэлектроники в различных областях значительно упростило контроль за различными процессами и повысило качество выпускаемых изделий.

-

Общие вопросы проектирования

-

Описание технологического процесса

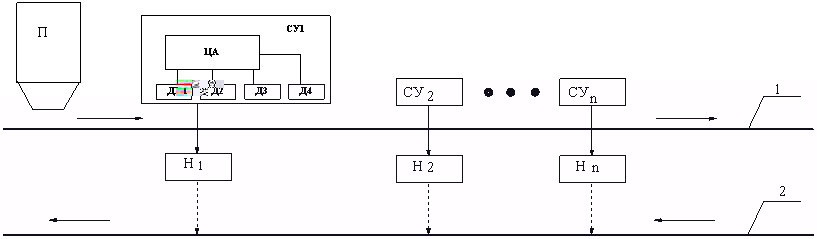

Рассмотрим технологический процесс сортировки некоторых предметов (изделий), представленный на рисунке 1.

Рисунок 1. Технологическая схема сортировки предметов

Изготовленные предметы из питателя П поступают на транспортную систему 1 и автоматически распределяются (сортируются) по накопителям Н1 тАУ Нn. Управление осуществляется с помощью сортировочных устройств СУ1 тАУ СУn, измеряющих некоторые параметры предметов и вырабатывающих сигнал управления на складирование в накопитель Н при совпадении набора определенных значений параметров предметов с заданным. При достижении количества отсортированных предметов заданному числу контейнер с отсортированными предметами удаляется с помощью другой транспортной системы 2, обеспечивая непрерывность процесса.

Разработаем и рассчитаем основные элементы системы управления сортировочного устройства.

Функции, выполняемые сортировочным устройством.

Количественная оценка каждого признака производится тремя аналоговыми датчиками (Д1 тАУ Д3), выходное напряжение которых имеет положительную полярность и изменяется от 0 до 10 В.

Так как одновременную оценку параметров трех признаков обеспечить технически сложно, то необходимо ввести позиционный (путевой) датчик Д4. Цифровой выходной сигнал датчика Д4. единичного уровня появляется тогда, когда аналоговые датчики Д1 тАУ Д3 закончили формирование своих выходных сигналов.

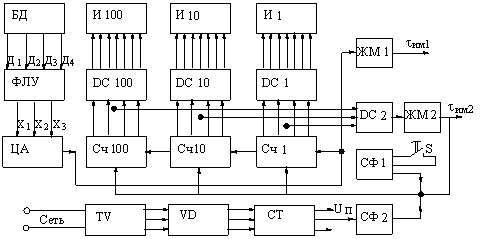

Числовая оценка параметра признака осуществляется в цифровой форме. Данный признак Х принимает единичное значение, если выходное напряжение соответствующего аналогового датчика находится в определенной зоне, задаваемой двумя пороговыми значениями UДmin и UДmax:

Программа сортировки задается определенной совокупностью цифровых наборов признаков Х1, Х2, Х3.

При совпадении текущего набора признаков с заданным по программе счетное устройство вырабатывает сигнал управления исполнительным механизмом (ИМ1) длительностью τим1, запускающий процесс складирования отсортированного предмета в накопитель Н1.

В процессе сортировки необходимо вести текущий счет и индикацию в десятичной форме числа отсортированных предметов.

При достижении заданного числа N отсортированных предметов в накопителе формируется сигнал определенной длительности τим2 управления исполнительным механизмом (ИМ2), для удаления контейнера с предметами из накопителя и замены на пустой. При этом счетчик должен автоматически тАЬобнулитьсятАЭ и начать счет отсортированных предметов в следующей партии.

Необходимо предусмотреть автоматическое тАЬобнулениетАЭ счетчика предметов при подаче напряжения питания на сортировочное устройство, а так же тАЬобнулениетАЭ по команде обслуживающего персонала (ручное управление).

Обоснование выбора блочной схемы СУ.

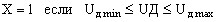

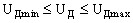

На рисунке 2 представлена блочная схема сортировочного устройства СУ, которая даёт наглядное представление о структуре СУ, его внутренних связях и работы.

Рисунок 2.Блочная схема СУ

Блок аналоговых датчиков (БД) производит измерение трех параметров предметов в аналоговой форме. Четвертый датчик Д4. выдает сигнал готовности процесса измерения в цифровой форме. Единичному выходному сигналу соответствует момент времени, когда все три признака блоком БД сформированы.

Процесс преобразования аналоговых сигналов измерения в цифровой вид (Х1, Х2, Х3) осуществляет блок формирователей логических уровней ФЛУ.

Цифровой (программный) автомат (ЦА) работает по жесткой программе, задаваемой таблицей истинности. При совпадении текущей совокупности измеренных параметров с заданной выдается выходной сигнал ЦА, используемый для счета и включения исполнительного механизма после формирования определенной длительности τим1 ждущим мультивибратором (ЖМ1). Счет количества отсортированных предметов ведется десятичными счетчиками Сч100 тАУ Сч1. Визуальная индикация числа предметов производится семисегментными индикаторами И100 тАУ И1 в десятичном виде. Для преобразования состояния счетчика (Сч) из двоичного кода в код, необходимый для управления индикаторами И100 тАУ И1, используются специальные дешифраторы DC100 тАУ DC1.

Дешифратор DC2 определяет момент достижения заданного количества отсортированных предметов. Ждущим мультивибратором ЖМ2 формируется сигнал управления длительностью τим2 вторым исполнительным механизмом и контейнер с предметами удаляется из накопителя. По этому же сигналу счетчик автоматически тАЬобнуляетсятАЭ. Установка счетчика Сч100 тАУ Сч1 в нулевое исходное состояние может быть произведена вручную оператором путем коммутации кнопки S. Сигнал установки счетчика в исходное состояние вырабатывается схемой формирования (i1).

Питание СУ производится от сети однофазного напряжения 220В, частотой 50Гц. С помощью понижающего трансформатора ТV получают источник тока с требуемым напряжением. VD тАУ блок выпрямителей, СТ тАУ блок стабилизаторов напряжения.

В VD производится преобразование переменного тока в постоянный и фильтрация полученных нестабилизированных напряжений.

Блок СТ обеспечивает питание электронных схем СУ стабилизированными напряжениями Uп. При подключении СУ к питающей сети предусмотрено автоматическое тАЬобнулениетАЭ счетчика с помощью схемы формирования (i2).

-

Разработка формирователей логических уровней (ФЛУ).

-

Разработка принципиальной схемы ФЛУ.

ФЛУ предназначены для преобразования аналогового сигнала датчиков признаков (UД1, UД2, UД3) в цифровой сигнал. При этом должно быть выполнено условие: цифровой сигнал признаков (Х1, Х2, Х3) принимает тАЬединичноетАЭ значение, если:

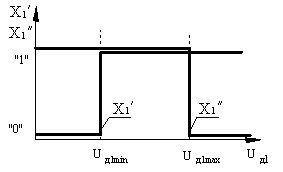

Реализуем поставленную задачу использовав два компаратора, формирующих выходные сигналы Х1′, Х1″ в соответствии с условием (2). Диаграмма работы компараторов представлена на рисунке 3.

Рисунок 3.Диаграмма работы компараторов

Рассмотрим работу компараторов для одного канала преобразования аналогового сигнала первого датчика UД1 в цифровой Х1.

На диаграмме (рисунок 3) представлены зависимости выходных сигналов компараторов Х1′ и Х1″ от величины входного сигнала датчика признаков UД1. При напряжении датчика:

;

;

при  .

.

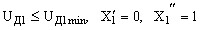

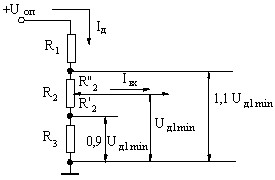

Принципиальная схема, реализующая диаграмму (рисунок 3) и задание пороговых уровней UД1min и UД1max, представлена на рисунке 4.

Рисунок 4.Принципиальная схема ФЛУ

Интегральный компаратор DA1.1 формирует цифровой сигнал Х1′, а DA1.2 тАУ Х1″. С выхода делителя R1, R2, R3 задается пороговый уровень, равный напряжению UД1min, а с выхода делителя R4, R5, R6 тАУ UД1max. Схема (рисунок 4) дополнена логическим устройством DD1.1 , состояние которого в зависимости от UД1 приведено в таблице 3.

Таблица 3.Состояния логического устройства DD1

UД1

|

Х1′

|

Х1″

|

Х1

|

UД1 < UД1min

|

0

|

1

|

0

|

UД1min ≤ UД1 ≤ UД1max

|

1

|

1

|

1

|

UД1 > UД1max

|

1

|

0

|

0

|

|

|

0

|

0

|

*

|

Логическая функция Х1не определена на наборе Х1′=0, Х1″=0, так как логическая функция технологически не может быть задана. Поэтому при формализации на этом наборе Х1 может принять любое значение 0 или 1. В данном случае целесообразным является нулевое значение функции Х1 на наборе Х1′=0, Х1″=0. Окончательный вид таблицы состояния функции Х1 дан в таблице 4.

Таблица 4.Таблица истинности функции Х1

Х1′

|

Х1″

|

Х1

|

0

|

0

|

0

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

1

|

1

|

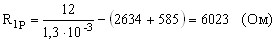

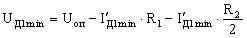

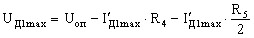

На инвертирующий вход компаратора DA1.1 с выхода потенциометра R2 (рисунок 4) подается пороговый уровень UД1min, а с выхода R6 тАУ UД1max на не инвертирующий вход DA1.2. Так как аналоговый сигнал датчика признаков Uд положительной полярности, то и опорное напряжение (Uоп) выбираем положительной полярности.

Выбор величины Uоп определяется наибольшим значением напряжений UД1max, UД2max, UД3max, в данном случае 9,3 В. Условием выбора величины напряжения Uоп определим его превышение на 10 тАУ 20% относительно наибольшего значения из UД1max, UД2max, UД3max, получаем:

Схемы формирования логических сигналов Х2 и Х3 аналогичны схеме на рисунке 4. При этом параметры резисторов R1, R2, R3 и R4, R5, R6 будут посчитаны в соответствии с заданными значениями UД2min, UД2max, UД3min, UД3max.

Логическое устройство (рисунок 4), реализующее функцию (2), выполнено на логическом элементе 3И (DD1.1). На третий вход подается выход датчика Д4, единичное значение которого разрешает формирование логического сигнала Х1. Окончательно, таблица состояния для логического элемента DD1 имеет вид таблицы 5.

Таблица 5.Состояние DD1.

Х1′

|

Х1″

|

Д4

|

Х1

|

0

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

Рассмотрим работу схемы (рисунок 4).

При Uд < Uдmin, положительный пороговый уровень Uдmin на инвертирующем входе DA1 определяет нулевой уровень выхода Х1′. На не инвертирующем входе DA1.2 действует положительное напряжение Uдmax и на выходе Х1″ формируется единичный уровень.

При Uд тЙе Uдmin, выход компаратора DA1.1 переключается на высокий уровень, а выход компаратора DA1.2 остается на прежнем высоком уровне.

При Uд = Uдmax выход компаратора DА1.1 остается без изменения на высоком уровне, а выход компаратора DA1.2 переключается на нулевой уровень. При Uд > Uдmax состояние компараторов не изменяется.

Формирование выходного логического сигнала признака Х1 производится по высокому уровню сигнала датчика Д4.

Если Д4 = 1 и Uдmin ≤ Uд ≤ Uдmax, то Х = 1;

если Д4 = 1 и Uд < Uдmin или Uд > Uдmax, то Х = 0.

Формирование логических уровней Х2, Х3 осуществляется аналогично описанному выше для Х1.

Выбор типа компаратора.

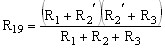

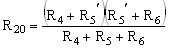

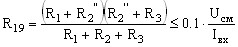

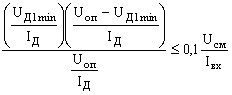

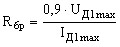

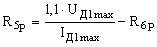

Расчет схемы сводится к выбору типа компаратора и определения параметров резисторов R1, R2, R3, R4, R5, R6, R19, R20.

В основу расчета приняты 2 условия:

1. Минимальное влияние входных токов Iвх компаратора

2. Минимальное влияние величины напряжения смещения Uсм на формирование выходного сигнала (на точность работы).

Первое требует равенства эквивалентных сопротивлений, подключаемых к инвертирующему и не инвертирующему входам компаратора:

,

,  .

.

Условие (3) приводит к необходимости включения дополнительных резисторов R19 и R20 на соответствующие входы компараторов DA1.1 и DA1.2.

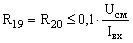

Второе условие ограничивает величину эквивалентных сопротивлений, подключаемых к входам компаратора:

,

,

где:

Uсм тАУ напряжение смещения выбранного компаратора,

Iвх тАУ входной ток выбранного компаратора.

Определим точнее условие (4). Будем считать, что снижение эквивалентного сопротивления по отношению к значению Uсм/Iвх на порядок, является достаточным. Тогда условие (4) будет иметь вид:

.

.

При этом следует иметь ввиду, что влияние Uсм на точность не исключено. Сведено до минимума влияние входных токов Iвх выполнением условий (3) и (4).

При выборе типа компаратора учтём два положения:

а) возможность формирования выходного цифрового сигнала, соответствующего стандартному уровню КМОП серии логических элементов,

б) численное значение напряжения смещения Uсм, приведенное в справочных данных.

Если напряжение Uсм велико, то необходимо применить дополнительную схему балансировки, подключаемую к дополнительным выводам NC компаратора в соответствии с рекомендацией, приводимой в литературе . Напряжение Uсм будем считать большим, если:

.

.

А мы имеем следующее:

это условие выполняется при исползовании компаратора К597СА3.Параметры UСМ = 0,005 В,IВХ = 0,25мкА

это условие выполняется при исползовании компаратора К597СА3.Параметры UСМ = 0,005 В,IВХ = 0,25мкА

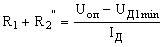

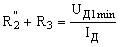

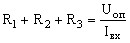

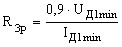

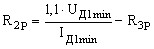

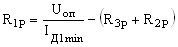

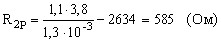

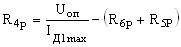

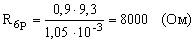

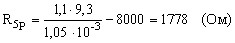

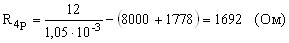

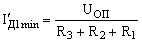

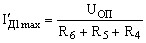

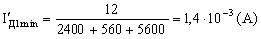

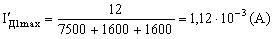

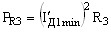

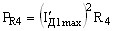

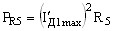

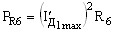

Расчет параметров элементов принципиальной схемы.

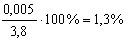

При расчете сопротивлений резисторов делителей, задающих требуемые пороговые значения напряжений, определим ток, протекающий через делитель. Рассмотрим делитель напряжения R1, R2, R3 для задания порогового уровня UД1min (рисунок 5). Делитель напряжения необходимо спроектировать так, чтобы с выхода R2 можно было получить UД1min при выборе стандартных (по ГОСТ) значений сопротивлений резисторов R1, R2, R3. Задача расчета существенно упрощается, если выбрать ток делителя R1, R2, R3 тАУ Iд, значительно превышающий входной ток компаратора Iвх.

Если

,

,

то входной ток компаратора можно не учитывать при расчете сопротивлений резисторов.

Для точной установки напряжения порогового уровня используется регулировочный резистор R2. Осью потенциометра можно плавно изменить величину порогового напряжения в пределах от 0,9UД1min до 1,1UД1min.

Рисунок 5.Схема делителя

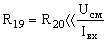

Для определения тока делителя (Iд). необходимо воспользоваться формулой (3) с учетом выражения (5) :

,

, ,

, ,

, .

.

С учетом формул (9), (10), (11) преобразуем соотношение (8) и представим в виде:

.

.

Из уравнения (12) определим неизвестный ток делителя Iд:

.

.

Ток делителя R4, R5, R6 будет определен аналогично выражению (13):

.

.

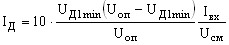

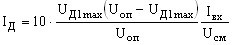

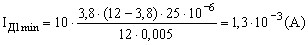

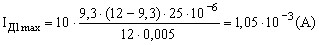

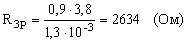

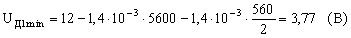

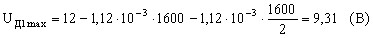

Подставляя в выражения (13) и (14) паспортные значения компаратора К597СА3, Uсм= 0,005 В, Iвх= 0,25мкА и исходные данные напряжений датчиков Д1, Д2, Д3, получим:

Проверяя условие  делаем вывод, что входным током компаратора можно пренебречь из-за малой величины, и пользуясь только током делителя IД рассчитаем сопротивления резисторов делителя для датчика Д1:

делаем вывод, что входным током компаратора можно пренебречь из-за малой величины, и пользуясь только током делителя IД рассчитаем сопротивления резисторов делителя для датчика Д1:

,

, ,

, ,

,

,

, ,

, ,

,

где: R1p, R2p, R3p, R4p, R5p, R6p тАУ расчетные сопротивления резисторов.

Далее по ГОСТ выбираем номиналы сопротивлений резисторов R1 R2, R3, R4, R5, R6 по условию:

R1 ≤ R1p, R2 ≤ R2p, R3 ≤ R3p, R4 ≤ R4p, R5 ≤ R5p, R6 ≤ R6p,

то есть из ряда стандартных значений выбирается равное ближайшее или меньшее значение.

С учётом гостированных номиналов резисторов рассчитаем ток делителей:

Далее делаем проверку возможности установки требуемого напряжения на резисторах R2 и R5:

С резисторами, выбранными по ГОСТ мы сможем обеспечить необходимые напряжения на входах компаратора.

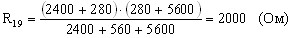

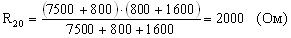

По формуле 3 рассчитаем сопротивление эквивалентных резисторов:

,

,

.

.

Расчёт резисторов для датчиков Д2 тАУ Д3 проводится аналогично описанному выше.

Проводя аналогичные вычисления для резистивных делителей датчиков Д2 и Д3 с тем же компаратором К597СА3 расчитаем сопротивления резисторов:R7 тАУ R18 и R21 тАУ R24.

R7=3900 (OM), R8=750 (OM), R9=3300 (OM), R10=2000 (OM),

R11=1300 (OM), R12=6200 (OM), R13=3600 (OM), R14=750 (OM),

R15=3300 (OM), R16=2700 (OM), R17=1000 (OM), R18=4300 (OM),

R21=2000 (OM), R22=2000 (OM), R23=2000 (OM), R24=2000 (OM),

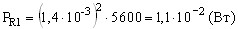

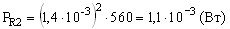

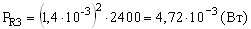

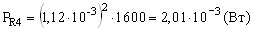

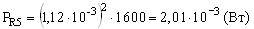

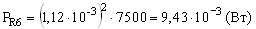

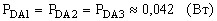

Определение мощности и тока, потребляемых ФЛУ.

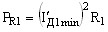

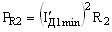

Рассчитаем рассеиваемую мощность резисторов на примере формирователя логического уровня для первого датчика:

,

,  ,

,  ,

, ,

,  ,

,  .

.

где:  ,

,  ,

,  ,

,  ,

,  ,

,  - расчетные значения рассеиваемых мощностей.

- расчетные значения рассеиваемых мощностей.

тАУ уточненное значение тока делителя после выбора резисторов по ГОСТ.

тАУ уточненное значение тока делителя после выбора резисторов по ГОСТ.

,

,

,

,

,

,

,

,

.

.

Номинальное значение рассеиваемой мощности PHR должно быть не менее расчетной:

Аналогично просчитав мощности резисторов делителей датчиков Д2 тАУ Д3, определим суммарное потребление мощности резистивных делителей датчиков:

Ток потребления одного корпуса микросхемы компаратора равен 3,6 мА, в нашем случае 3 корпуса. Мощность потребления микросхемы выполняющую функцию 3ИтАУНЕ (К564ЛА9) равна 20 мВт на каждый логический элемент. Общая потребляемая мощность ФЛУ будет равен сумме всех обозначенных ниже мощностей:

Где:

тАУ ток потребляемый микросхемой от двухполярного питания.

тАУ ток потребляемый микросхемой от двухполярного питания.

-

Проектирование цифрового автомата.

-

Минимизация логической функции автомата.

Задачи в цифровой технике, как правило, формируются в виде таблиц истинности. Решение задачи сводится к нахождению аналитического выражения логической функции, которое соответствовало бы этой таблице. В данной задаче программа сортировки заданна следующей таблицей истинности:

Таблица 6.Программа сортировки.

Номер набора

|

Х1

|

Х2

|

Х3

|

Y

|

0

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

1

|

0

|

2

|

0

|

1

|

0

|

0

|

3

|

0

|

1

|

1

|

1

|

4

|

1

|

0

|

0

|

1

|

5

|

1

|

0

|

1

|

0

|

6

|

1

|

1

|

0

|

1

|

7

|

1

|

1

|

1

|

0

|

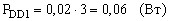

В таблице истинности выделим строки, в которых выходная переменная Y принимает значение 1. Для каждой строки таблицы составляем конъюнктивный терм (контерм) тАУ логическое умножение всех входных переменных. Причем записывают сомножитель в прямом виде тАУ Xi, если рассматриваемая переменная равна тАЬ1тАЭ, в противном случае записывают в инверсном виде тАУ  i. Таким образом составляем столько выражений, сколько имеется строк с Y=1;

i. Таким образом составляем столько выражений, сколько имеется строк с Y=1;

Записывая логическую сумму всех найденных контермов, получаем искомую функцию в дизъюнктивной форме.

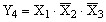

В соответствии с таблицей истинности (таблица 6) в строках 3, 4, 6 функция Y=1. Контермы для каждой из строк имеют следующий вид:

а) строка 3 тАУ  ;

;

б) строка 4 тАУ  ;

;

в) строка 6 тАУ  .

.

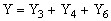

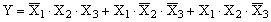

Искомая функция записывается в виде логической суммы конъюнктивных термов:

или

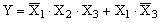

Преобразуем выражение (30) по правилам алгебры логики. В соответствии с дистрибутивным законом:

.

.

Логическая схема, построенная по выражению (31), приведена на рисунке 6.

Рисунок 6.Схема функциональная логического устройства.

Разработка принципиальной схемы автомата.

В КМОП тАУ серии, логических элементов И не выпускают, да и целесообразно наиболее полно использовать элементы одной микросхемы, так как увеличение числа корпусов микросхем ведёт к увеличению потребляемой мощности всей схемы и стоимости. Поэтому логическое выражение (31) преобразуем с помощью теоремы Де Моргана:

В связи с необходимостью применения элемента 3И-НЕ, в схеме сброса счётчиков, и в целях уменьшения количества корпусов микросхем и как следствие уменьшения энергопотребления, целесообразно использовать такие же элементы (3И-НЕ) в схеме ФЛУ+ЦА. Поэтому функцию (32) реализуема на 3-х элементах 3-И-НЕ и двух инверторах. Функциональная схема приведена на рисунке 7.

Рисунок 7.Схема цифрового автомата

Определение мощности и тока, потребляемых цифровым автоматом.

Мощность потребления микросхемы DD3 (К561ЛА9) равна 20мВт на каждый логический элемент. Учтём потребление мощности инверторов применённых в ФЛУ и выполненных на микросхеме DD2 (К561ЛА9).

-

Разработка двоично-десятичного счетчика.

-

Обоснование и выбор типа интегральной микросхемы двоично-десятичного счетчика.

В интегральном исполнении выпускаются асинхронные и синхронные импульсные счетчики. По способу кодирования внутренних состояний указанные счетчики делятся на двоичные, двоично-десятичные (декадные) и др. Кроме того, следует различать суммирующие (UP тАУ counter), вычитающие (DownтАУcounter) и реверсивные (Up тАУ down тАУ counter) счетчики.

Для решения поставленной задачи целесообразно использовать синхронные двоично-десятичные счетчики в интегральном исполнении. Возможен выбор реверсивного, хотя для простого счета предметов достаточным является использование суммирующего. Общим недостатком асинхронных импульсных счетчиков является последовательное срабатывание триггеров, а значит, большое время реакции на поступивший входной сигнал. Переключение триггеров в синхронных счетчиках происходит одновременно в течении времени задержки распространения. Последнее обстоятельство исключает появление помех (сигналов малой длительности и нестандартной амплитуды) особенно на выходе дешифраторов, фиксирующих достижение счетчиком определенного состояния.

Для счёта предметов в нашем случае и для согласования корпусов микросхем по входам, выделим из КМОП тАУ серии реверсивный программируемый счётчик 561ИЕ14. На рисунке 8 приведено УГО микросхем К564ИЕ14.

Рисунок 8. УГО микросхем К564ИЕ14

D0, D1, D2, D3 тАУ информационные входы; Q0, Q1, Q2, Q3 тАУ выходы; L тАУ вход записи информации, установленной на входах D0, D1, D2, D3 путем подачи высокого уровня напряжения; Р0 тАУ разрешение счета при низком уровне сигнала; С тАУ тактовый (счетный) вход; U тАУ при высоком уровне суммирующий режим, при низком уровне напряжения вычитающий режим работы; ML тАУ высокий уровень сигнала на входе определяет счет в двоичном формате, при низком счет ведется в двоично-десятичном формате; Р4 тАУ выход конца счета (переполнение).

Проектирование счетчика предметов на заданное число.

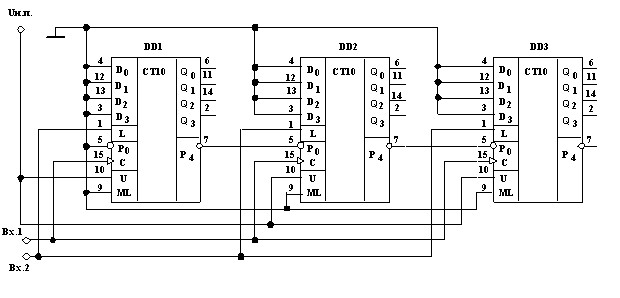

На рисунке 9 показана схема соединения трех микросхем в быстрый синхронный 12-разрядный счетчик до максимального десятичного числа 999.

Рисунок 9. Схема соединения трех микросхем

На вход Р0 (вывод 5) микросхемы DD1 подается низкий уровень, постоянно разрешая счет. Декада DD1 является младшей (единиц), декада DD3 - старшей (сотен). По входу 1 происходит счёт импульсов с выхода ЦА. Сигналом высокого уровня по входу 2 счетчик сбрасывается - тАЭобнуляетсятАЭ. так как на все информационные входы D0, D1, D2, D3 поданы тАЬнулитАЭ. Низкий уровень на входе ML определяет счёт в десятичной форме, Высокий уровень на входе U задаёт суммирующий режим.

Разработка дешифратора конца счета.

Программа сортировки предметов должна подать сигнал при достижении в контейнере предметов в количестве 789 шт. Разработаем дешифратора для окончания счёта. Счёт ведётся в десятичной форме, составим таблицу истинности для выходов счётчика представленного на рисунке 9:

Таблица 7.Таблица истинности дешифратора конца счёта

|

|

Единицы

|

Десятки

|

Сотни

|

Y1

|

Y10

|

Y100

|

Q1

|

Q2

|

Q3

|

Q4

|

Q5

|

Q6

|

Q7

|

Q8

|

Q9

|

Q10

|

Q11

|

Q12

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

2

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

3

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

4

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

5

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

6

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

0

|

7

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

0

|

1

|

8

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

1

|

0

|

9

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

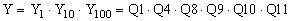

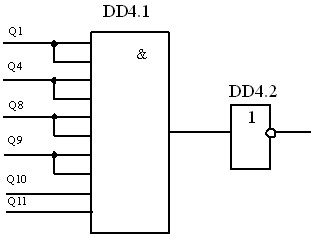

Функция дешифратора конца счёта имеет вид:

Реализуем эту функцию на 9-ти входовом элементе КМОП тАУ серии 9И-НЕ. Функциональная схема конца дешифратора счета примет вид:

Рисунок 10. Схема дешифратора конца счёта

Разработка схемы установки счетчика в исходное (нулевое) состояние

Необходимо решить четыре задачи:

тАУ формирование логического сигнала от дешифратора на число N;

тАУ формирование кратковременного логического сигнала при включении прибора в сеть;

тАУ формирование логического сигнала при нажатии кнопки тАЬСбростАЭ;

тАУ логическое объединение в один сигнал для управления счетчиком.

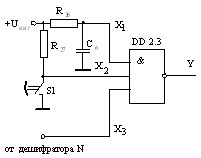

Счётчик обнуляется положительным перепадом напряжения, что бы наиболее просто обеспечить реализацию всех поставленных задач, выполним схему на элементе 3И-НЕ как показано на рисунке 11.

Рисунок 11. Схема сброса счётчика в исходное состояние

Время заряда конденсатора С6 до напряжения Uпит является временем автоматического сброса счетчика.

тАУ определяет время в течении которого будет заряжаться конденсатор С6.

тАУ определяет время в течении которого будет заряжаться конденсатор С6.

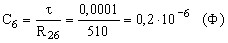

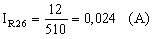

R26 для элементов КМОП-серий выбирают до (100) кОм. Время тАЬобнулениятАЭ ПД не следует выбирать большим, так как это приведет к необходимости выбора конденсатора большой емкости. Время не должно превышать значения 0,001 с. Выберем ПД = 1⋅10-4 (сек), и сопротивление резистора R26 = 510 (Ом).

Определим ёмкость конденсатора С6 по формуле 35:

.

.

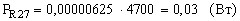

Активным уровнем, определяющим процесс тАЬобнулениятАЭ счётчика является высокий. Для ручного управления сбросом используем кнопку S2 подключённую к клемме тАЬ⊥тАЬ источника питания. Сопротивление R27 для КМОП-серий выберем равным 4,7 кОм. Повышенные значения сопротивлений для КМОП-серий не рекомендуются из-за условия ухудшения коммутации кнопкой S2 малых токов.

Активным уровнем дешифратора конца счёта является низкий. С учетом принятых схемных решений таблица истинности объединяющего логического узла (ЛУ) имеет вид таблицы 8.

Таблица 8. Выход ЛУ

Х1

|

Х2

|

Х3

|

Y

|

0

|

0

|

0

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

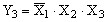

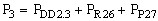

Определение мощности и тока, потребляемых счетчиком.

Мощность потребляемая схемой двоично тАУ десятичного счётчика (Pi) будет определяться суммой потребляемых мощностей схемы счёта (P1), дешифратора (P2)и схемой обнуления (P3).

,

,

,

,

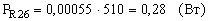

Мощность резисторов R26 R27рассчитаем по формуле (38):

,

,

,

,

Произведём подбор мощностей резисторов R26 и R27 по ГОСТ с учётом,

,

,

.

.

Мощность R26=0,5 Вт, R27=0,125 Вт.

Элемент DD3.3 (3И тАУ НЕ) входит в состав микросхемы К561ЛА9 применённой в схеме ФЛУ и мощность этого элемента уже учтена. Из этого следует, что мощность потребляемая схемой обнуления будет определяться только мощностью потребляемой резисторами R26 и R27:

,

,

.

.

-

Проектирование схемы индикации в десятичной форме.

-

Выбор типа дешифраторов и семисегментных индикаторов.

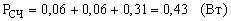

В качестве индикаторных устройств наибольшее применение находят полупроводниковые и жидкокристаллические семисегментные индикаторы (рисунок12).

При пропускании прямого тока через светодиод полоска (сегмент) начинает излучать свет красного, зеленого или желто-зеленого цвета. Определенное сочетание светящихся сегментов индицирует цифру или букву и при применении специальных дешифраторов создается возможность вывода цифровой и буквенной информации, отражающей состояние управляющих и вычислительных устройств.

Рисунок 12. УГО семисегментного индикатора АЛС321А

Наиболее удобочитаемым, является индикатор АЛС321А с общим катодом. Высота знака у этого индикатора 7,5 мм, цвет свечения жёлтотАУзелёный.Ток потребления каждого сегмента равен 0,02 (А), напряжение питания одного сегмента 3,6 (В)

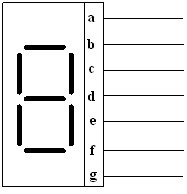

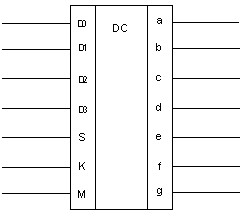

Специальные дешифраторы предназначены для преобразования двоичного кода в семисегментный код и управления полупроводниковыми семисегментными и жидкокристаллическими индикаторами. Рассмотрим дешифратор К176ИД2 (рисунок 13)

Рисунок 13. УГО дешифратора К176ИД2

Входы D0 тАУ D3 информационные входы, a-g тАУ выходы на семисегментный индикатор. При подаче на вход S высокого уровня тАУ разрешение преобразования двоичного кода в семисегментный код, при подаче низкого уровня тАУ тАЬзащёлкатАЭ. Высокий уровень на входе М определяет подключение семисегментного индикатора с общим анодом, низкий уровень тАУ с общим катодом. При наличии тАЬединицытАЭ на входе К все сегменты индикатора гаснут, низкий уровень разрешает индикацию. Таблица истинности дешифратора представлена в таблице 9.

Таблица 9. Таблица истинности дешифратора К176ИД2

D3

|

D2

|

D1

|

D0

|

L

|

PI

|

A

|

B

|

C

|

D

|

E

|

F

|

G

|

Символ на индикаторе

|

0

|

0

|

0

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

2

|

0

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

0

|

1

|

3

|

0

|

1

|

0

|

0

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

4

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

5

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

6

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

7

|

1

|

0

|

0

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

8

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

9

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

1

|

1

|

1

|

0

|

L

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

1

|

1

|

H

|

1

|

1

|

0

|

0

|

1

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

1

|

P

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

R

|

1

|

1

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

-

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

Отсутствие символа

|

Разработка принципиальной схемы индикации.

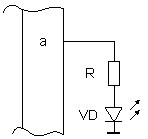

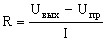

Максимальное прямое напряжение на сегменте индикатора равно 3,6 В. Наша задача тАУ понизить напряжение выхода дешифратора (+8,2 В) до напряжения 3,6 В. Реализуем эту задачу так как показано на рисунке 14:

Рисунок 14.

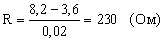

Найдём сопротивление резистора R по закону Ома:

Где U тАУ напряжение выхода дешифратора 8,2 В,

Uпр тАУ максимальное прямое напряжение на сегменте индикатора, 3,6 В,

I тАУ прямой ток сегмента, 20 мА.

Выберем по ГОСТу номинал резистора: R=240 Ом

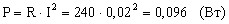

Рассчитаем мощность этого резистора:

Расчётная мощность резистора должна быть меньше выбранной по ГОСТу:

Р=0,125 (Вт)

Расчет мощности и тока, потребляемых схемой индикации.

Мощность потребления схемой индикации (Ринд) будет определяться по формуле (39).

где Ри тАУмощность потребляемая тремя индикаторами;

Рд тАУ мощность потребляемая тремя дешифраторами.

Ток потребления одним сегментом индикатора равен 20 мА. Возьмём крайний случай когда зажигаются все сегменты. В этом случае ток потребления индикатором будет равен 140 мА при прохождении прямого напряжения через сегментВа3,6ВаВ. Мощность потребления схемой индикации равна:

Потребляемая мощность дешифратора 0,05 Вт

-

Проектирование схем управления исполнительными механизмами.

-

Выбор типа интегральной микросхемы ждущего мультивибратора.

Смысл управления состоит в формировании сигнала заданной длительности. Эту задачу выполняет ждущий мультивибратор.

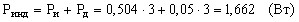

Из КМОП тАУ серии следует отметить микросхему К564АГ1 (рисунок 15).

Рисунок 15. УГО микросхемы К564АГ1

Микросхема К564АГ1 содержит два ждущих мультивибратора (ЖМ). Каждый ЖМ имеет прямой Q и инверсный  выходы. ЖМ можно запустить любым перепадом входного сигнала. Вход +TR используется для запуска ЖМ положительным перепадом, при этом на неиспользуемый вход -TR подать тАЬединичныйтАЭ сигнал (+Uп). Для запуска ЖМ отрицательным перепадом сигнал подается на вход -TR, а на +TR - тАЬнулевойтАЭ. Вход R используется для укорачивания выходного импульса или для предотвращения появления выходного импульса при включении напряжения питания, например, как показано на рисунке 15.

выходы. ЖМ можно запустить любым перепадом входного сигнала. Вход +TR используется для запуска ЖМ положительным перепадом, при этом на неиспользуемый вход -TR подать тАЬединичныйтАЭ сигнал (+Uп). Для запуска ЖМ отрицательным перепадом сигнал подается на вход -TR, а на +TR - тАЬнулевойтАЭ. Вход R используется для укорачивания выходного импульса или для предотвращения появления выходного импульса при включении напряжения питания, например, как показано на рисунке 15.

Длительность возбужденного состояния ЖМ для Cτ можно определить по формуле:

Расчет параметров элементов времязадающих цепей

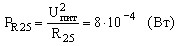

По формуле 40 рассчитаем ёмкость конденсатора C5 для импульса ПД1=0.019 (сек), задавшись R25=180000 (Ом):

Так как время ПД1= ПД2 параметры времязадающих цепей одинаковы.

Заданные резисторы и найденные конденсаторы соответствуют своими номиналами соответствующим ГОСТам.

Определим мощность резисторов:

Мощность PR25=PR28.

По ГОСТ выберем мощность резисторов равную 0,125 Вт.

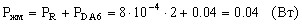

Мощность потребления схемами ждущих мультивибраторов определяется:

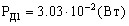

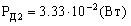

Расчет мощности и тока, потребляемых схемой.

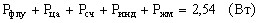

Рассчитаем суммарную мощность потребления всей схемой, суммировав полученные мощности в вышеизложенных расчётах, получим:

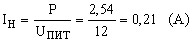

Определим ток потребления схемой:

-

Разработка источника питания.

-

Определение исходных данных (количество источников напряжения, требуемые величины напряжений и токов нагрузки).

Микросхемы КМОП тАУ серии можно питать широким спектром напряжений, от +3В до +15 В. Малым напряжением не рекомендуется питать эти микросхемы, сильно понижается быстродействие и увеличивается чувствительность к помехам. Максимальным напряжением также не целесообразно запитывать КМОП тАУ микросхемы, даже при малом повышении напряжения питания возможен выход из строя микросхемы. Мы остановимся на золотой середине. Обеспечив приличное быстродействие и запас по питанию, определим напряжения питания микросхем равным +12 В.

Микросхемы компараторов необходимо согласовать по выходу с выбранной нами КМОП тАУ серии по напряжению. Для этого запитаем их от источника двухполярного напряжения В±12 В.

Источник питания на +12 В должен обеспечивать ток нагрузки равный 0,21ВаА, а на напряжение -12 В тАУ 0,003 А.

Для обеспечения задания порогов соответствующих напряжений на входах микросхем DA1 тАУ DA3 необходим источник опорного напряжения на 12 В. Источник опорного напряжения должен обеспечивать ток нагрузки равный 0,008 А.

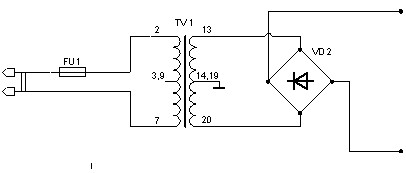

Выбор схемы выпрямления и типа диодов.

Для выпрямления полученного напряжения на вторичных обмотках трансформатора TV применим мостовую схему выпрямителя с выводом нулевой точки трансформатора (рисунок 16), необходимого при реализации получения двух разнополярных относительно нулевой точки напряжений.

Рисунок 16. Схема выпрямителя на два одинаковых разнополярных напряжения

Диоды должны обеспечивать прохождение прямого тока нагрузки и напряжения, а также и обратного напряжения. К классу таких диодов относятся тАЬвыпрямительные диодытАЭ.

Трансформатор TV1 тАУ стандартный трансформатор вторичного питания ТПП тАУ 295 110 ПЛМ 22×32×58.

Выпрямительный мост VD2 тАУ КЦ405А который обеспечивает необходимые нам требования, ток нагрузки до 1А.

Расчет и выбор параметров схемы сглаживания пульсаций.

Активно-емкостная нагрузка выпрямителя создается для сглаживания кривой выпрямленного напряжения. Включение конденсатора параллельно нагрузке изменяет режим работы выпрямителя по сравнению с работой при чисто активной нагрузке.

Чем больше емкость конденсатора, тем меньше размах пульсаций. Рассчитаем емкость конденсаторов С1 тАУ С2 фильтра по заданным значениям тока нагрузки Iн и размаху пульсаций выпрямленного напряжения.

Максимальное мгновенное значение выпрямленного напряжения Udmax можно принять на 1,5тАУ2 В меньшим, чем амплитудное значение U2m, учтя падение напряжения на открытом диоде и на активном сопротивлении обмоток трансформатора. При выборе числового значения Udmin следует учесть, что Udmin должно быть на 25-30% больше, чем требуемое напряжение питания электронной схемы при указанном в задании минимальном напряжении питающей сети.

Ток, протекающий через конденсатор при разряде определяется по формулеВа41:

где С тАУ емкость конденсатора, Ф;

тАУ скорость изменения напряжения (производная), В/с.

тАУ скорость изменения напряжения (производная), В/с.

Примем, что разряд конденсатора подчиняется линейному закону. Тогда (41) можно записать в виде:

где ΔUc тАУ изменение напряжения на конденсаторе за время Δt.

Примем:

где Тn тАУ период пульсаций выпрямленного напряжения, равный 0,01с, соответствующий частоте 100 Гц.

Из (42) с учетом (43) получим выражение для расчета емкости конденсатора

Из ряда ГОСТа выберем значение ёмкости конденсатора равное 560 мкФ. Рабочее напряжение на конденсаторе должно быть на 10 тАУ 20% меньше его номинального значения, что следует учесть при выборе типа конденсатора.

Разработка принципиальной схемы стабилизаторов, расчет параметров схемы и выбор типа применяемых элементов.

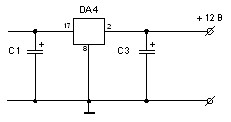

Стабилизацию выпрямленного положительного напряжения будем производить применив ИМ стабилизации напряжения КР142ЕН8Б включенную по схеме (рисунок 17):

Рисунок 17. Схема включения КР142ЕН8Б

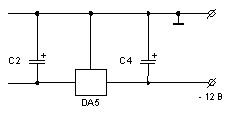

Конденсатор С3 выберем 510 мкФ, тем самым обеспечив минимальные пульсации стабилизированного напряжения. Применение этой микросхемы обеспечивает ток нагрузки до 1,5 А. Отрицательный источник питания будем стабилизировать ИМ КР1168ЕН12А (рисунок 18). Применение КР1168ЕН12А обеспечит ток нагрузки до 0,1 А. Ёмкость конденсатора С4 выберем равную С3.

Рисунок 18. Схема включения КР1168ЕН12А

-

Разработка и описание принципиальной схемы сортировочного устройства.

Руководствуясь блочной схемой описанной в п.1.3 соединим разработанные нами функциональные узлы в одну схему.

На вход Д1 тАУ Д3 сортировочного устройства подается сигнал от аналоговых датчиков Д1 тАУ Д3, измеряющих три параметра предметов. Четвёртый датчик Д4 выдаёт сигнал готовности процесса измерения в цифровой форме и подключается к входу Д4 сортировочного устройства.

Процесс преобразования аналоговых сигналов измерения в цифровой вид осуществляет блок формирователей логических уровней, состоящий из компараторов напряжения DA1 тАУ DA3 и делителей. При совпадении текущей совокупности измеренных параметров с заданной, выдаётся выходной сигнал цифрового элемента DD3.4, используемый для счёта и включения исполнительного механизма после формирования сигнала определённой длительности ПДим1 ждущим мультивибратором DА6.1. Счёт количества отсортированных предметов ведётся двоично-десятичными счётчиками DD5, DD8, DD10. Визуальная индикация числа предметов производится семисегментными индикаторами HG1тАжHG3 в десятичном виде. Для преобразования состояния счётчика DD5, DD8, DD10 из двоичного кода в код, необходимый для управления индикаторами HG1тАжHG3, используются специальные дешифраторы DD4, DD7, DD9.

Дешифратор DD6 определяет момент достижения заданного количества отсортированных предметов. Ждущим мультивибратором DA6.2 формируется сигнал управления длительностью ПДим2 вторым исполнительным механизмом. По этому же сигналу счётчик автоматически ''обнуляется'' с помощью обнуляющей системы DD2.3. Так же с помощью обнуляющей схемы возможно обнуление счётчика вручную и автоматическое обнуление счётчика при включении сортировочного устройства в сеть.

Выпрямители VD2 производят преобразование переменного тока в постоянный. Стабилизатор DА4 обеспечивает питание схемы сортировочного устройства положительным источником питания, а стабилизатор DA5 обеспечивает питание компараторов DA1 и DA2 отрицательным источником питания.

Управляющие исполнительными механизмами сигналы определённой длительности ПДим1 и ПДим2 снимаются с выводов ПДим1 и ПДим2 сортировочного устройства соответственно.

-

Заключение.

Разработанное в ходе курсового проекта сортировочное устройство питается от однофазной промышленной сети переменного тока 220 В частотой 50 Гц и обеспечивает надёжную работу при отклонениях напряжения питающей сети от номинального в пределах от плюс 10 до минус 15 %.

Данное сортировочное устройство предназначено для работы в закрытых стационарных помещениях при температуре окружающего воздуха в пределах от плюс 5ЛЪС до плюс 40ЛЪС.

Расчётная потребляемая мощность СУ 2,54 Вт, токопотребление 0,21 А

Все расчёты производились в программе EXEL.

-

Список литературы.

- Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. Е.А. Зельдин. - Л.: Энергоатомиздат. Ленингр. отд-ние, 1986.-280 с.: ил.

- Васерин Н.Н. и др. Применение полупроводниковых индикаторов / Н.Н. Васерин, Н.К. Дадерко, Г.А. Прокофьев; Под ред. Е.С. Лепина. - М.: Энергоатомиздат, 1991. тАУ 200 с.: ил.

- Аналоговые и цифровые интегральные микросхемы: Справочное пособие / С.В. Якубовский, Н.А. Барканов, Л.И.ВаНиссельсон и др.; Под ред. С.В. Якубовского. тАУ 2-е изд., перераб. и доп. тАУ М.: Радио и связь, 1984. тАУ 432 с. ил. - (Проектирование РЭА на интегральных микросхемах).

- Шило В.Л. Популярные цифровые микросхемы: Справочник. тАУ М.: Радио и связь, 1987. тАУ 352 с.: ил. тАУ (Массовая радиобиблиотека. Вып. 1111).

- Вениаминов В.Н., Лебедев О.Н., Мирошниченко А.И. Микросхемы и их применение: Справ. пособие. тАУ 3-е изд., перераб. и доп. тАУ М.: Радио и связь, 1989. 240 с.: ил тАУ (Массовая радиобиблиотека: Вып. 1143).

- Интегральные микросхемы: Справочник / Б.В. Тарабрин, Л.Ф. Лунин, Ю.Н. Смирнов и др.; Под ред. Б.В. Тарабрина. тАУ М.: Радио и связь, 1984 -528 с., ил.

- Забродин Ю.С. Промышленная электроника: Учебник для ВУЗов. тАУ М.: Высш. школа, 1982. тАУ 496 с., ил.

- Браммер Ю.А., Пащук И.Н. Импульсная техника. Учебник для учащихся электрорадиоприборостроительных техникумов. тАУ 5-е изд., перераб. и доп. тАУ М.: Высш. шк., 1985. тАУ 320 с., ил.

- Бедрековский М.А. и др. Интегральные микросхемы: Взаимозаменяемость и аналоги: Справочник / М.А. Бедрековский, А.А Косырбанов, П.П. Мальцев. тАУ М.: Энергоатомиздат, 1991. тАУ 272 с.: ил.

- Справочник по полупроводниковым диодам, транзисторам и интегральным схемам / под общ. ред. Н.Н. Горюнова.тАУ4-е изд., перераб. и доп.тАУМ.: Энергия, 1978,744с., ил

Приложение 1

Таблица 10. Спецификация

Зона

|

Поз. обозначе-ние

|

Н а и м е н о в а н и е

|

Кол.

|

Примечание

|

|

|

|

Резисторы

|

|

|

|

|

R1

|

5,6 кОм В± 5 % МЛТ тАУ 0,125

|

1

|

|

|

|

R2

|

560 Ом СП5-16ВВ-0,125

|

1

|

|

|

|

R3

|

2,4 кОм В± 5 % МЛТ тАУ 0,125

|

1

|

|

|

|

R4, R5

|

1,6 кОм В± 5 % МЛТ тАУ 0,125

|

2

|

|

|

|

R6

|

7,5 кОм В± 5 % МЛТ тАУ 0,125

|

1

|

|

|

|

R7

|

3,9 кОм В± 5 % МЛТ тАУ 0,125

|

1

|

|

|

|

R8, R14

|

750 Ом СП5-16ВВ-0,125

|

2

|

|

|

|

R9, R15

|

3,3 кОм В± 5 % МЛТ тАУ 0,125

|

2

|

|

|

|

R10, R19..R24

|

2 кОм В± 5 % МЛТ тАУ 0,125

|

7

|

|

|

|

R11

|

1,3 кОм СП5-16ВВ-0,125

|

1

|

|

|

|

R12

|

6,2 кОм В± 5 % МЛТ тАУ 0,125

|

1

|

|

|

|

R13

|

3,6 кОм В± 5 % МЛТ тАУ 0,125

|

1

|

|

|

|

R16

|

2,7 кОм В± 5 % МЛТ тАУ 0,125

|

1

|

|

|

|

R17

|

1 Ом СП5-16ВВ-0,125

|

1

|

|

|

|

R18

|

4,3 кОм В± 5 % МЛТ тАУ 0,125

|

1

|

|

|

|

R25, R28

|

180 кОм В± 5 % МЛТ тАУ 0,125

|

2

|

|

|

|

R26

|

510 Ом СП5-16ВВ-0,125

|

1

|

|

|

|

R27

|

4,7 кОм В± 5 % МЛТ тАУ 0,125

|

1

|

|

|

|

R29тАжR49

|

240 Ом В± 5 % МЛТ тАУ 0,125

|

21

|

|

|

|

|

|

|

|

|

|

|

Конденсаторы

|

|

|

|

|

С1, С2

|

560 мкФ К53-22-100В В±5%-В

|

2

|

|

|

|

С3, С4

|

510 мкФ К53-22-100В В±5%-В

|

2

|

|

|

|

С5, С6, С7

|

0,2 мкФ К53-22-100В В±5%-В

|

3

|

|

|

|

|

|

|

|

|

|

|

Микросхемы

|

|

|

|

|

DA1..DA3

|

KP597CA3

|

3

|

|

|

|

DA4

|

КР142ЕН8Б

|

1

|

|

|

|

DA5

|

КР1168ЕН2А

|

1

|

|

|

|

DA6

|

KP564АГ1

|

1

|

|

|

|

DD1, DD2

|

K561ЛA9

|

2

|

|

|

|

DD3

|

К564ЛА7

|

1

|

|

|

|

DD6

|

K176ЛИ1

|

1

|

|

|

|

DD5, DD8, DD10

|

K564ИЕ14

|

3

|

|

|

|

DD4, DD7, DD9

|

K176ИД2

|

3

|

|

Окончание таблицы 10

Зона

|

Поз. обозначение

|

Н а и м е н о в а н и е

|

Кол.

|

Примечание

|

|

|

|

Индикаторы

|

|

|

|

|

HG1тАжHG3

|

АЛС321А

|

3

|

|

|

|

|

|

|

|

|

|

|

Диоды

|

|

|

|

|

VD1

|

КЦ405А

|

1

|

|

|

|

|

|

|

|

|

|

S1

|

Кнопка ПКн41

|

1

|

|

|

|

S2

|

Кнопка КМ1-1

|

1

|

|

|

|

|

|

|

|

Вместе с этим смотрят:

Электронные вольтметрыЭнергетический расчет спутниковой линии связи для передачи телевизионных сигналовЭффект Ганна и его использование в диодах, работающих в генераторном режимеАбразивы