Дослiдження методiв та iнструментальних засобiв проектування цифрових пристроiв на основi програмованих логiчних iнтегральних схем (ПЛРЖС)

Дослiдження методiв та iнструментальних засобiв проектування цифрових пристроiв на основi ПЛРЖС

1. Огляд елементноi бази, що застосовуiться для побудови логiчних керуючих автоматiв з паралельною архiтектурою

1.1 Класифiкацiя

Для побудови логiчних керуючих автоматiв з паралельною архiтектурою використовують пристроi з регулярною архiтектурою, якi представляють собою набiр стандартних елементiв та вузлiв, що iнтегрованi на одному кристалi. РЖснуi багато рiзновидiв таких пристроiв, але всi вони обтАЩiднуються однiiю назвою тАУ програмованi логiчнi iнтегральнi схеми.

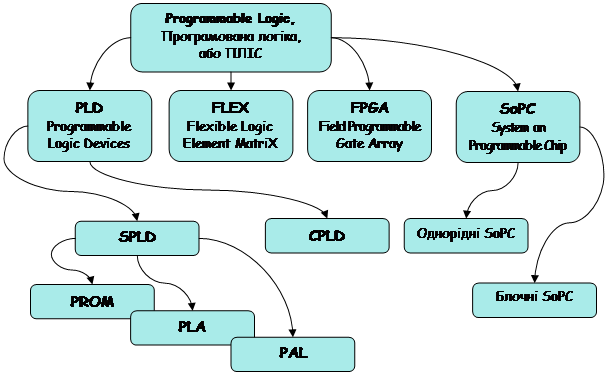

Настроювання ПЛРЖС на виконання заданих функцiй здiйснюються користувачем шляхом вiльного компонування цих елементiв i вузлiв програмним способом. Завдяки зазначеним особливостям ПЛРЖС в останнi роки успiшно завойовують ринок i в рядi предметних областей становлять гiдну конкуренцiю мiкропроцесорам i мiкроконтролерам. Залежно вiд використовуваноi архiтектури ПЛРЖС можуть бути класифiкованi таким чином (рис. 1).

Структури ПЛРЖС мають високий рiвень регулярностi: основу кристала ПЛРЖС становить матриця однотипних функцiональних вузлiв, на базi яких користувач може створювати цiлi системи керування складними технологiчними об'iктами. Завдяки цьому ПЛРЖС характеризуються високою швидкодiiю i надiйнiстю, а також широкими можливостями в частинi резервування i дiагностики.

Найбiльш ефективними областями застосування ПЛРЖС i:

1. синтез (моделювання) нетрадицiйних архiтектур керуючих автоматiв (навiть якщо надалi плануiться використання iншоi елементноi бази);

2. побудова надшвидкодiючих керуючих пристроiв;

3. реалiзацiя автономних систем керування критичного застосування, до яких пред'являються жорсткi вимоги в частинi забезпечення надiйностi, безпеки, електромагнiтноi сумiсностi й т.iн.

Рис. 1. Класифiкацiя ПЛРЖС

1.2 Стандартнi програмованi логiчнi пристроi (SPLD)

До перших ПЛРЖС, якi з'явилися на початку 70-х рокiв, вiдносяться програмованi постiйнi запам'ятовуючi пристроi (ППЗП тАУ Programmable Read Only Memory тАУ PROM). Перший час PROM використовували винятково для зберiгання iнформацii, пiзнiше iх стали застосовувати для реалiзацii логiчних функцiй.

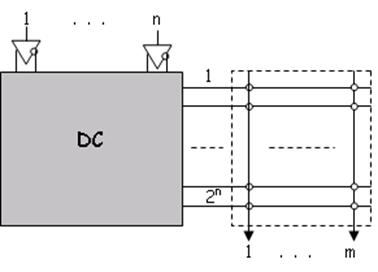

Структура PROM (рис. 2) мiстить двi матрицi: матриця DC, настроiна на реалiзацiю функцii повного дешифратора, i програмована матриця ВлАБОВ» (ВлORВ»). PROM дозволяi реалiзувати логiчнi функцii, представленi в довершенiй диз'юнктивнiй нормальнiй формi.

Рис. 2. Структура ППЗП тАУ Programmable Read Only Memory

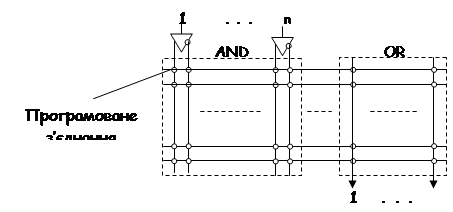

З 1971 р. стали випускатися програмованi логiчнi матрицi (ПЛМ тАУ Programmable Logic Array тАУ PLA), якi мiстять двi програмованi матрицi (рис. 3), одна з яких настроiна на реалiзацiю функцii ВлРЖВ» (ВлANDВ»), а iнша тАУ функцii ВлАБОВ» (ВлORВ»).

Рис. 3. Структура ПЛМ тАУ Programmable Logic Array тАУ PLA

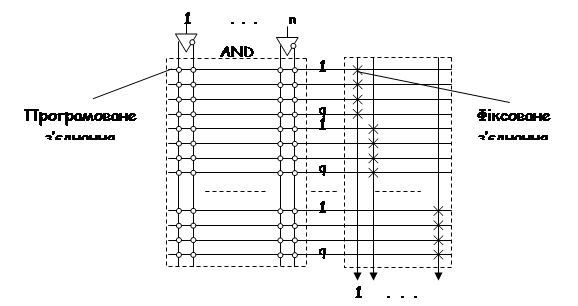

Удосконалювання структури PLA привело до створення програмувованих матриць логiки (ПМЛ тАУ Programmable Array Logic тАУ PAL), у яких, на вiдмiну вiд PLA, програмуiться тiльки матриця РЖ, а матриця АБО маi фiксовану настройку, при якiй q промiжних шин зв'язуiться з одним виходом (рис. 4). Це дозволяi матрицю АБО реалiзувати у виглядi сукупностi q-входових дизъюнкторiв. Вихiднi буфери, що визначають архiтектуру PAL, являють собою програмованi макроосередки, якi можуть включати iнвертор iз трьома станами, тригери рiзних типiв, елементи Влвиключне АБОВ» i iн.

Рис. 4. Структура ПМЛ тАУ Programmable Array Logic тАУ PAL

Описанi вище структури ПЛРЖС вiдносяться до стандартних програмованих логiчних пристроiв (стандартних ПЛП, Standard Programmable Logic Devices, SPLD).

1.3 Складнi програмованi логiчнi пристроi (CPLD)

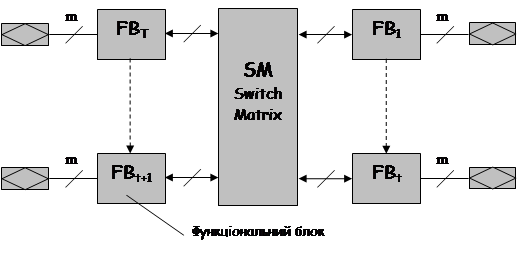

Удосконалювання технологii виробництва ПЛРЖС привело до можливостi реалiзацii на одному кристалi декiлькох PAL, що поiднуються програмованими з'iднаннями. Такi ПЛРЖС одержали назву складних ПЛП (Complex Programmable Logic Devices, CPLD). Узагальнена структура CPLD (рис. 5) мiстить матрицю функцiональних блокiв FB i програмовану матрицю перемикань (Switch Matrix, SM).

Рис. 5 Структура CPLD

У бiльшостi CPLD функцiональнi блоки мають структуру, подiбну до програмованих матриць логiки, тому iх найчастiше називають PAL-блоками. У кожного PAL-блоку i множина двунаправлених виводiв, по яким надходять оброблюванi сигнали. Основнi логiчнi перетворення виконуються в PAL-блоках, а матриця перемикань служить лише для передачi сигналiв мiж ними. Також у структурi CPLD присутнi спецiалiзованi входи, зв'язанi як з матрицею перемикань, так i з усiма PAL-блоками. Цi входи звичайно використовують для передачi глобальних сигналiв синхронiзацii i керування пристроiм.

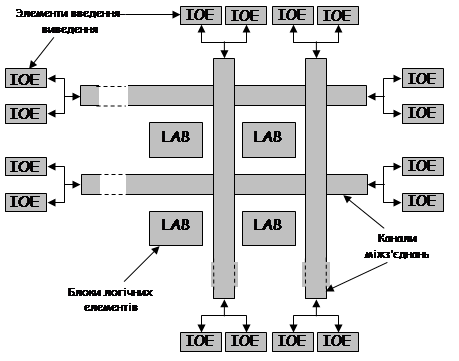

1.4 Матрицi елементiв гнучкоi логiки (FLEX)

Подальший розвиток структура CPLD одержала в мiкросхемах фiрми Altera, названих матрицями елементiв гнучкоi логiки (Flexible Logic Element Matrix тАУ FLEX). У таких ПЛРЖС вiдсутня звична PAL-структура, а i блоки логiчних елементiв, що поiднуються в LAB-модулi, зв'язок мiж якими здiйснюються за допомогою горизонтальних i вертикальних каналiв мiж з'iднань (рис. 6).

Рис. 6. Структура FLEX

LAB-модулi являють собою сукупнiсть логiчних елементiв (LE), об'iднаних локальною шиною мiж з'iднань i наявнiстю ланцюгiв переносу й каскадування. Кожний логiчний елемент включаi функцiональний генератор, що може програмно настроюватися на табличну реалiзацiю будь-якоi функцii певного числа змiнних. Елементи вводу-виходу (РЖOE), що обслуговують зовнiшнi виходи, пiдключаються безпосередньо до каналiв мiжзтАЩiднань.

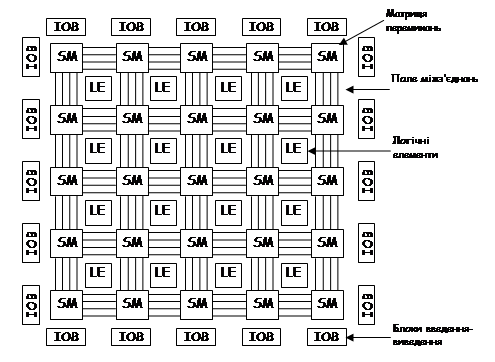

1.5 Вентильнi матрицi, що програмуються користувачем (FPGA)

Якщо в FLEX-пристроях лiнii каналiв проходять через всю довжину або ширину кристала, то в програмованих користувачем вентильних матрицях (Field Programmable Gate Array тАУ FPGA) лiнii каналiв складаються з окремих сегментiв, що з'iднують програмованими матрицями перемикань, якi дозволяють передавати сигнали в кожному iз чотирьох напрямкiв (рис. 7).

Рис. 7. Структура FPGA

Сегментованi мiжзтАЩiднання можуть утворювати складнi розгалуженi ланцюги, завдяки чому кожному з'iднанню може бути знайдено кiлька альтернативних шляхiв, при цьому ефективно використовуються металiзованi лiнii сегментiв.

Основу логiчних елементiв в FPGA представляi функцiональний генератор, подiбний до аналогiчного пристрою логiчних елементiв LAB-модулiв FLEX-пристроiв.

Протягом перших рокiв розвитку ПЛРЖС архiтектури CPLD i FPGA були представленi в ВлчистомуВ» видi, але кожна з них маi своi переваги та недолiки. Прагнення до сполучення переваг обох типiв архiтектур привело до появи ПЛРЖС iз комбiнованою архiтектурою, якi вiдрiзняються бiльшою розмаiтiстю варiантiв i рiзним ступенем близькостi до того або iншого класичного типу ПЛРЖС.

Фактичне iснування ПЛРЖС iз комбiнованою архiтектурою й вiдсутнiсть для них загальноприйнятоi узагальнюючоi назви вносять вiдчутнi незручностi в процес класифiкацii ПЛРЖС. Найчастiше ПЛРЖС iз комбiнованою архiтектурою представляються виробником пiд конкретним iм'ям, у якому не згадуiться нi CPLD, нi FPGA.

1.6 ПЛРЖС типу Влсистема на кристалiВ»

Значимiсть можливостi створення закiнченоi системи на одному кристалi очевидна тАУ така система маi високi якiснi показники. Для переважноi бiльшостi розроблювачiв створення системи на одному кристалi здiйснено тiльки на основi ПЛРЖС, тому що замовлене проектування по економiчним мiркуванням можливо тiльки при масовому виробництвi.

Термiн SOPC (System On Programmable Chip), тобто Влсистема на програмованому кристалiВ», був уперше введений фiрмою Altera. До SOPC вiдносять ПЛРЖС найбiльшого рiвня iнтеграцii, що мiстять сотнi тисяч i навiть мiльйони еквiвалентних вентилiв.

Зараз на ринку присутнi велике число SOPC, i серед них намiтилися своi пiдкласи й проблемнi орiiнтацii. Однак доцiльно роздiлити клас SOPC на два пiдкласи: однорiдних i блокових систем на кристалi.

В однорiдних SOPC рiзнi блоки системи реалiзуються тими самими апаратними засобами, використовуючи при розробцi так званi Влодиницi iнтелектуальноi власностiВ» РЖP (РЖntellectual Properties), тобто заздалегiдь реалiзованi параметризуiмi мегафункцii. Всi блоки системи, називанi Soft-ядрами (Softcores) i повнiстю синтезуiмi, можуть перемiщуватись й розмiщатися в рiзних областях кристала.

Блоковi SOPC мають апаратнi ядра, тобто спецiалiзованi областi кристала, видiленi для певних функцiй. У цих областях створюються блоки незмiнноi структури, оптимiзованi для заданоi функцii й не мають засобiв програмування. Такi блоки будемо називати hard-ядрами (Hardcores). Реалiзацiя функцiй спецiалiзованими апаратними ядрами вимагаi значно меншоi площi кристала в порiвняннi з реалiзацiiю Soft-ядер i збiльшуi швидкодiю блокiв, однак зменшуi унiверсальнiсть ПЛРЖС. Характерними прикладами hard-ядер, крiм процесорiв i мiкроконтролерiв можуть служити блоки для реалiзацii iнтерфейсiв рiзних шин (PCРЖ, VME), схеми пiдтримки iнтерфейсу JTAG, пристроi помноження для систем цифровоi обробки сигналiв. У ходi розвитку блокових SOPC характер i складнiсть ядер змiнювалися вiд вiдносно простих, у момент появи, до складних ядер у виглядi процесора або мiкроконтролера зi значною швидкодiiю у даний момент.

По своiм архiтектурним ознакам SOPС, як правило, вiдносяться до структур комбiнованого типу, у яких поiднуються ознаки FPGA i CPLD з перевагою ознак FPGA.

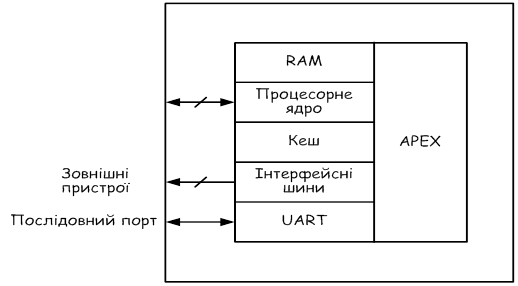

Як приклад блокового SOPC розглянемо ПЛРЖС сiмейства Excalibur фiрми Altera. Загальний план мiкросхеми (рис. 8) показуi основнi блоки кристала, у якому роль процесора грають ядра RAM або MРЖPS.

Рис. 8. Узагальнена структура SOPC

Мiкросхеми сiмейства Excalibur з апаратними процесорними ядрами дозволяють створювати системи з високою продуктивнiстю i помiрною функцiональною гнучкiстю. Плануiться розвиток лiнii Excalibur, зокрема реалiзацiя 64-розрядних процесорних ядер.

2. Аналiз систем автоматизованого проектування логiчних керуючих автоматiв на основi ПЛРЖС

2.1 Системи автоматизованого проектування фiрми Xilinx

При виборi елементноi бази для реалiзацii логiчних керуючих автоматiв одним iз важливих факторiв i наявнiсть достатньо розвинутих версiй САПР, що використовуються для пiдготовки проектiв, у тому числi для введення цих проектiв, iх компiляцii, комптАЩютерного моделювання, загрузки проекту на кристал ПЛРЖС. Програмнi продукти фiрм Xilinx та Altera на сьогоднiшнiй день i найбiльш поширеними САПР для проектування цифрових пристроiв на ПЛРЖС.

Серед програмних продуктiв Xilinx i як вiдносно простi вiльно розповсюджуванi системи, так i потужнi iнтегрованi пакети, що дозволяють розробляти ПЛРЖС еквiвалентноi iмностi бiльше 1000000 вентилiв. Серед безкоштовних САПР Xilinx варто видiлити систему WebFiTTER, перший у своiму родi продукт, заснований на використаннi РЖnternet.

Для бiльшостi користувачiв в Украiнi використання даного продукту може виявитися скрутним, оскiльки, на жаль, швидкiсний доступ в РЖnternet доступний поки не всiм. Проте, варто звернути увагу на тенденцiю застосування технологiй глобальних комп'ютерних мереж у розробцi ПЛРЖС.

Розумною альтернативою використанню WebFiTTER i застосування пакета WebPack, що дозволяi працювати з CPLD XC9500 i CoolPLD, уведення опису проекту можливо як за допомогою схемного редактора, так i з використанням мов опису апаратури ABEL i VHDL. Можливе програмування пристроiв безпосередньо в системi з використанням апаратного завантажника Xсhecker. На жаль, в WebPack поки вiдсутня опцiя моделювання алгоритмiв, описаних за допомогою VHDL, пiдтримуiться тiльки лише синтез. Даний пакет можна ВлскачатиВ» iз сайту фiрми Xilinx.

Таблиця 1. Основнi характеристики системи WebFITTER

| Пiдтримуванi пристроi | XC9500 (5V), XC9500XL (3.3V), XC9500 (2.5V) |

| Спосiб опису проекту | VHDL, Verilog, ABEL, EDIF, TDF, XNF |

| Завдання обмежень на проект | Визначаiться користувачем |

| Вихiднi данi | Звiт про часовi параметри проекту (timing report), звiт про трасування (fitter report), файл програматора (programming file) у форматi JEDEC, убудована модель для моделювання (timing simulation model) у форматi VHDL, Verilog, EDIF |

Вместе с этим смотрят:

GPS-навигация

GPS-прийомник авиационный

IP-телефония и видеосвязь

IP-телефония. Особенности цифровой офисной связи

Unix-подобные системы