Система управления установкой для измерения влажности и давления

Реферат

Курсовой проект направлен на создание системы управления установкой для измерения влажности и давления, сочетающей в себе точность работы и доступность элементной базы.

В ходе работы над курсовым проектом были выполнены следующие пункты:

- Разработана структурная схема системы управления измерителем влажности и давления;

- Произведен выбор элементной базы;

- Разработана функциональная схема системы;

- Спроектирован алгоритм работы;

- Разработан фрагмент программного продукта.

Определения, обозначения и сокращения

ЖК тАУ жидкокристаллический;

АЦП тАУ аналогово-цифровой преобразователь;

ЦАП тАУ цифро-аналоговый преобразователь;

ОЗУ тАУ оперативное запоминающее устройство;

ИОН тАУ источник опорного напряжения;

TIC тАУ Time Interval Counter тАУ счетчик временных интервалов;

SPI тАУ Serial Peripheral Interface тАУ последовательный периферийный интерфейс;

TSSOP тАУ Thin Shrink Small Outline Package тАУ вид миниатюрного корпуса;

MSOP тАУ Mini Small Outline Package тАУ вид миниатюрного корпуса.

Введение

Регулирование и автоматизация многих промышленных процессов требует точного и достоверного измерения влажности. Управляемые микропроцессором датчики влажности и давления представляет собой универсальное решение для измерение влажности и давления в экстремальных условиях эксплуатации. Благодаря простоте обслуживания, обширному набору функций и возможности расширения эти датчики доказывает свою надежность в различных технологических процессах. Данные приборы используются в промышленных процессах сушки, системах контроля и управления, климатических установках стерильных и складских помещений, лабораториях и др.

Потребности различных отраслей промышленности покрываются за счет семи различных типов применения. Возможно использование датчиков совместно с прочным алюминиевым корпусом со степенью защиты IP 65,коротрый обеспечивает защиту датчиков от пыли и брызг воды. Корпус также обеспечивает электромагнитную совместимость при напряженности поля до 10 В/м. По конструкции датчики различаются на модели с настенным вариантом монтажа и модели с длиной кабеля 2, 5 или 10 м, позволяющего устанавливать датчики в вентиляционных каналах или других технологических линиях. Специальные варианты сенсоров позволяют использовать датчики в вакууме и при избыточном давлении от 0 до 100 бар и рабочей температуре до 180В°С. Первичные выходные значения датчиков представляют собой измерения давления и относительной влажности. Микропроцессор с помощью дополнительного программного обеспечения позволяет выполнять расчет абсолютных величин, таких как относительное давление в помещении, абсолютная влажность а (г/м³), содержание влаги х (г/кг), теплосодержание h (кДж/кг). Датчики имеют два аналоговых выхода, по которым можно в любой комбинации передавать измеренные значения. Имеется возможность масштабирования диапазона измерения и выходных сигналов в пределах заданных границ. Датчики могут оснащаться ЖК-дисплеем/ панелью управления, предназначенными для отображения измеряемых значений и выполнения различных операций, например, калибровки. Имеется также конфигурация с последовательным интерфейсом и возможность управления датчиком с компьютера, на котором установлена любая программа терминала (ОС Windows). Дополнительно вместо последовательного интерфейса датчики могут оборудоваться токовой петлей 20 мА, что позволяет подключать их к сети. Используемые сенсоры отличаются повышенной точностью, надежностью и стабильностью. Большое значение в технологических процессах имеет стойкость к загрязнениям частицами пыли и различными химическими веществами. Кроме того, с помощью дополнительной функции восстановления имеется возможность восстановления сенсора после воздействия высококонцентрированных химических веществ, которые могут повредить сенсоры. Восстановление выполняется с помощью программируемой процедуры кратковременного нагрева, во время которой с поверхности сенсора испаряются молекулы посторонних веществ.

1. Разработка структурной схемы

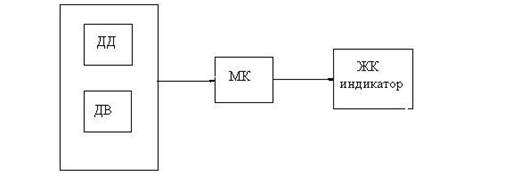

Структурная схема представлена на рисунке 1.1.

Рисунок 1.1 тАУ Структурная схема

Условные обозначения рисунка 1.1:

ДД тАУ датчик давления;

ДВ тАУ датчик влажности;

МК тАУ микроконтроллер.

2. Выбор элементной базы

2.1 Выбор микроконтроллера

В данной задаче будет использоваться микроконтроллер 51 семейства от фирмы Analog Devices ADuC 812.

Общие сведения о микроконтроллере ADuC812 [1]

ADuC812 - интегральная 12-разрядная система сбора информации, включающая в себя прецизионный многоканальный АЦП с самокалибровкой, два 12-разрядных ЦАП и программируемое 8-битное микропроцессорное ядро (совместимое с 8051, MCU). MCU поддерживается внутренними 8К FLASH ЭРПЗУ программ, 640 байт ЭРПЗУ памяти данных и 256 байт статической памяти данных с произвольной выборкой (RAM).

MCU поддерживает следующие функции: сторожевой таймер, монитор питания и канал прямого доступа к памяти для АЦП. Для мультипроцессорного обмена и расширения ввода/вывода имеются 32 программируемые линии, I2C, SPI и UART интерфейсы. Для гибкого управления в приложениях с низким потреблением в MCU и аналоговой части предусмотрены 3 режима работы: нормальный, холостой и дежурный. Продукт специфицирован для +3/+5В работы в индустриальном диапазоне температур и поставляется 52-выводном пластмассовом корпусе (PQFP).

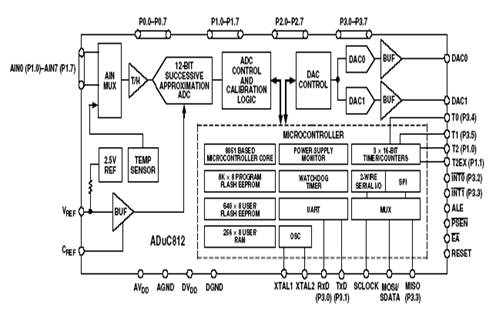

На рисунке 2.1 приводится функциональная блок схема используемого микроконтроллера.

Рисунок 2.1 тАУ Функциональная блок схема

На рисунке 2.2 приводится внешний вид корпуса микроконтроллера ADuC812.

Рисунок 2.2 тАУ Внешний вид корпуса ADuC812

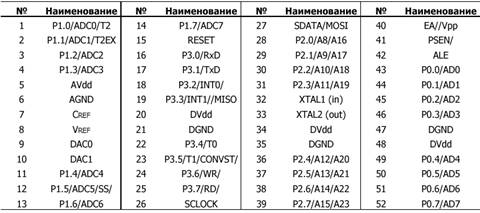

В таблице 2.1 приведено расположение контактов контроллера ADuC812.

Таблица 2.1 тАУ Расположение контактов ADuC812

Использование памяти данных

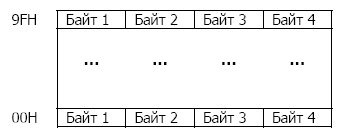

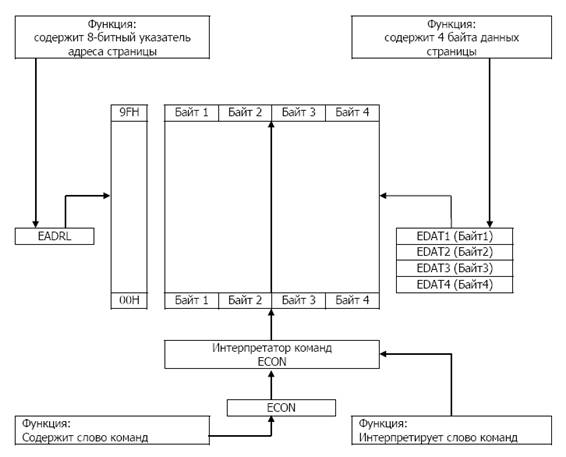

Память данных пользователя состоит из 640 байт, которые составляют 160 (от 00Н до 9FН) четырехбайтовых страниц, как показано на рисунке 2.3. Как и для прочей периферии, доступ к этой памяти производится через SFR регистры. Группа из 4-х регистров (EDATA1-4) используется для хранения данных четырех байт страницы из последнего обращения. EADRL используется для хранения адреса страницы, куда будет осуществляться доступ. И, наконец, ECON тАУ 8-разрядный регистр управления, в который записывается одна из пяти команд управления доступом к памяти, допускающие различные операции чтения, записи, стирания и верификации. Блок-схема регистрового интерфейса к памяти показана на рисунке 2.4.

Рисунок 2.3 тАУ Конфигурация FLASH/EE памяти пользователя

Рисунок 2.4 тАУ Управление FLASH/EE памятью пользователя

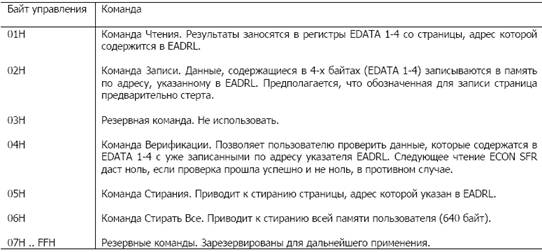

Для управления памятью используется регистр ECON, который является интерпретатором команд и в него можно записать одну из пяти чтения, программирования и стирания, как указано в таблице 2.2.

Таблица 2.2 тАУ Регистр управления памятью ECON

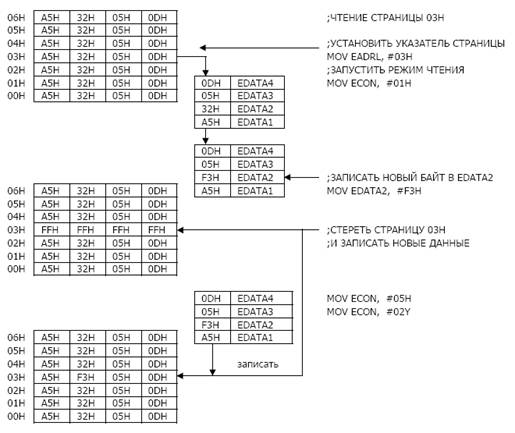

При использовании данная память может быть запрограммирована в составе системы побайтно, при этом, она предварительно должна быть стерта страничными блоками. Типовой цикл доступа к FLASH/EE памяти включает в себя установку адреса страницы доступа EADRL SFR, запись данных для программирования в EDATA 1-4 (в случае чтения - не записываются) и, наконец, запись команды в ECON, инициирующей действие в соответствие с таблицей 2.2.Следует отметить, что заданный режим работы инициируется по записи слова команды в ECON SFR. При этом микропроцессорное ядро переходит в холостой режим и находится там до тех пор, пока выполнение команды не завершится.На практике это означает, что даже если режим работы с FLASH/EE памятью инициируется двумя машинными циклами (инструкция MOV для записи в ECON SFR), следующая инструкция будет выполнена только после окончания цикла обслуживания FLASH/EE памяти (т.е. спустя 250 мкс или 20 мс). Это означает, что ядро не будет обслуживать запросы на прерывание до тех пор, пока операция с FLASH/EE памятью не завершится, хотя функции управления ядра периферией будет выполняться, как, например, продолжение счета времени/событий Счетчиками/Таймерами на протяжении всего псевдохолостого режима.

Для программирования одного байта в FLASH/EE памяти необходимо чтобы сначала этот байт был стерт, т.е. в ячейке записано FFH. Вследствие особенности архитектуры FLASH/EE памяти, стирание можно производить только для 1 страницы (минимум 4-байта) при инициировании Команды Стирания.

Пример процесса побайтного программирования графически показан на рисунке 2.5. В этом примере во второй байт на странице 03Н пользовательской FLASH/EE памяти записывается код F3H. Однако страница 03Н уже содержит данные в четырех байтах, а пользователю требуется изменить только содержимое одного байта; всю страницу следует сначала прочитать с тем, чтобы можно было стереть содержимое этой страницы без потери данных. Затем новый байт записывается в EDATA SFR вслед за циклом стирания. Если попытаться начать цикл Программирования (ECON=02H), не выполняя цикла Стирания (ECON=05H), то в этом случае будут модифицированы только те разряды, которые содержат единицы, т.е. для правильной записи массива необходимо выполнить его предварительное стирание. Следует отметить, что циклы стирания страницы и всей памяти имеют одинаковую длительность тАУ 20 мс.

Рисунок 2.5 тАУ Пример программирования байта памяти пользователя

Ассемблерный код приведенного примера выглядит следующим образом:

MOV EADRL, #03H ;Установка указателя страницы MOV ECON, #01H ;Команда чтения страницы MOV EDATA2, #0F3H ;Запись нового байта MOV ECON, #02H ;Команда стирания страницы MOV ECON, #05H ;Команда программирования страницы

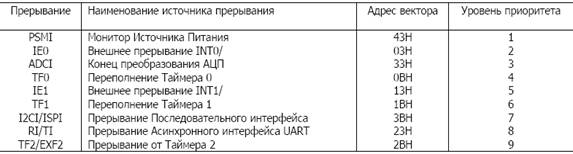

ADuC812 обеспечивает восемь источников и два уровня прерываний. В таблице 2.3 приводятся адреса векторов прерываний и уровни приоритетов.

Таблица 2.3 тАУ Адреса векторов прерываний

Для обработки любого из прерываний следует предпринять следующие три действия:

1. Расположить процедуру обслуживания прерывания по адресу соответствующего прерывания.

2. Установить бит разрешения всех прерываний (ЕА) Вл1В» в регистре IE SFR.

3. Установить бит разрешения индивидуального прерывания в Вл1В» в IE или IE2 SFR.

Для разрешения и установки приоритета различных прерываний используются три регистра SFR.

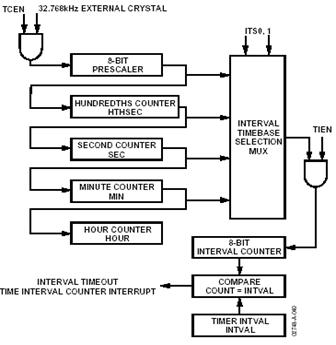

Счетчик временных интервалов TIC

Важной особенностью прибора является наличие счетчика временных интервалов (TIC), позволяющего отсчитывать временные интервалы большие, чем способны стандартные таймеры тАУ длительностью до 255 часов. Упрощенная схема TIC представлена на рисунке 2.6.

Работа с TIC осуществляется при помощи следующих регистров:

TIMECON тАУ регистр управления TIC (назначение битов TIMECON и набор режимов работы представлены в таблице 2.4);

INTVAL тАУ регистр пользовательского временного интервала;

HTHSEC тАУ регистр сотых долей секунды (инкрементируется через каждую 1/128 секунды, после значения 127 сбрасывается, инкрементируя регистр SEC);

SEC - регистр секунд (после значения 59 сбрасывается, инкрементируя регистр MIN);

MIN тАУ регистр минут (после значения 59 сбрасывается, инкрементируя регистр HR);

HOUR тАУ регистр часов (сбрасывается на 0 после значения 23 или 255 тАУ в зависимости от режима работы).

Рисунок 2.6 - Упрощенная схема TIC

Таблица 2.4тАУ Назначение битов TIMECON

№ бита | обозначение | назначение |

| 7 | -- | Зарезервирован |

| 6 | TFH | Бит выбора 24-часового режима (Twenty-Four Hour Select Bit). Если установлен тАУ регистр HOUR сбрасывается после значения 23, иначе тАУ после значения 255. |

| 5-4 | TS1, TS0 | Биты выбора единиц измерения интервалов (Interval Timebase Selection Bits). Определяют частоту обновления 8-битного счетчика временных интервалов. | TS1 | TS0 | | | 0 | 0 | 1/128 секунды | | 0 | 1 | секунды | | 1 | 0 | минуты | | 1 | 1 | часы |

|

| 3 | STI | Бит единичного временного интервала (Single Time Interval Bit). Устанавливает режим единичного временного интервала, когда бит TIEN сбрасывается при первом таймауте. |

| 2 | TII | Бит прерывания TIC (TIC Interrupt Bit). Устанавливается когда значение 8-битного счетчика временных интервалов совпадает с INTVAL. |

| 1 | TIEN | Бит включения 8-битного счетчика временных интервалов (Time Interval Enable Bit). |

| 0 | TCEN | Бит включения таймера (Time Clock Enable Bit). |

Вместе с этим смотрят:

GPS-навигация

GPS-прийомник авиационный

IP-телефония и видеосвязь

IP-телефония. Особенности цифровой офисной связи

Unix-подобные системы