Цифро-аналоговi перетворювачi

Курсова робота

Цифро-аналоговi перетворювачi

2008р.

1. Загальнi вiдомостi

Цифро-аналоговий перетворювач (ЦАП) призначений для перетворення числа у виглядi двiйкового коду у напругу або струм, пропорцiйний значенню цифрового коду. Схемотехнiка ЦАП дуже рiзноманiтна. На рис.1 показана класифiкацiя схем ЦАП за схемотехнiчними показниками.

Рис.1 Класифiкацiя схем ЦАП

Окрiм того, iнтегральнi мiкросхеми ЦАП мають класифiкацiю за такими ознаками:

В· По вигляду цифрового сигналу: або з токовим виходом, або у виглядi напруги.

В· По типу цифрового iнтерфейсу: з послiдовним введенням, або з паралельним введенням вхiдного коду.

В· По кiлькостi ЦАП на кристалi: одно канальнi або багатоканальнi.

В· По швидкодii: помiрноi або високоi швидкодii.

2. Послiдовнi ЦАП

ЦАП з широтно-iмпульсною модуляцiiю

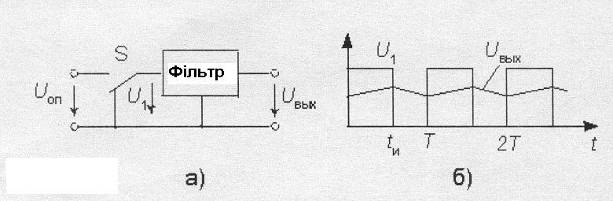

Дуже часто ЦАП входить у склад мiкропроцесорних систем. В такому випадку, якщо не потрiбна висока швидкодiя, цифро-аналогове перетворення може бути дуже просто здiйснене за допомогою широтно-iмпульсноi модуляцii (ШРЖМ). Схема ЦАП з ШРЖМ наведена на рис.2.

Рис.2. а) Схема послiдовного ЦАП; б) дiаграма напруг.

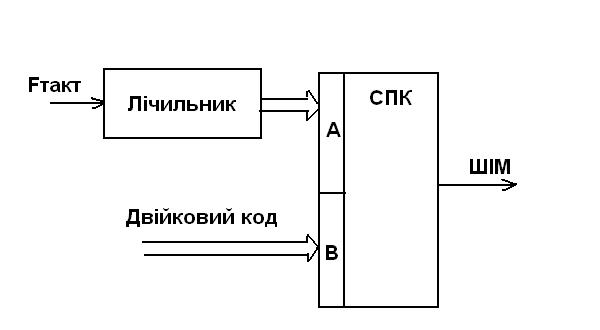

Вихiд ШРЖМ-модулятора керуi роботою ключа S. В залежностi вiд коду формуiться iмпульс ШРЖМ, тривалiсть якого прямо пропорцiйна значенню цифрового коду. Схема формування показана на рис.3. Код на виходi лiчильника лiнiйно зростаi з кожним iмпульсом тактовоi частоти Fтакт. Поки цей код менший за двiйковий код, на виходi.

Рис.3. Схема формування коду

Схеми порiвняння кодiв (СПК) буде сигнал логiчноi одиницi. Як тiльки код лiчильника зрiвнюiться з вiйковим кодом, на виходi СПК встановлюiться логiчний нуль. Цей iмпульс керуi ключем S. Фiльтр у схемi рис.2а видiляi середнi значення напруги, як це показане на рис.2б. Ця схема забезпечуi майже iдеальну лiнiйнiсть перетворення i не маi прецизiйних елементiв. РЗi головний недолiк тАУ низька швидкодiя.

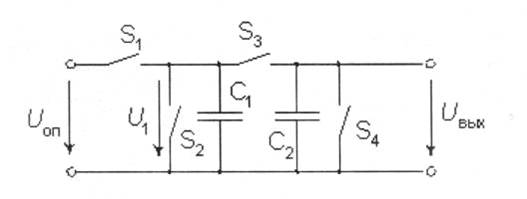

ЦАП на перемикаiмих конденсаторах

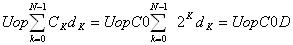

У попереднiй схемi потрiбно 2N тактiв iмпульсiв синхронiзацii. В схемi рис.4 для цього потрiбно значно менше тактiв.

Рис. Схема ЦАП на перемикаiмих конденсаторах.

В цiй схемi iмностi конденсаторiв С1 та С2 рiвнi. Перед початком циклу перетворення конденсатор С2 розряджаiться ключем S Вхiдне вiйкове слово задаiться у виглядi послiдовного коду. Його перетворення здiйснюiться послiдовно, починаючи з молодшого розряду d0. кожен такт перетворення складаiться з двох полу тактiв. В першому полутактi конденсатор С1 заряджаiться до опорноi напруги Uоп при d0=1 за допомогою замикання ключа S1, або розряджаiться до нуля при d0=0 за допомогою замикання ключа S2. На другому полу тактi при розiмкнутих ключах S1, S2 та S4 замикаiться ключ S3, що викликаi дiлення заряду навпiл мiж С1 та С2. В результатi одержимо:

U1(0) = Uвих(0) = (d0/2)Uоп.

Доки на конденсаторi С2 зберiгаiться заряд, процедура зарядження конденсатора С1 повинна бути повторна для наступного розряду d1 вхiдного слова. Пiсля нового циклу перезаряджання напруга на конденсаторах буде

Uвих(1) = U1(1) = [(d1 + d0/2)Uоп]/2 = [(2d1 + d0)Uоп]/

Таким же чином виконуiться перетворення для iнших розрядiв слова. В результатi для N-розрядного ЦАП вихiдна напруга буде дорiвнювати

Uвих(N-1) + U(1) =  =

=  .

.

Якщо потрiбно зберегти результат перетворення будь-який тривалий час, до виходу схеми треба пiдключити ПВЗ. Пiсля закiнчення циклу перетворення потрiбно провести цикл вибирання, перевести ПВЗ в режим збереження i знову почати перетворення.

Таким чином ця схема виконуi перетворення вхiдного коду за 2N квантiв, що значно менше, нiж у ЦАП з ШРЖМ. Тут потрiбно лише два узгоджених конденсатори невеликоi iмностi. Конфiгурацiя аналоговоi частини схеми не залежить вiд розрядностi перетворюваного коду. Але по швидкодii послiдовний ЦАП значно уступаi паралельним ЦАП, що обмежуi сферу його застосування.

3. Паралельнi ЦАП

ЦАП з сумуванням вагових струмiв

Бiльшiсть схем паралельних ЦАП заснованi на сумуваннi струмiв, сила кожного з яких пропорцiйна вазi цифрового вiйкового розряду, причому повиннi сумуватись тiльки суми розрядiв, значення яких дорiвнюi 1. Наприклад, потрiбно перетворити двiйковий 4-розрядний код в аналоговий сигнал струму. У старшого значущого розряду (СЗР) вага дорiвнюi 23 = 8, у третього 22 = 4, у другого 21 = 2 i у молодшого (МЗР) 20 = 1. Якщо вага МЗР дорiвнюi струму I1 = 1 мА, то I2 = 2 мА, I3 = 4 мА, I4 = 8 мА. Наприклад, коду 1001 вiдповiдаi струм Iвих = 9 мА. Тому потрiбна схема, що забезпечуi генерацiю та комутацiю по заданих законах точних вагових струмiв. Найпростiша схема показана на рис.5.

Рис.5. Цап з сумуванням вихiдних струмiв

Опори резисторiв вибирають так, щоб при замкнених ключах через них протiкав струм вiдповiдний вазi розряду Ключ повинен бути замкнений тодi, коли вiдповiдний йому бiт вхiдного слова дорiвнюi одиницi. Вихiдний струм визначаiться спiввiдношенням

Iвих =  Ва= UопD/R0.

Ва= UопD/R0.

При високiй розрядностi ЦАП резистори, що задають струм, повиннi бути погодженi з високою точнiстю. Найбiльш жорсткi вимоги по точностi висуваються к резисторам старших розрядiв, оскiльки розкид в них не повинен перевищувати струму молодшого розряду. Тому розкид опору у к-му розрядi повинен бути меншим, нiж DR/R = 2-k.

З цiii вимоги виникаi, що розкид опору резистора, наприклад у 10-му розрядi не повинен перевищувати 0,05%.

Розглянута схема маi кiлька недолiкiв. По перше, при рiзних вхiдних кодах, струм, що споживаiться вiд джерела опорноi напруги (ДОН), буде рiзним, а це впливаi на величину вихiдноi напруги ДОН. По друге, значення опорiв вихiдних резисторiв можуть вiдрiзнятись у тисячi разiв, а це робить проблемною реалiзацiю цих резисторiв у напiвпровiдникових iнтегральних мiкросхемах. Окрiм того, значення опорiв старших розрядiв у багато розрядних цап може бути зiставленим з опором замкненого ключа, а це приведе до похибки перетворення. По трете, у цiй схемi до ключiв прикладаiться значна напруга, що ускладнюi iх реалiзацiю.

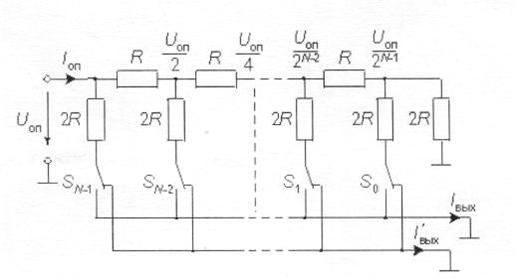

Цi недолiки усунутi у схемi ЦАП AD7520 (вiтчизняний аналог 572ПА1), що розроблений фiрмою Analog Devices. Ця схема показана на рис.6. У якостi ключiв тут використовуються МОН-транзистори.

Рис.6. Схема ЦАП з ключами

У цiй схемi завдання вагових коефiцiiнтiв ступенiв перетворювача здiйснюiться за посередництвом послiдовного дiлення опорноi напруги за допомогою резистивноi матрицi постiйного iмпедансу. головний елемент такоi матрицi i подiльник напруги, який повинен задовольняти наступнiй умовi: якщо вiн завантажений опором Rн, то його вхiдний опiр також повинен приймати значення Rн. Коефiцiiнт ослаблення кола a =U2/U1 при цьому завантаженнi повинен мати задане значення. При виконаннi цих умов одержуiмо наступнi вирази для опорiв

Uвих(N -1) = U1(N - 1) =  =

=

Rp = aRн/(1-a), Rs = (1 - a)Rн.

При вiйковому кодуваннi a = 0,5. Якщо покласти Rн = 2R, то Rs = R, a Rp = 2R.

Оскiльки у будь-якому положеннi перемикачiв Sk вони зтАЩiднують нижнi виводи резисторiв з загальною шиною схеми, джерело опорноi напруги навантажене на постiйний вхiдний опiр Rвх = R. Це гарантуi незмiннiсть опорноi напруги при будь-якому вхiдному кодi ЦАП. Нижнi виводи резисторiв 2R матрицi при будь-якому положеннi перемикачiв Sk зтАЩiднанi з загальною шиною через низький опiр замкнених ключiв, тодi напруги на ключах завжди невеликi. Це спрощуi побудову ключiв та схем керування ними та дозволяi використати опорну напругу з великого дiапазону напруг, у тому числi i рiзноi полярностi. Оскiльки вихiдний струм ЦАП залежить вiд Uоп линiйно. перетворювачi цього типу можна використовувати для множення аналогового сигналу (подаючи його на вхiд опорноi напруги) на цифровий код. Такi ЦАПи називають перемножуючими.

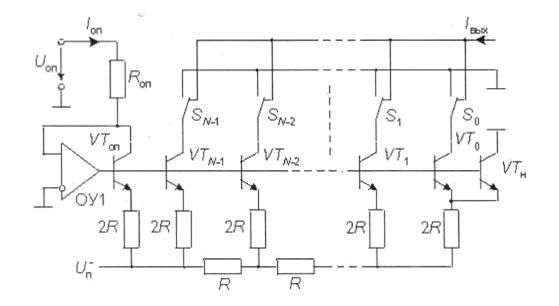

ЦАП на джерелах струму

ЦАП на джерелах струму маi бiльш високу точнiсть. На вiдмiну вiд попереднього варiанту, у якому ваговi струми формуються резисторами порiвняно невеликого опору, а тому залежать вiд опору ключiв на навантаження, у даному разi ваговi струми забезпечуються транзисторними джерелами струму, що мають високий динамiчний опiр. Спрощена схема такого ЦАП наведена на рис.7.

Ваговi струми формуються за допомогою резистивноi матрицi. Потенцiали баз транзисторiв однаковi, а щоб були рiвними i потенцiали емiтерiв усiх транзисторiв, площi РЖi емiтерiв роблять рiзними у вiдповiдностi до вагових коефiцiiнтiв. Правий резистор матрицi пiдключений не до загальноi шини, а до двох паралельно включених однакових транзисторiв VT0 та VTн, у результатi чого струм через VT0 дорiвнюi половинi струму через VT1.

ВаРис.7. ЦАП на джерелах струму

ВаРис.7. ЦАП на джерелах струму

Вихiдна напруга для резистивноi матрицi створюiться за допомогою опорного транзистора VTоп та операцiйного пiдсилювача ОУ1, вихiдна напруга якого встановлюiться такою, що колекторний струм транзистора VTоп приймаi значення Iоп. Вихiдний струм для N-розрядного ЦАП

Iвих = Iоп D/2N.

Формування вихiдного сигналу у виглядi напруги

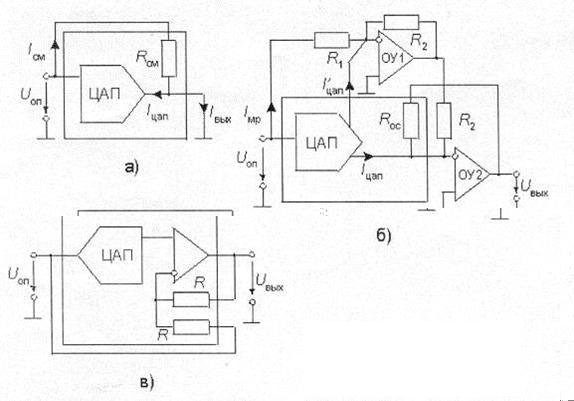

РЖснуi декiлька способiв формування вихiдноi напруги для ЦАП з сумуванням вихiдних струмiв. Два з них показанi на рис.8.

Рис.8. а) Формування вихiдноi напруги за допомогою операцiйного пiдсилювача; б) формування вихiдноi напруги за допомогою резистора.

На рис.8,а наведена схема з перетворювачем струму в напругу на операцiйому пiдсилювачi. Ця схема придатна для усiх ЦАП зi струмовим виходом. Оскiльки плiвковi резистори, що визначають ваговi струми ЦАП мають значний температурний коефiцiiнт опору, резистор зворотнього звтАЩязку треба виготовляти на кристалi ЦАП та в тому ж технологiчному процесi, що звичайно i робиться. Це дозволить знизити температурну нестабiльнiсть перетворювача у 300..400 разiв. Вихiдна напруга схеми на рис.8,а

Uвих = -RосI вих = -RосUопD/R2N.

Звичайно, опiр резистора зворотнього звтАЩязку Roc = R. У такому випадку

Звих = -UопD/2N.

Бiльшiсть моделей ЦАП мають велику вихiдну iмнiсть. Наприклад, у AD7520 вона в залежностi вiд вхiдного коду складаi величину 30..120 пФ.

Для ЦАП на джерелах струму перетворення вихiдного струму у напругу може бути зроблено за допомогою резистора (рис.8,б). У цiй схемi амплiтуда вихiдноi напруги повинна бути невеликою (не бiльше В±1 В). Такий режим забезпечуiться при малому опорi навантаження Rн = 1 кОм.

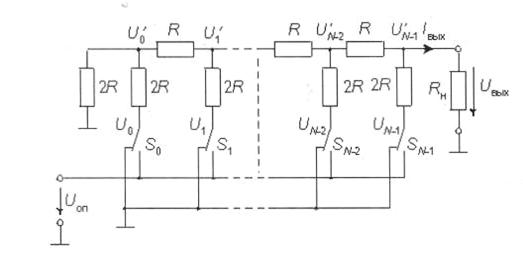

Для ЦАП з МОН-ключами. щоб одержати вихiдний сигнал у виглядi напруги, можна використати iнверсне включення резистивноi матрицi (рис.9).

Рис.9. РЖнверсне включення резистивноi матрицi.

Вихiдна напруга такого ЦАП

Uвих =  Ва.

Ва.

В особистому випадку, Rн = Вµ Uвих =  Ва.

Ва.

Недолiками цiii схеми i: велике спадання напруги на ключах, змiнне навантаження джерела опорноi напруги та значний вихiдний опiр.

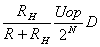

Паралельний ЦАП на перемикаiмих конденсаторах

Основою ЦАП цього типу i матриця конденсаторiв, iмностi яких спiввiдносяться як цiлi ступенi двiйки. Схема простого варiанту такого перетворювача наведена на рис.10.

Рис.10. Паралельний ЦАП на перемикаiмих конденсаторах

РДмнiсть К-го конденсатору матрицi визначаiться спiввiдношенням: Ск = 2КС0.

Цикл перетворення складаiться з двох фаз У першiй фазi ключi S0тАжSN-1 знаходяться у лiвiй позицii. Ключ скидання Sсб замкнений. При цьому усi конденсатори розрядженi. У другiй фазi ключ скидання Sсб розмикаiться. Якщо k-й бiт вхiдного N-розрядного слова dk = 1, то вiдповiдний ключ Sk перемикаiться у праву позицiю. пiдключаючи нижню обкладинку конденсатору до джерела опорноi напруги, або залишаiться у лiвiй позицii, якщо dk = 0.Сумарний розряд конденсаторiв матрицi з урахуванням Ск = 2КС0, складаi:

q =  .

.

Такий же заряд одержуi i конденсатор С в колi зворотного звтАЩязку операцiйного пiдсилювача. При цьому вихiдна напруга ОУ складе:

Uвих = -UopC0D/C.

Для збереження результату перетворення (постiйноi напруги) на протязi кiлькох рокiв к виходу кiлькох ЦАП цього типу потрiбно пiдключати пристрiй вибiрки-збереження. Зберiгати результат тривалий час неможливо, тому такi ЦАП застосовуються в основному у составi АЦП. РЖнший недолiк тАУ велика площа кристалу мiкросхеми, котру займаi така схема.

ЦАП з сумуванням напруг

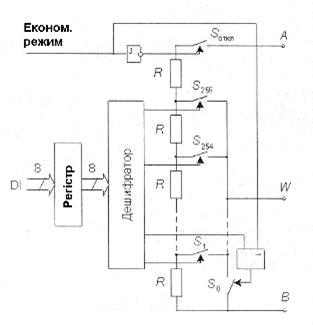

Схема 8-розрядного ЦАП з сумуванням напруг, що виготовляiться у виглядi мiкросхеми, показано на рис.11.

Рис.11. ЦАП з сумуванням напруг

Основу перетворювача складаi ланцюг з 256 резисторiв рiвного опору, що зтАЩiднанi послiдовно. Вивiд W через ключi S0тАжS256 може пiдключатись до будь-якоi точки цього кола в залежностi вiд вхiдного числа. Вхiдний двiйковий код D перетворюiться дешифратором 8х256 в унiтарний позицiйний код, що безпосередньо керуi ключами. Якщо прикласти напругу UAB мiж виводами А i В, то напруга мiж виводами Wi В складе:

UWB = UABD.

Достоiнство даноi схеми тАУ мала диференцiйна нелiнiйнiсть та гарантована монотоннiсть характеристики перетворення. РЗi можна використовувати як резистор, що пiдстроюiться цифровим кодом. При подачi активного рiвня на вхiд тАЮЕконом. режимтАЭ маi мiсце розмикання ключа Sоткл, та замикання ключа S0. У наш час випускаються ЦАП такого типу на 12 розрядiв, наприклад, AD5321.

РЖнтерфейси ЦАП

Важливу частину ЦАП складаi цифровий iнтерфейс тАУ схеми, що забезпечують звтАЩязок керуючих входiв ключiв з джерелами цифрових сигналiв. Структура цифрового iнтерфейсу безпосередньо визначаi спосiб пiдключення ЦАП до джерела вхiдного коду, наприклад, мiкропроцесору та мiкро контролеру. Властивостi цифрового iнтерфейсу безпосередньо впливають i на форму кривоi сигналу на виходi ЦАП. Так, неодночаснiсть надходження бiтiв вхiдного слова на керуючi входи ключiв перетворювача призводить до появи вузьких викидiв, тАЮголоктАЭ у вихiдному сигналi при змiнi коду.

При керуваннi ЦАП вiд цифрових пристроiв з жорсткою логiкою керуючi коди ключiв ЦАП можуть бути безпосередньо пiдключенi до вихiдних виводiв цифрових пристроiв, тому у багатьох моделях ЦАП, особливо бiльш раднiших (572ПА1 та iн.) суттiва цифрова частина вiдсутня. Якщо ЦАП входить у склад мiкропроцесорноi системи та одержуi вхiдний код вiд шини даних, то його потрiбно оснастити пристроями, що приймають вхiдне слово вiд шини даних, та керувати ключами ЦАП i зберiгати слово до надходження нових даних. В залежностi вiд способу завантаження вхiдного слова в ЦАП роздiляють перетворювачi з паралельним та послiдовним iнтерфейсами вхiдних даних.

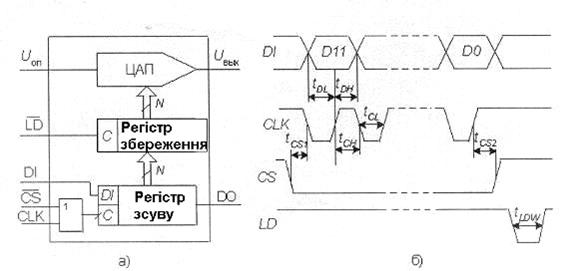

ЦАП з послiдовним iнтерфейсом вхiдних даних

Такий ЦАП маi на кристалi окрiм власне ЦАП додатково також послiдовний регiстр завантаження, паралельний регiстр збереження та керуючу логiку (рис.12,а).

Рис.12. а) ЦАП з послiдовним iнтерфейсом; б) дiаграми напруг.

При активному рiвнi сигналу CS (лог.тАЭ0тАЭ) вхiдне слово довжини N (що дорiвнюi розрядностi ЦАП) завантажуiться по лiнii DI в регiстр зсуву пiд керуванням тактовоi послiдовностi CLK/ Пiсля закiнчення завантаження, виставивши на лiнiю LD активний рiвень, вхiдне слово записують у регiстр збереження, виходи якого безпосередньо керують ключами ЦАП. Для того, щоб мати можливiсть передавати по однiй лiнii даних вхiднi коди у декiлька ЦАП, останнiй розряд регiстру зсуву у багатьох моделей ЦАП з послiдовним iнтерфейсом зтАЩiднуiться з виводом D0. Цей вивiд зтАЩiднуiться зi входом DI наступного ЦАП i т.i.

Як приклад на рис.12,б розглянута часова дiаграма, що вiдтворюi процес завантаження вхiдного слова у ЦАП AD7233. Мiнiмально досяжнi iнтервали часу (порядку 50 нс), що позначенi на часових дiаграмах, вказуються в технiчнiй документацii на мiкросхему.

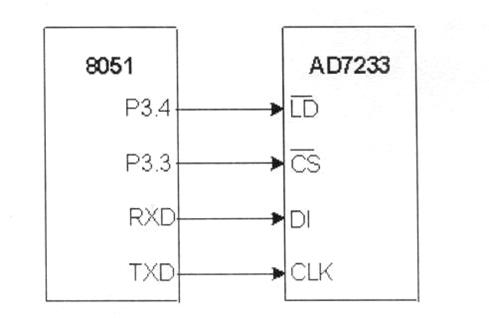

На рис.13 наведений варiант схеми пiдключення перетворювача з послiдовним iнтерфейсом до мiкроконтролера (МК). На час завантаження вхiдного слова в ЦАП через послiдовний порт мiкро контролера, до котрого можуть бути також пiдключенi iншi приймачi, на вхiд CS (вибiр кристалу) подаiться активний рiвень з однiii з лiнiй введення-виводу МК. пiсля закiнчення завантаження МК мiняi рiвень на входi CS, як це показане на рис.12,б, та виставивши активний рiвень на входi LD ЦАП, забезпечуi пересилку вхiдного коду з регiстра зсуву ЦАП в регiстр збереження. Час завантаження залежить вiд тактовоi частоти МК i звичайно близько 1 мкс. Мiнiмальна кiлькiсть лiнiй звтАЩязку з ЦАП забезпечуiться двох провiдним iнтерфейсом I2C.

Рис.13. Пiдключення схеми перетворювача до мiкроконтролера

ЦАП з паралельним iнтерфейсом вхiдних даних

На N входiв даних N-розрядного ЦАП подаiться все вхiдне слово. РЖнтерфейс такого ЦАП маi два регiстри збереження та схему керування (рис.14,а).

Рис.1 а) ЦАП з паралельним iнтерфейсом; б) дiаграма напруг

Два регiстри збереження потрiбнi, якщо пересилання вхiдного коду в ЦАП та установка вихiдного аналогового сигналу, що вiдповiдаi цьому слову, повиннi бути роздiленi в часi. Подача на вхiд асинхронного скиду CLR сигналу низького рiвня призводить до занулення першого регiстру, i вiдповiдно вихiдноi напруги ЦАП.

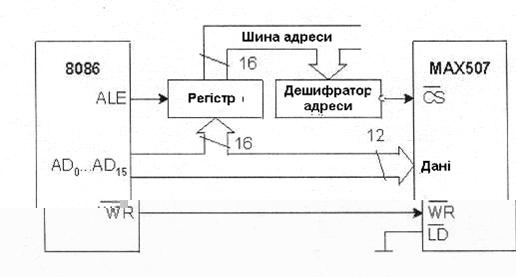

Приклад блок-схеми пiдключення 12-розрядного ЦАП МАХ507 до 16-розрядного мiкропроцесора наведений на рис.15. Процесор надсилаi вхiдний код в ЦАП як у комiрку памтАЩятi даних. Спочатку з шини адреса-данi поступаi адреса ЦАП, яка фiксуiться регiстром по командi з виходу ALE мiкропроцесора i, пiзнiше, пiсля дешифрацii активiзуi активiзуi вхiд CS ЦАПю Услiд за цим МП подаi на шину адреса-данi вхiдний код ЦАП, а потiм сигнал запису на вхiд WR (див. рис.14,б).

Рис.15. Пiдключення ЦАП до мiкропроцесору.

5. Параметри ЦАП

При послiдовному наростаннi значень вхiдного цифрового сигналу D(t) вiд 0 до 2N-1 через одиницю молодшого розряду (ОМР) вихiдний сигнал Uвих(t) утворюi схiдчасту криву. Таку залежнiсть звичайно називають характеристикою перетворення ЦАП. У вiдсутностi апаратних похибок середнi точки розмiщенi на iдеальнiй прямiй 1 рис.16, якiй вiдповiдаi iдеальна характеристика перетворення.

Рис.16. РЖдеальна характеристика перетворення

Реальна характеристика перетворення може суттiво вiдрiзнятись вiд iдеальноi розмiрами та формою ступенiв а також розмiщенням на площинi координат. Для кiлькiсного опису цих розходжень iснуi цiлий ряд параметрiв.

Статичнi параметри

Роздiльна здатнiсть тАУ прирощення Uвих при перетвореннi сумiжних значень Dj, що вiдрiзняються на ОМР. Це прирощення i шагом квантування. Для вiйкових кодiв перетворення номiнальне значення шагу квантування h = Uпш/(2N-1), де Uпш тАУ номiнальна максимальна вихiдна напруга ЦАП (напруга повноi шкали), N тАУ розряднiсть ЦАП. Чим бiльша розряднiсть перетворювача, тим вища його роздiльна здатнiсть.

Похибка повноi шкали тАУ вiдносна рiзниця мiж реальним та iдеальним значеннями границi шкали перетворення при вiдсутностi змiщення нуля:

dпш = eпш 100%/Uпш.

РД мультиплiкативною складовою повноi похибки. РЖнколи ii указують вiдповiдним числом ОМР.

Похибка змiщення нуля тАУ значення Uвих, коли вхiдний код ЦАП дорiвнюi нулю. РД адитивною складовою повноi похибки. Звичайно указуiться в мiлiвольтах або в процентах вiд повноi шкали:

dсм = eсм 100%/Uпш.

Нелинiйнiсть тАУ максимальне вiдхилення реальноi характеристики перетворення Uвих(D) вiд оптимальноi (лiнiя 2 на рис.16). Оптимальна характеристика знаходиться емпiрично так, щоб мiнiмiзувати значення похибки нелинiйностi. Нелинiйнiсть звичайно визначаiться у вiдносних одиницях, але у довiдкових даних наводиться також i в ОМР. Для характеристики, наведеноi на рис.16

dл = ej 100%/Uпш.

Диференцiйна нелинiйнiсть тАУ максимальна змiна (з урахуванням знаку) вiдхилення реальноi характеристики перетворення Uвих(D) вiд оптимальноi при переходi вiд одного значення вхiдного коду до iншого сумiжного значення. Звичайно визначаiться у вiдносних одиницях або ОМР. Для характеристики, наведеноi на рис.16:

dдл = (ej + e(j+1))100%/Uпш.

Монотоннiсть характеристики перетворення тАУ зростання або зменшення вихiдноi напруги ЦАП Uвих при зростаннi або зменшеннi вхiдного кода D. Якщо диференцiйна нелинiйнiсть бiльша за вiдносний шаг квантування h/Uпш, то характеристика перетворення немонотонна.

Температурна нестабiльнiсть ЦАП характеризуiться температурними коефiцiiнтами похибки повноi шкали та похибки змiщення нуля.

Похибка повноi шкали та змiщення нуля можуть бути усуненi калiбровкою (пiдстройкою). Похибки нелинiйностi простими засобами усунути неможливо.

Динамiчнi параметри

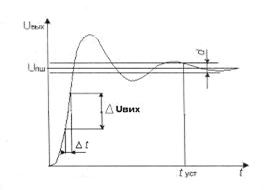

Динамiчнi параметри ЦАП визначаються по змiнi вхiдного сигналу при стрибковiй змiнi вхiдного коду, звичайно вiд значення тАЮусi нулiтАЭ до значення тАЮусi одиницiтАЭ (рис.17).

Рис.17. Динамiчнi параметри

Час встановлення тАУ iнтервал часу вiд моменту змiнення вхiдного коду (на рис.17 t=0) до моменту, коли у останнiй раз виконуiться рiвнiсть

Uвих тАУ Uпш = d/2.

Швидкiсть наростання тАУмаксимальна швидкiсть змiни Uвих(t) пiд час перехiдного процесу. Визначаiться як вiдношення прирощення DUвих до часу t, за який це прирощення здiйснилось. звичайно вказуiться у технiчних характеристиках ЦАП з вихiдним сигналом у виглядi напруги. У ЦАП з вихiдним сигналом у виглядi струму цей параметр у великiй мiрi залежить вiд типу вихiдного операцiйного пiдсилювача.

Для перемножуючих ЦАП з виходом у виглядi напруги часто зазначаiться частота одиничного пiдсилення та смуга пропущення по потужностi. якi в основному визначаються властивостями вихiдного пiдсилювача.

Шуми ЦАП

Шум на виходi ЦАП може зтАЩявлятись по рiзним причинам, що викликаються фiзичними процесами у напiвпровiдникових пристроях. Для оцiнки якостi ЦАП з високою роздiльною здатнiстю прийнято використовувати поняття середньоквадратичного значення шуму. Вiн вимiрюiться звичайно у нВ/(Гц)0,5 в заданiй смузi частот.

Викиди (iмпульснi перешкоди) тАУ крутi короткi сплески або провали у вихiднiй напрузi, що виникають пiд час змiни значень вхiдного коду за рахунок несинхронностi замикань та розмикань аналогових ключiв у рiзних розрядах ЦАП. Наприклад, якщо при переходi вiд значення коду 011..111 до значення 100..000 ключ самого старшого розряду ЦАП з сумуванням вагових струмiв вiдкриiться пiзнiше, нiж закроються ключi молодших розрядiв, то на виходi ЦАП деякий час буде iснувати сигнал, що вiдповiдаi коду 000..000.

Викиди характернi для швидкодiючих ЦАП, де зведенi до мiнiмуму iмностi, якi могли б iх згладити. Радикальним способом придушення викидiв i використання пристроiв вибiрки та збереження. Викиди оцiнюються по iх площi (в В*с).

6. Застосування ЦАП

Схеми застосування ЦАП вiдносяться не тiльки до галузi перетворення код-аналог. Користуючись iх властивостями можна визначити добуток двох або бiльше сигналiв, будувати подiльники функцiй, аналоговi ланки, що керуються вiд мiкроконтролерiв, такi як атенюатори, iнтегратори. Важливою галуззю застосування ЦАП i також генератори сигналiв будь-якоi форми. Нижче розглянутi деякi схеми обробки сигналiв, що вмiщають у себе ЦАП.

Обробка чисел, що мають знак

Ранiше при описi ЦАП вхiдна цифрова iнформацiя представлялась у виглядi чисел натурального ряду (унiполярних). Обробка цiлих чисел (бiполярних) маi деякi особливостi. Звичайно двiйковi цiлi числа представляються з використанням додаткового коду. Таким шляхом за допомогою восьми розрядiв можна представити числа у дiапазонi вiд -128 до +127. При вводi чисел у ЦАП цей дiапазон змiщують до 0..255 шляхом додавання числа 128. Числа, що бiльшi за 128, при цьому визначаються як позитивнi, а числа, що меншi за 128 тАУ негативнi. Середнi число 128 вiдповiдаi нулю. Таке представлення чисел зi знаком називаiться змiщеним кодом. Додавання числа , що складаi половину повноi шкали даноi розрядностi (у нашому прикладi це 128) можна легко виконати шляхом iнверсii старшого (знакового) розряду. У табл.1 це iлюструiться.

Таблиця 1

| Десятковий | Додатковий | Змiщений | Аналог I/Iмакс |

127 1 0 -1 -127 -128 | 01111111 00000001 00000000 11111111 10000001 10000000 | 11111111 10000001 10000000 01111111 00000001 00000000 | 127/255 1/255 0 -1/255 -127/255 -128/255 |

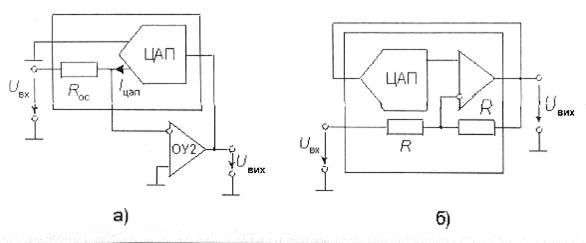

Щоб одержати вихiдний сигнал з правильним знаком, потрiбно здiйснити зворотне змiщення шляхом вiднiмання струму або напруги, що складають половину шкали перетворювача. Для рiзних типiв ЦАП це можна зробити рiзними способами. Наприклад, у ЦАП на джерелах струму, дiапазон змiни опорноi напруги обмежений. причому вихiдна напруга маi полярнiсть зворотну полярностi опорноi напруги. У цьому випадку бiполярний режим найбiльш просто реалiзуiться включенням додаткового резистора змiщення Rcм мiж виходом ЦАП та входом опорноi напруги (рис.18,а) Резистор Rcм виготовляiться на кристалi мiкросхеми. Його опiр вибраний таким, щоб струм РЖсм складав половина максимального значення вихiдного струму ЦАП.

Рис.18. а) схема на одному резисторi; б) схема з операцiйним пiдсилювачем; в) схема на iнверснiй резистивнiй матрицi.

В принципi аналогiчно можна вирiшити задачу змiщення вихiдного струму i для ЦАП на МОН-ключах. Для цього потрiбно про iнвертувати опорну напругу, а потiм сформувати з тАУUоп струм змiщення, який потрiбно вiдняти вiд вихiдного струму ЦАП. Але для збереження температурноi стабiльностi краще забезпечити формування струму змiщення безпосередньо у ЦАП. Для цього у схему рис.18,а вводять другий операцiйний пiдсилювач, а другий вихiд ЦАП пiдключають до входу цього пiдсилювача (рис.18,б).

Другий вихiдний струм ЦАП

IтАЩвих = Iвх тАУ Iвих тАУ Uоп/R·2N= Uоп(2N-1)/R·2N тАУ Iвих.

На входi операцiйного пiдсилювача струм IтАЩвих сумуiться зi струмом Iмр, що вiдповiдаi одиницi молодшого розряду вхiдного коду. Сумарний струм iнвертуiться. Струм, що проходить через резистор зворотнього звтАЩязку Rос ОУ2 складаi

Iос = Iвх тАУ Iвих тАУ Uоп/R·2N = 2(Iвих тАУ Uоп/2R),

або

Iос = Uоп/R·2N(D тАУ 2N-1).

Якщо D=0, Iос = - Uоп/R, а при D = 2N тАУ 1, Iос = (Uоп/R)(2N-1 тАУ 1)/2N-1.

Це у випадку N=8 з точнiстю до множника 2 спiвпадаi з даними таблицi, з урахуванням того, що для перетворювача на МОН-ключах максимальний вихiдний струм

Iмакс = (Uоп/R)(2N-1 тАУ 1)/2N-1.

Якщо резистори R2 добре узгодженi по опору, то абсолютна змiна iх величин при коливаннях температури не впливаi на вихiдну напругу схеми.

У ЦАП з вихiдним сигналом у виглядi напруги, побудованих на iнверснiй резистивнiй матрицi (рис.9), можна бiльш просто реалiзувати бiполярний режим (рис.18,в). Як правило, такi ЦАП мають на кристалi вихiдний буферний пiдсилювач. Для роботи ЦАП в унiполярному режимi вiльний вивiд нижнього по схемi резистора R не пiдключають, або пiдключають до спiльноi точки схеми для подвоiння вихiдноi напруги. Для роботи у бiполярному режимi вiльний вивiд цього резистора зтАЩiднують зi входом опорноi напруги ЦАП. Операцiйний пiдсилювач у цьому випадку працюi в диференцiйному включеннi i його вихiдна напруга:

Uвих = 2Uцап тАУUоп = 2Uоп(D/2N тАУ ½).

Перемножувачi та подiльники функцiй

Як вже вказувалося вище, ЦАП на МОН-ключах допускають змiну опорноi напруги в широкому дiапазонi, у тому числi i змiну полярностi. З наведених вище формул випливаi, що вихiдна напруга ЦАП пропорцiйна добутку опорноi напруги на вхiдний цифровий код. Ця обставина дозволяi безпосередньо використовувати такi ЦАП для перемноження аналогового сигналу на цифровий код.

При унiполярному включеннi ЦАП вихiдний сигнал пропорцiйний добутку двополярного аналогового сигналу на одно полярний цифровий код. Такий перемножував називають двоквадрантним. При бiполярному включеннi ЦАП (рис.18,б,в) вихiдний сигнал пропорцiйний добутку двополярного аналогового сигналу на двополярний цифровий код. Ця схема може працювати як чотирьох полярний перемножувач.

Дiлення вхiдноi напруги на цифровий масштаб MD = D/2N виконуiться за допомогою схеми двохквадрантного подiльника (рис.19).

Рис.19. Варiанти схеми двох квадрантного подiльника

В схемi на рис.19,а перетворювач на МОН-ключах зi струмовим виходом працюi як перетворювач тАЮнапруга-струмтАЭ, що керуiться кодом D та включений у коло зворотного звтАЩязку операцiйного пiдсилювача. Вхiдна напруга подаiться на вiльний вивiд резистора зворотного звтАЩязку ЦАП, що розмiщений на кристалi мiкросхеми. У цiй схемi вихiдний струм ЦАП

Iцап = Uвих·D/R·2N = - Uвх/Rос,

що при виконаннi умови Rос =R призводить до:

Uвих = -Uвх·2N/D = - Uвх/MD.

Треба сказати, що при кодi тАЮусi нулiтАЭ зворотнiй звтАЩязок розмикаiться. запобiгти цьому режиму можна, або заборонивши цей код програмно, або включивши мiж виходом та iнвертуючим входом операцiйного пiдсилювача резистор з опором R·2N.

Схема подiльника на основi ЦАП з виходом у виглядi напруги, побудованим на iнверснiй резистивнiй матрицi з буферним операцiйним пiдсилювачем наведена на рис.19,в. Вихiдна i вхiдна напруги цiii схеми звтАЩязанi рiвнянням:

Uвих = 2Uвих·D/2N тАУ Uвх.

звiдси Uвих = Uвх·2N-1/(D тАУ 2N-1) = Uвх/(2MD тАУ 1).

В данiй схемi пiдсилювач охоплений як позитивним, так i негативним зворотнiм звтАЩязком. Для переважання негативного зворотного звтАЩязку (бо iнакше операцiйний пiдсилювач перетвориться у компаратор) необхiдне виконання умови D<2N-1 або MD<1/2. Це обмежуi значення вхiдного коду нижньоi половини шкали.

Атенюатори та iнтегратори на ЦАП

Атенюатори тАУ регулятори рiвня сигналiв, з цифровим керуванням набагато надiйнiшi та довговiчнiшi, нiж традицiйнi атенюатори на базi змiнних резисторiв. РЗх доцiльно використовувати в вимiрювальних приладах та iнших приладах, якi потребують пiдстроювання параметрiв, особливо автоматичних. такi атенюатори найбiльш просто побудувати на основi перемножую чого ЦАП з iнверсною резистивною матрицею та буферним пiдсилювачем. Для цього може пiдiйти будь-який ЦАП вказаного типу. але деякi фiрми випускають перетворювачi, оптимiзованi для виконання цiii функцii. На рис.20,а наведена схема атенюатора на змiнному резисторi, а на рис.20,б тАУ аналогiчна схема на перемножуючому ЦАП.

Рис.20. а) схема атенюатора на змiнному резисторi; б) схема на перемножую чому ЦАП.

Якщо вхiдний сигнал тАУ одно полярний, доцiльно використовувати ЦАП з однополярним живленням, але буферний операцiйний пiдсилювач повинен мати вихiд rail-to-rail, це означаi, що його вихiдна напруга повинна досягати нуля та напруги живлення. Якщо ЦАП тАУ багатоканальний, то у кожного перетворювача мiкросхеми повинен бути iндивiдуальний вхiд опорноi напруги.

Для побудови iнтегратора з цифровою установкою постiйноi часу iнтегрування можна використовувати базову схему iнтегратора, а у якостi вхiдного резистора включити ЦАП з сумуванням напруг (рис.11). На базi такоi схеми можна побудувати фiльтри, генератори iмпульсiв, тощо.

Системи прямого цифрового синтезу сигналiв

Важливою галуззю застосування ЦАП i синтез аналогових сигналiв необхiдноi форми. Аналоговi генератори сигналiв тАУ синусоiдальноi, трикутноi та прямокутноi форм тАУ мають низьку точнiсть та стабiльнiсть, вони не можуть керуватись вiд ЕОМ. В останнi роки розвиваються системи прямого цифрового синтезу сигналiв, що забезпечують високу точнiсть завдання частоти та початковоi фази сигналiв, а також високу вiрнiсть представлення iх форми. Бiльш того, цi системи дозволяють генерувати сигнали з великою рiзноманiтнiстю форм, у тому числi форм, що задаi користувач. Спрощена блок-схема генератора прямого цифрового синтезу сигналiв наведена на рис.21.

Система прямого цифрового синтезу вмiщуi три головних блоки: генератор фазового кута, памтАЩять та ЦАП. Працюi вiн як регiстр фази, вмiст якого одержуi прирощення на деякий фазовий кут через заданi iнтервали часу. Прирощення фази Dj завантажуiться у виглядi цифрового коду у вхiднi регiстри. ПамтАЩять тАУ i таблицею функцiй. Код поточноi фази поступаi на ii адреснi входи, а з виходу даних на вхiд ЦАП поступаi код, що вiдповiдаi поточному значенню даноi функцii. Цап у свою чергу формуi аналоговий сигнал.

Рис.21. Схема прямого цифрового синтезу сигналiв

Регiстр вмiщуi поточну фазу вихiдного сигналу у виглядi цiлого числа, яке, будучи подiлене на 2N, де N тАУ розряднiсть суматора, дорiвнюi частинi перiоду. Збiльшення розрядностi регiстру пiдвищуi тiльки роздiльну здатнiсть цiii долi. Частота вихiдного сигналу дорiвнюi добутку частоти тактiв Fтакт на прирощення фази в кожному перiодi тактiв. При використаннi N-розрядного суматора частота вихiдного сигналу дорiвнюi

Fвих = Δφ·Fтакт/2N.

Генератори прямого синтезу випускаються у виглядi iнтегральних мiкросхем. Наприклад, мiкросхема AD9850, структура якоi показана на рис.21, вмiщуi 32-розрядний генератор фазового кута та 10-розрядний ЦАП. Завантаження прирощення фази здiйснюiться по 8-розряднiй шинi даних побайтово у 4 вхiдних регiстри. ПамтАЩять вмiщуi таблицю синусiв. Максимальна тактова частота тАУ 125 МГц. При цьому роздiл по частотi складаi 0,0291 Гц. Швидкий iнтерфейс дозволяi змiнювати частоту вихiдного сигналу до 23 мiльйонiв разiв за секунду.

Вместе с этим смотрят:

GPS-навигация

GPS-прийомник авиационный

IP-телефония и видеосвязь

IP-телефония. Особенности цифровой офисной связи

Unix-подобные системы