Мiкропроцесорний АЦП порозрядного врiвноваження iз ваговою надлишковiстю, що калiбруiться

Мiнiстерство освiти i науки Украiни

Вiнницький нацiональний технiчний унiверситет

РЖнститут iнформацiйних технологiй та комптАЩютерноi iнженерii

Кафедра ОТ

Пояснювальна записка

з дисциплiни ВлЦифровi ЕОМ та мiкропроцесорнi системиВ»

до спецiалiзованого курсового проекту за спецiальнiстю 7.160104 тАЬАдмiнiстративний менеджмент у сферi захисту iнформацii з обмеженим доступомтАЭ 08-23.ЦМ.004.00.000 ПЗ

МРЖКРОПРОЦЕСОРНИЙ АЦП ПОРОЗРЯДНОГО ВРРЖВНОВАЖЕННЯ РЖЗ ВАГОВОЮ НАДЛИШКОВРЖСТЮ, ЩО КАЛРЖБРУРДТЬСЯ

Керiвник курсовоi роботи

Вл___В» ____________2009 р.

Розробив студент гр. АМЗ-04

_____________________

Вл___В» ____________2009 р.

Вiнниця ВНТУ 2009

Мiнiстерство освiти i науки Украiни

Вiнницький нацiональний технiчний унiверситет

РЖнститут iнформацiйних технологiй та комптАЩютерноi iнженерii

ЗАТВЕРДЖУЮ

Зав. Кафедри ОТ проф., д.т.н.

_______________ О.Д. Азаров

Вл___В» _____________ 2007 р.

РЖНДИВРЖДУАЛЬНЕ ЗАВДАННЯ

на спецiалiзований курсовий проект

з дисциплiни ВлЦифровi ЕОМ та мiкропроцесорнi пристроiВ»

студенту _____________________факультету КСМ групи 1 АМЗ-04

ТЕМА: МРЖКРОПРОЦЕСОРНИЙ АЦП ПОРОЗРЯДНОГО ВРРЖВНОВАЖЕННЯ РЖЗ ВАГОВОЮ НАДЛИШКОВРЖСТЮ, ЩО КАЛРЖБРУРДТЬСЯ

Розробити функцiональну схему та алгоритм функцiонування мiкропроцесорного АЦП порозрядного врiвноваження iз ваговою надлишковiстю, що самокалiбруiться. Обгрунтувати тип мiкропроцесора, який можна використовувати для калiбрування характеристики перетворення.

Функцiональнi можливостi пристрою:

Робота в режимi:

режим основного перетворення аналог-код з програмною корекцiiю ваг розрядiв надлишкового ЦАП;

Розробка програми керування роботою АЦП у заданому режимi.

Додатковi вимоги:

число розрядiв вихiдного двiйкового коду АЦП N=14;

час перетворення в основному режимi  ;

;

система числення надлишкового ЦАП тАУ НПi на основi золотоi пропорцii;

число розрядiв ЦАП N=20;

Термiн здачi студентом завершеного проекту ______________________

Змiст пояснювальноi записки

Вступ

Аналiз технiчного завдання.

Розробка функцiональноi схеми.

Вибiр мiкроконтролера та огляд його архiтектури

Вибiр додаткових елементiв.

Розробка загального алгоритму функцiонування АЦП.

Розробка функцiональноi схеми АЦП.

Розробка програмного забезпечення.

Розробка алгоритму функцiонування.

Органiзацiя памтАЩятi та розподiл адресного простору.

Розробка програми, що керуi роботою мiкропроцесора.

4. Моделювання роботи.

Висновки.

Лiтература.

Графiчна частина:

Алгоритм функцiонування АЦП.

Граф-схема алгоритму.

3. Принципiальна схема пристрою.

Анотацiя

Дана робота присвячена розробцi мiкропроцесорного АЦП порозрядного врiвноваження iз ваговою надлишковiстю, що калiбруiться.

Проводиться аналiз умов та можливостей використання мiкропроцесора для керування роботи АЦП, а також розробка функцiональноi схеми АЦП на базi мiкроконтролера та програмного забезпечення для функцiонування ЦОП.

У додатках наводяться граф-схема алгоритму, лiстинги програм.

Змiст

Перелiк умовних скорочень

Вступ

1. Аналiз технiчного завдання

2. Розробка функцiональноi схеми

2.1 Вибiр мiкроконтролера та огляд його архiтектури

2.2 Вибiр додаткових елементiв

2.3 Розробка загального алгоритму функцiонування АЦП

2.4 Розробка функцiональноi схеми АЦП

3. Розробка програмного забезпечення

3.1 Розробка алгоритму функцiонування пристрою

3.2 Органiзацiя памтАЩятi та розподiл адресного простору

3.3 Розробка програми, що керуi роботою мiкропроцесора

4. Моделювання роботи

Висновки

Перелiк лiтературних джерел

Додаток А. Алгоритм функцiонування АЦП

Додаток Б. Алгоритм функцiонування пристрою

Додаток В. Алгоритм пiдпрограми пiдготовки

Перелiк умовних скорочень

АКтАУаналоговий комутатор

АЛПтАУарифметико-логiчний пристрiй

АЦПтАУаналого-цифровий перетворювач

БДСтАУблок допомiжних сигналiв

БКтАУблок керування

БПтАУблок памтАЩятi

БПВтАУблок порозрядного врiвноваження

ВРЖСтАУвелика iнтегральна схема

ЕОМтАУелектронно-обчислювальна машина

МЗРтАУмолодший значущий розряд

МКтАУмiкроконтролер

МПтАУмiкропроцесор

НПiтАУнадлишкова позицiйна система числення

ОЗПтАУоперативний запамтАЩятовуючий пристрiй

ПВЗтАУпiдсилювач вибирання-зберiгання

ПЗПтАУпостiйний запамтАЩятовуючий пристрiй

РПНтАУрегiстр послiдовного наближення

САЦПтАУАЦП, що самокалiбруються

СЗРтАУстарший значущий розряд

СПтАУсхема порiвняння

ЦАПтАУцифро-аналоговий перетворювач

ЦОПтАУцифровий обчислювальний пристрiй

Вступ

За останнi десятилiття в свiтi створене бiльше сотнi типiв АЦП, вiдмiнних по функцiональному складу i призначенню, конструктивним, електричним i експлуатацiйним характеристикам. Вiдоме iх застосування спiльно з МП i мiкро ЕОМ у складi пристроiв сполучення мiж об'iктами i iнтерфейсом, а також використання як самостiйних функцiональних елементiв у вузлах i блоках.

Сучасний етап характеризуi великi i надвеликi iнтегральнi схеми АЦП, що володiють високими експлуатацiйними параметрами: швидкодiiю, малими погрiшностями, багаторозряднiстю. АЦП знаходять широке застосування в рiзних областях сучасноi науки i технiки. Вони i невiдтАЩiмною частиною цифрових вимiрювальних приладiв, систем перетворення i вiдображення iнформацii, програмованих джерел живлення, iндикаторiв на електронно-променевих трубках, систем радiолокацii, установок для контролю елементiв i мiкросхем, а також важливими компонентами рiзних автоматичних систем контролю i управлiння, пристроiв вводу/виводу iнформацii ЕОМ. На iх основi будують перетворювачi i генератори практично будь-яких функцiй, аналоговi реiструючi пристроi, корелятори, аналiзатори спектру i т.д. Великi перспективи використовування швидкодiючих перетворювачiв в телеметрii i телебаченнi.

Поза сумнiвом, серiйний випуск малогабаритних i вiдносно дешевих АЦП ще бiльш пiдсилить тенденцiю проникнення методу дискретно-безперервного перетворення в сферу науки i технiки.

В даний час застосовують рiзнi типи АЦП, що мiстять в своiму складi МП, якi виконують обробку даних. Очевидно, що обробка даних тАУ одна iз головних функцiй МП, яка включаi як i манiпулювання так i обрахунок даних. РЖншою функцiiю МП i управлiння системою. Схеми управлiння дозволяють декодувати i виконувати програми тАУ набiр команд для обробки даних. Робота МП складаiться з наступних крокiв: спочатку вибираiться команда, потiм логiчна схема ii декодуi, пiсля чого здiйснюiться виконання цiii команди. Також вiдбуваiться обмiн iнформацiiю з зовнiшнiми пристроями, якi пiдтАЩiднанi до МП.

МП являють собою цифровi ВРЖС, призначенi для виконання простих операцiй, iнакше названих командами, що зчитуються i здiйснюються послiдовно з великою швидкiстю. До числа внутрiшнiх схем МП вiдносяться багаторозряднi регiстри, рiвнобiжнi тракти даних, буфери для пiдключення зовнiшнiх пристроiв, багатофункцiональнi схеми, логiчнi схеми синхронiзацii i керування. Багатофункцiональнi схеми призначенi для реалiзацii простих арифметичних i логiчних дiй над двiйковими числами, що знаходяться в регiстрах процесора, i пересилок даних як усерединi процесора, так i мiж ним i зовнiшнiми пристроями. Схеми синхронiзацii i керування задають порядок дiй процесора, для виконання функцiй синхронiзацii iм необхiднi тактовi iмпульси, що постiйно поступають.

Мiкропроцесорнi засоби використовуються у видi мiкропроцесорних комплектiв iнтегральних мiкросхем, що мають iдине конструктивно-технологiчне виконання i призначених для спiльного застосування. Мiкропроцесорний комплект крiм самого МП мiстить мiкросхеми, що пiдтримують функцiонування МП i розширюють його логiчнi можливостi.

МК являi собою логiчний автомат з високим ступенем детермiнованостi, який допускаi небагато варiантiв в його системному включеннi.

В пристроях управлiння обтАЩiктами МК розглядаються у виглядi сукупностi апаратно-програмних засобiв. При проектуваннi схем на базi МК потрiбна реалiзацiя оптимального розподiлу функцiй мiж апаратними засобами i програмним забезпеченням. Рiшення такоi задачi ускладнюiться тим, що взаiмозвтАЩязок i взаiмодiя мiж апаратними i програмними засобами динамiчно змiнюються.

В даний час розповсюджена така методологiя, при якiй весь цикл розробки схем з використанням МК подiляють на три фази:

1) аналiз задачi i вибiр апаратних засобiв;

2) розробка прикладного програмного забезпечення;

3) комплексування апаратних засобiв i програмного забезпечення;

Дана робота присвячена розробцi мiкропроцесорного АЦП порозрядного врiвноваження iз ваговою надлишковiстю, що калiбруiться.

1. Аналiз технiчного завдання

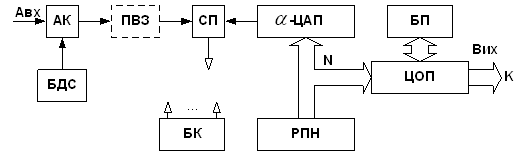

Для зтАЩясування вимог до технiчного завдання, доцiльно навести структуру АЦП порозрядного врiвноваження iз ваговою надлишковiстю, що калiбруiться [1], яку зображено на рисунку 1.1.

Структура повинна мiстити: аналоговий комутатор (АК) тАУ для переключення мiж джерелами аналогових сигналiв; для процедури врiвноваження вхiдного аналогового сигналу використовуiться схема порiвняння (СП), регiстр послiдовних наближень (РПН) та цифро-аналоговий перетворювач ( -ЦАП), який працюi в надлишковiй позицiйнiй системi числення (НПi) (назвемо ii робочою системою числення); цифровий обчислювальний пристрiй (ЦОП) в якому, в залежностi вiд способу калiбрування повиннi виконуватись операцii додавання, вiднiмання, множення, дiлення та операцii з памтАЩяттю; для збереження цифрових еквiвалентiв дiйсних ваг розрядiв та промiжних результатiв обчислень тАУ блок памтАЩятi (БП); блок допомiжних сигналiв (БДС) для створення нульового вхiдного аналогового сигналу, пiд час визначення похибки змiщення нуля та, для вимiрювальних АЦП, наближене до еталонного джерело напруги або струму, що використовуiться пiд час визначення масштабного коефiцiiнту; в деяких випадках для фiксацii рiвня вхiдного аналогового сигналу використовуiться пристрiй вибiрки та збереження (ПВЗ); для узгодження роботи вище згаданих блокiв використовуiться блок керування (БК). Як бачимо, введення ваговоi надлишковостi вiдбиваiться тiльки на

-ЦАП), який працюi в надлишковiй позицiйнiй системi числення (НПi) (назвемо ii робочою системою числення); цифровий обчислювальний пристрiй (ЦОП) в якому, в залежностi вiд способу калiбрування повиннi виконуватись операцii додавання, вiднiмання, множення, дiлення та операцii з памтАЩяттю; для збереження цифрових еквiвалентiв дiйсних ваг розрядiв та промiжних результатiв обчислень тАУ блок памтАЩятi (БП); блок допомiжних сигналiв (БДС) для створення нульового вхiдного аналогового сигналу, пiд час визначення похибки змiщення нуля та, для вимiрювальних АЦП, наближене до еталонного джерело напруги або струму, що використовуiться пiд час визначення масштабного коефiцiiнту; в деяких випадках для фiксацii рiвня вхiдного аналогового сигналу використовуiться пристрiй вибiрки та збереження (ПВЗ); для узгодження роботи вище згаданих блокiв використовуiться блок керування (БК). Як бачимо, введення ваговоi надлишковостi вiдбиваiться тiльки на  -ЦАП, решта блокiв залишаiться стандартними, тому всi обчислення вiдбуваються у загально прийнятiй двiйковiй системi числення. Основна перевага надлишкових позицiйних систем числення (НПi), реалiзована при аналого-цифровому перетвореннi складаiться у вiдсутностi "розривiв" у перетворювальнiй характеристицi, викликаних вiдхиленнями реальних ваг розрядiв вiд iхнiх розрахункових значень. Для "двiйкових" АЦП цi вiдхилення не повиннi перевищувати половини молодшого розряду.

-ЦАП, решта блокiв залишаiться стандартними, тому всi обчислення вiдбуваються у загально прийнятiй двiйковiй системi числення. Основна перевага надлишкових позицiйних систем числення (НПi), реалiзована при аналого-цифровому перетвореннi складаiться у вiдсутностi "розривiв" у перетворювальнiй характеристицi, викликаних вiдхиленнями реальних ваг розрядiв вiд iхнiх розрахункових значень. Для "двiйкових" АЦП цi вiдхилення не повиннi перевищувати половини молодшого розряду.

Рисунок 1.1 тАУ Структурна схема АЦП порозрядного врiвноваження з ваговою надлишковiстю

Для АЦП на основi "золотоi пропорцii" вiдносна похибка ваг розряду за рахунок технологiчних, температурних, часових факторiв може досягати до 23,6% [2], що не приведе до пропускiв кодiв. Таким чином, i можливiсть, знаючи точнi значення реальних ваг розрядiв, що беруть участь у перетвореннi, одержати точне значення вхiдного аналогового сигналу. Задача зводиться до визначення реальних ваг розрядiв у спецiальному режимi роботи АЦП, названому калiбруванням.

Використання НПi при заданi ваг розрядiв ЦАП, дозволяi, за рахунок наявностi зон перекриття мiж сусiднiми розрядами отримати нерозривну передатну характеристику навiть за умови наявностi значних вiдхилень ваг розрядiв [3]. Головним недолiком ЦАП, побудованих з використанням НПi, вважаiться збiльшення кiлькостi розрядiв порiвняно з двiйковим ЦАП, що теоретично мало б призводити до збiльшення часу врiвноваження. Але, як було доведено в працях професора О.Д.Азарова, швидкодiя таких перетворювачiв може бути на порядок бiльша за двiйковi без втрати точностi за рахунок компенсацii динамiчних похибок першого та другого роду [4].

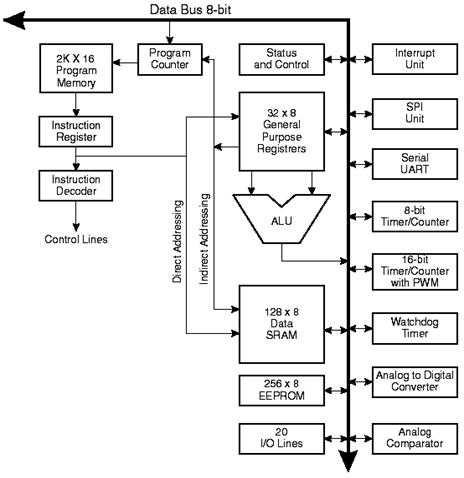

Основою системи числення [5] називаiться спiввiдношення ваг сусiднiх розрядiв

.

.

Для двiйковоi системи  , а для надлишкових систем

, а для надлишкових систем  . До НПi з дробовими вагами розрядiв зокрема вiдносяться так званi системи числення золотоi

. До НПi з дробовими вагами розрядiв зокрема вiдносяться так званi системи числення золотоi  - пропорцii[6].У системах числення золотоi

- пропорцii[6].У системах числення золотоi  -пропорцii, будь-яке натуральне число N* можна зобразити у виглядi

-пропорцii, будь-яке натуральне число N* можна зобразити у виглядi

Ва1.1

Ва1.1

де

тАУ вага  -го розряду або

-го розряду або  -а ступiнь золотоi

-а ступiнь золотоi  -пропорцii. Вiдповiдно при

-пропорцii. Вiдповiдно при  =0 НПi вироджуiться у двiйкову систему числення,

=0 НПi вироджуiться у двiйкову систему числення,  =1 тАУ золота пропорцiя,

=1 тАУ золота пропорцiя,  ВатАУ одиничний код. Значення

ВатАУ одиничний код. Значення  Вадля золотоi пропорцii рiвне 1,618.

Вадля золотоi пропорцii рiвне 1,618.

Застосування вказаноi системи числення в порозрядних АЦП дозволяi виконувати самокалiбрування виключно у цифровiй формi. Це в свою чергу дозволяi вiдмовитися вiд введення додаткових аналогових вузлiв та блокiв для реалiзацii процедури калiбрування ваг розрядiв. Використання таких додаткових вузлiв у пристроi значно ускладнюi аналогову частину АЦП. Разом з тим, калiбрування ваг розрядiв у цифровiй формi в АЦП на основi НПi дозволяi максимально використати можливостi цифрових обчислювальних пристроiв, замiнити аналоговi вузли цифровими i тим самим спростити аналогову частину перетворювачiв, а також знизити ii вартiсть.

2. Розробка функцiональноi схеми

2.1 Вибiр мiкроконтролера та огляд його архiтектури

Сучаснi радiоелектроннi пристроi побудованi на МК. Це дозволяi спростити схему радiоелектронного пристрою, зробити ii бiльш унiверсальною, що дозволяi змiнюючи програму МК покращувати ii споживчi та експлуатацiйнi характеристики.

Розробнику мiкропроцесорних пристроiв приходиться вирiшувати ряд характерних задач: на якому процесорi будувати систему, якi периферiйнi пристроi (таймери, послiдовнi i паралельнi порти, АЦП, ЦАП, i т. д. ) вибрати, який блок живлення, скiльки коштуi розробка.

До недавнього часу у розробникiв не було широкого вибору. Сiмейство однокристальних мiкротАУEОM Intel 8051, здавалось, перекривало по можливостям задачi, якi найбiльш часто зустрiчаються.

Сьогоднi на ринку зтАЩявився цiлий ряд фiрм зi своiми пропозицiями до однокристальних восьмирозрядних мiкро тАУ EОM. В першу чергу це мiкро - ЕОМ сiмейства Z86 фiрми Zilog, МС 68 (Motorola), РРЖС 16/17 (Microchip). Менш вiдомi тАУ мiкро тАУ ЕОМ ST62 (Thomson) та СОР800(National).

Для того, щоб вибрати з цього рiзноманiття найбiльш вдалу базу для майбутнього мiкропроцесорного пристрою, необхiдно мати порiвняльнi характеристики всiх вище перерахованих однокристальних мiкро тАУ ЕОМ. Однак кiнцевий вибiр залежить вiд багатьох факторiв. В першу чергу, це привтАЩязанiсть розробника чи традицii, далi тАУ складнiсть вирiшуваноi задачi цiна однокристальноi мiкро тАУ ЕОМ.

Цiкаве опитування було проведено серед вiдвiдувачiв сайту ВлТелесистемиВ». Учасники могли вiдповiсти на питання: тАЬЯкому мiкроконтролеру ви вiддаiте найбiльшу перевагу?тАЬ Голоси розподiлилися таким чином (таблиця 2.1): найбiльш популярними стали МК архiтектура AVR ( розробка Atmel) i класичноi архiтектури MCS-51 (розробка Intel).

Популярна також структура PIC, розроблена Microchip. Малопопулярнi МК фiрми Zilog типу Z8 тАФ виключно iз-за одноразовоi структури програмування. Технiчнi параметри приблизно однаковi, показники надiйностi тАФ теж. Залишаються тiльки мiркування чисто фiнансового характеру. РЖ ось тут вiдмiнностi iстотнi. Наприклад, цiна МК фiрми Intel, в 2, а то i в 3 рази вище за цiну МК фiрми Atmel.

Таблиця 2.1 тАУ Статистика опитування на сайтi http://" onclick="return false">

| Мiкроконтролер | Кiлькiсть голосiв |

| АСРЖ | 3 (0%) |

| AVR | 309 (29%) |

| MCS-51 | 220 (21%) |

| PIC | 317 (30%) |

| Z8 | 35 (3%) |

| Z80 | 21(2%) |

| РЖнший | 60 (5%) |

| Кращий мiкроконтролер тАФ DSP | 33 (3%) |

| Ненавиджу мiкроконтролери | 41(3%) |

Фiрма Atmel запропонувала цiкаву серiю AVR, яка миттiво знайшла пiдтримку у радiоаматорiв. У МК серii AVR використовуються принципи так званоi RISC архiтектури, коли пам'ять програм i пам'ять даних, з якими програма оперуi, не тiльки роздiленi фiзично, але ще мають i рiзнi канали зв'язку з ядром (рiзнi шини). Окрiм цього, i ще одна цiкава особливiсть, яка називаiться конвеiризацiiю. Конвеiризацiя дозволяi одночасно i виконувати команду, i готувати до виконання наступну. Гарвардська архiтектура, а також конвеiризацiя i деякi iншi спецiальнi заходи дозволяють виконувати iнструкцii дуже швидко тАФ за один машинний цикл.

МК серii AVR мають в своiму складi компаратори, АЦП, пристроi ШРЖМ, послiдовнi порти вводу/виводу. Звичайно, рiзнi типономiнали включають рiзнi пристроi, але iх набiр на сьогоднiшнiй момент i нормою.

Таким чином вибираiмо МК фiрми Atmel [7].

Для вибору мiкроконтролера потрiбно враховувати його технiчнi характеристики, такi як:

швидкодiя мiкроконтролера;

наявнiсть потрiбноi периферii;

число лiнiй введення-виведення;

споживану потужнiсть.

Мiкроконтролер, який вiдповiдаi даним параметрам належить до сiмейства AVR. АVR тАФ це нове сiмейство 8-розрядних RISC-мiкроконтролерiв фiрми Atmel. Цi мiкроконтролери дозволяють вирiшувати безлiч задач убудованих систем. Вони вiдрiзняються вiд iнших розповсюджених у даний час мiкроконтролерiв бiльшою швидкiстю роботи, бiльшою унiверсальнiстю. Швидкодiя даних мiкроконтролерiв дозволяi в рядi випадкiв застосовувати iх у пристроях, для реалiзацii яких ранiше можна було застосовувати тiльки 16-розряднi мiкроконтролери, що дозволяi вiдчутно знизити цiну готовоi системи. Крiм того, мiкроконтролери АVR дуже легко програмуються за допомогою компiлятора мови асемблера.

Фiрма Atmel випускаi великий спектр мiкроконтролерiв серед яких iз потрiбними параметрами можна визначити модель AT90S2333.

AT90S2333 тАУ економiчний 8-бiтовий КМОН МК, побудований з використанням розширеноi RISC архiтектури AVR. Виконуючи по однiй командi за перiод тактовоi частоти, що дозволяi розробникам створювати системи оптимальнi по швидкостi i споживанiй потужностi. У основi ядра AVR лежить розширена RISC архiтектура, об'iднуюча розвинений набiр команд i 32 регiстри загального призначення. Всi 32 регiстри безпосередньо пiдключенi до АЛП, що даi доступ до будь-яких двох регiстрiв за один машинний цикл.

Подiбна архiтектура забезпечуi десятиразовий виграш в ефективностi коду в порiвняннi з традицiйними CISC МК.

AT90S2333 пропонуi наступнi можливостi: 2 Кбайт - пам'ять з пiдтримкою внутрiшнього системного програмування, 128 байт EEPROM, 20 лiнiй I/O загального призначення, 32 робочих регiстра загального призначення, два унiверсальнi таймер/лiчильники з режимами порiвняння, внутрiшнi i зовнiшнi переривання, програмований послiдовний UART, 6-ти канальний, 10-ти розрядний АЦП, програмований сторожовий таймер з вбудованим тактовим генератором i програмований послiдовний порт SPI для завантаження програм в Flash пам'ять, а також, два програмно вибираних режиму економii енергоспоживання. Режим очiкування ВлIdleВ» зупиняi CPU, але залишаi функцiонувати SRAM, таймер/лiчильники, SPI порт i систему переривань. Режим економii енергоспоживання ВлPower DownВ» зберiгаi значення регiстрiв, але зупиняi тактовий генератор, вiдключаючи всю решту функцiй мiкроконтролера, аж до наступного зовнiшнього переривання, або до апаратноi iнiцiалiзацii.

МК виробляiться з використанням технологii незалежноi пам'ятi високоi щiльностi фiрми Atmel. Flash пам'ять на кристалi може бути перепрограмована прямо в системi через послiдовний iнтерфейс SPI або доступним програматором незалежноi пам'ятi. Об'iднуючи на одному кристалi вдосконалений 8-бiтовий RISC процесор iз Flash пам'яттю, AT90S2333 i потужним мiкроконтролером, який дозволяi створювати ефективнi та маловартiснi пристроi.

AVR AT90S2333 пiдтримуiться повним набором програм i пакетiв для розробки, включаючи: компiлятори С, макроасемблери, внутрiшньосхемнi емулятори i набори для макетування.

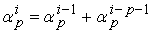

Мiкроконтролери сiмейства AVR мають iдину базову структуру. Узагальнену структурну схему мiкроконтролера AT90S2333 зображено на рисунку 2.1.

Рисунок 2.1 тАУ Блок схема мiкроконтролера AT90S2333

До складу мiкроконтролера входять:

генератор тактового сигналу (GCK);

процесор (CPU);

постiйний запам'ятовуючий пристрiй для збереження програми виконаний за технологiiю Flash (FlashROM);

оперативний запам'ятовуючий пристрiй статичного типу для збереження даних (SRAM);

постiйний запам'ятовуючий пристрiй для збереження даних, виконаний за технологiiю EEPROM, (EEPROM);

набiр периферiйних пристроiв для вводу/виводу даних i керуючих сигналiв, i виконання iнших функцiй.

До складу процесора (CPU) входять:

лiчильник команд (PC);

арифметико-логiчний пристрiй (ALU);

блок регiстрiв загального призначення (GPR, General Purpose Registers) i iншi елементи.

Крiм регiстрiв загального призначення в мiкроконтролерi маються регiстри спецiальних функцiй, що у сiмействi AVR називаються регiстрами вводу/виводу (РЖ/O Registers, IOR). За участю цих регiстрiв здiйснюються:

керування роботою мiкроконтролера i окремих його пристроiв;

визначення стану мiкроконтролера i окремих його пристроiв;

ввiд даних у мiкроконтролер й окремi його пристроi.

Кожному регiстру присвоiне iм'я, пов'язане з функцiiю, яку виконуi цей регiстр. Мiкроконтролер AT90S2333 маi 20 регiстрiв вводу/виводу, якi iменованi, як:

Port B (PB5.PB0) - Порт B i 6-бiтовим двонаправленим портом вводу/виводу з внутрiшнiми пiдтягаючими резисторами. Вихiднi буфери порту B можуть поглинати струм до 20мА. Якщо виводи PB0.PB5 використовуються як входи i ззовнi встановлюються в низький стан, вони i джерелами струму, якщо включенi внутрiшнi пiдтягаючi резистори.

Port С (PС5.PС0) - Порт С i 6-бiтовим двонаправленим портом вводу/виводу з внутрiшнiми пiдтягаючими резисторами. Вихiднi буфери порту С можуть поглинати струм до 20мА. Якщо виводи PС0.PС5 використовуються як входи i ззовнi встановлюються в низький стан, вони i джерелами струму, якщо включенi внутрiшнi пiдтягаючi резистори.

Port D (PD5.PD0) - Порт D i 8-бiтовим двонаправленим портом вводу/виводу з внутрiшнiми пiдтягаючими резисторами. Вихiднi буфери порту B можуть поглинати струм до 20мА. Якщо виводи PD0.PD7 використовуються як входи i ззовнi встановлюються в низький стан, вони i джерелами струму, якщо включенi внутрiшнi пiдтягаючi резистори.

RESET - вхiд скидання. Утримання на входi низького рiвня протягом двох машинних циклiв (якщо працюi тактовий генератор), скидаi пристiй.

Мiкроконтролери сiмейства AVR i пристроями синхронного типу. Дii, якi виконуються в мiкроконтролерi, прив'язанi до iмпульсiв тактового сигналу.

Як генератор тактового сигналу (GCK) використовуються:

внутрiшнiй генератор iз зовнiшнiм кварцовим чи керамiчним резонатором (XTAL);

внутрiшнiй RC-генератор (РЖRC);

внутрiшнiй генератор iз зовнiшнiм RC-колом (ERC);

зовнiшнiй генератор (ЕХТ).

У мiкроконтролерiв, якi мають внутрiшнiй генератор iз зовнiшнiм резонатором. XTAL1 i XTAL2 i входом i виходом iнвертуючого пiдсилювача, на якому можна зiбрати генератор тактових iмпульсiв. Можна використовувати як кварцовi, так i керамiчнi резонатори. Якщо сигнал генератора необхiдно використовувати для управлiння зовнiшнiми пристроями, сигнал з виводу XTAL2 знiмаiться через одиночний буфер. При подачi зовнiшнього тактового сигналу вивiд XTAL2 залишаiться непiдключеним, а XTAL1 пiдключаiться до виходу зовнiшнього генератора.

Процесор (CPU) формуi адреса черговоi команди, вибираi команду з пам'ятi й органiзовуi ii виконання.

До складу процесора крiм лiчильника команд (PC), арифметико-логiчного пристрою (ALU) i блоку регiстрiв загального призначення (GPR) входять:

регiстр стану мiкроконтролера SREG;

регiстр-показник стека SP чи SPL i SPH.

Високопродуктивно AVR ALU з'iднано безпосередньо з усiма 32 швидкодiючими регiстрами загального призначення. За один тактовий цикл ALU виконуi операцiю мiж регiстрами цього реiстрового файлу. Операцii ALU пiдроздiляються на три основнi категорii: арифметичнi, логiчнi i бiтовi [8].

2.2 Вибiр додаткових елементiв

Структурна схема АЦП порозрядного врiвноваження мiстить в аналоговiй частинi ВлнадлишковийВ» ЦАП, що використовуiться пiд час перетворення.

Число розрядiв  , задiяних у надлишковому ЦАП, природно, бiльше нiж у двiйковому

, задiяних у надлишковому ЦАП, природно, бiльше нiж у двiйковому  Вай визначаiться зi спiввiдношення:

Вай визначаiться зi спiввiдношення:

. (2.1)

. (2.1)

Так, для побудови АЦП 14-ти розрядноi точностi ( =14) при α=1,618 потрiбен ЦАП на

=14) при α=1,618 потрiбен ЦАП на  =20 розряду коду "золотоi пропорцii". Незважаючи на збiльшення розрядноi сiтки, швидкодiя АЦП на основi НПi не зменшуiться, а навпаки, може бути iстотно збiльшена. Зазначений ефект виникаi внаслiдок витрати частини надмiрностi ваг розрядiв на автокомпенсацiю динамiчних похибок iз сигналу, що компенсуi [8].

=20 розряду коду "золотоi пропорцii". Незважаючи на збiльшення розрядноi сiтки, швидкодiя АЦП на основi НПi не зменшуiться, а навпаки, може бути iстотно збiльшена. Зазначений ефект виникаi внаслiдок витрати частини надмiрностi ваг розрядiв на автокомпенсацiю динамiчних похибок iз сигналу, що компенсуi [8].

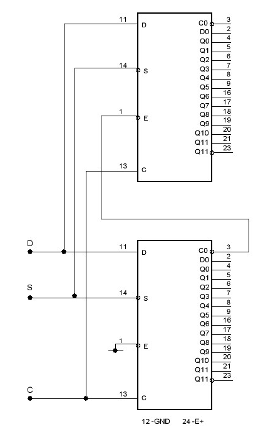

Для роботи ЦАП використовуiться РПН, що забезпечуi утворення кодових комбiнацiй, якi створюють компенсуючий сигнал для компаратора в процесi порозрядного врiвноваження. Основною складовою РПН i спецiальний регiстр тАУ мiкросхема AM2504 [7], яка зображена на рисунку 2.2, яка призначена для побудови АЦП, що працюють по принципу послiдовного наближення з числом розрядiв до 12. Маi в своiму складi 4 входи:

С тАУ для подачi тактових iмпульсiв (спрацювання по зростанню тактових iмпульсiв), D тАУ iнформацiйний вхiд, Е тАУ дозвiл перетворення та S тАУ вхiд тАЬпусктАЬ.

Робота мiкросхеми показана на дiаграмах C-DO, що зображена на рисунку 2.2.

Рисунок 2.2 тАУ Мiкросхема AM2504

При подачi на вхiд S логiчного 0 по спаду чергового iмпульсу вiдбуваiться початкова установка тригерiв регiстра. На виходi закiнчення перетворення C0 з'являiться логiчна 1. Такий стан регiстра зберiгатиметься до тих пiр, поки на входi S буде логiчний 0.

Пiсля встановлення на входi S логiчноi 1 перший спад iмпульсу негативноi полярностi виробить запис в тригер регiстра з виходами 12 i 12 iнформацii з входу D i встановить вихiд 11 в стан 0, на виходах 10-1 i C0 буде логiчноi 1.

Спад чергового iмпульсу негативноi полярностi виробить запис iнформацii з входу D в черговий тригер регiстра i встановить наступний за ним вихiд в стан 0. Таким чином, на виходах регiстра по черзi з'являiться логiчний 0, вслiд за ним - iнформацiя з входу D.

Пiсля запису iнформацii з входу D в останнiй тригер регiстра (з виходом 1) на виходi C0 з'являiться логiчний 0 i цей стан регiстра фiксуiться до появи логiчного 0 на входi S. Якщо вхiд S з'iднати з виходом C0, поява логiчного 0 на виходi C0 по спаду чергового тактового iмпульсу приведе до встановлення початкового стану регiстра аналогiчно iмпульсу 0. В результатi мiкросхема повторюватиме описаний вище цикл роботи.

Рисунок 2.3 тАУ Часова дiаграма роботи мiкросхеми AM2504

Наявнiсть входу Е дозволяi сполучати мiж собою мiкросхеми для отримання регiстрiв послiдовного наближення на бiльшу кiлькiсть розрядiв, як показано на рисунку 2.4. Робота таких регiстрiв аналогiчна роботi однiii мiкросхеми.

Мiкросхема дозволяi використовувати ii як регiстр послiдовного наближення i з меншим, нiж на 12, числом розрядiв, для чого для подачi сигналу на вхiд S можна використовувати його з'iднання з будь-яким з виходiв 1-11.

Рисунок 2.4 тАУ ЗтАЩiднання мiкросхем AM2504 для збiльшення кiлькостi розрядiв

2.3 Розробка загального алгоритму функцiонування АЦП

АЦП порозрядного врiвноваження перетворить аналоговий сигнал в цифровий за N крокiв, де N тАФ розряднiсть АЦП. На кожному кроцi визначаiться по одному бiту шуканого цифрового значення, починаючи СЗР i закiнчуючи МЗР. Послiдовнiсть дiй за визначенням чергового бiта полягаi в наступному. На ЦАП виставляiться аналогове значення, утворене з бiтiв, вже визначених на попереднiх кроках; бiт, який повинен бути визначений на цьому кроцi, виставляiться в 1, бiльш молодшi бiти встановленi в 0. Отримане на допомiжному ЦАП значення порiвнюiться з вхiдним аналоговим значенням. Якщо значення вхiдного сигналу бiльше значення на допомiжному ЦАП, то визначуваний бiт отримуi значення 1, iнакше 0. АЦП цього типу володiють одночасно високою швидкiстю i хорошою розряднiстю.

Слiд зазначити, що використання АЦП iз ЦАП на основi НПi у складi систем цифровоi обробки аналогових сигналiв також даi певнi переваги перед двiйковими перетворювачами iнформацii. Так, зменшений час врiвноважування дозволяi пiдняти частоту дискретизацii, збiльшити кiлькiсть оброблюваних каналiв при роботi в багатоканальному режимi. Незважаючи на спрощену технологiю виготовлення аналогових вузлiв, результуюча точнiсть перетворення як ЦАП, так i АЦП на основi НПi може бути досить високою при роздiльностi не менше 14-16 двiйкових розрядiв. Це досягаiться, зокрема, калiбруванням ваг розрядiв i корекцiiю статичних похибок, що здiйснюiться цифровим обчислювальним пристроiм. Причому даний пристрiй може одночасно виконувати двi функцii: калiбрування похибок i перетворення НПi у двiйкову систему. Для виконання операцiй безпосередньо з цифровими сигналами доцiльно використовувати мiкроконтролер. СП, a-ЦАП, РПН i БК сукупно складають ядро АЦП тАУ блок порозрядного врiвноважування (БПВ). У БК передбачено можливiсть подачi сигналу керування Узв.

Задачею БПВ i перетворення аналогового сигналу з виходу ПВЗ в робочий код К(а), що формуiться у РПН. Для перетворення робочого коду К у двiйковий код використовуiться окремий ЦОП. Причому на етапi виготовлення системи i компонування аналогових вузлiв здiйснюiться високоточне вимiрювання ваг розрядiв АЦП. Отриманi результати у виглядi двiйкових кодiв заносяться в БП i використовуються надалi для роботи. Для звтАЩязку ЦОП iз каналами виведення двiйковоi цифровоi iнформацii використовуiться послiдовний або паралельний iнтерфейс залежно вiд необхiдноi швидкостi передавання iнформацii [9].

Граф-схему алгоритму функцiонування АЦП системи наведено в додатку А. Тут: j тАУ номер каналу; i тАУ номер такту порозрядного врiвноважування в БПВ; k тАУ номер дискретизацii; С тАУ результат обчислень у ПК; В тАУ операнд, якому призначаються значення кодiв iз ПЗП; К(ΔА0) тАУ код похибки нуля; Кi тАУ код ваги i-го додатного розряду;  ВатАУ код ваги i-го вiдтАЩiмного розряду. Причому у випадку НПi (0,1) iснуi тiльки один вiдтАЩiмний розряд тАУ знаковий; П тАУ масив пам'ятi в мiкроконтролерi, в якому фiксуються коди дискретизованих вiдлiкiв аналогових сигналiв. Значення цифрового сигналу у=1 вiдповiдаi режимовi вибiрки ПВЗ, у=0 - збереження. У процесi функцiонування системи аналоговi сигнали з входу подаються на ПВЗ. Дискретизованi вiдлiки потiм перетворюються в цифровi еквiваленти i надходять у ЦОП для вiдповiдного оброблення. Причому на етапi проектування вимiряються ваги розрядiв a-ЦАП, коди яких фiксуються в ПЗП. Надалi цi розряди вважаються "точними" i "стабiльними". Водночас варто вiдзначити, що зазначений пристрiй можна виконати, зокрема, на базi мiкроконтролера.

ВатАУ код ваги i-го вiдтАЩiмного розряду. Причому у випадку НПi (0,1) iснуi тiльки один вiдтАЩiмний розряд тАУ знаковий; П тАУ масив пам'ятi в мiкроконтролерi, в якому фiксуються коди дискретизованих вiдлiкiв аналогових сигналiв. Значення цифрового сигналу у=1 вiдповiдаi режимовi вибiрки ПВЗ, у=0 - збереження. У процесi функцiонування системи аналоговi сигнали з входу подаються на ПВЗ. Дискретизованi вiдлiки потiм перетворюються в цифровi еквiваленти i надходять у ЦОП для вiдповiдного оброблення. Причому на етапi проектування вимiряються ваги розрядiв a-ЦАП, коди яких фiксуються в ПЗП. Надалi цi розряди вважаються "точними" i "стабiльними". Водночас варто вiдзначити, що зазначений пристрiй можна виконати, зокрема, на базi мiкроконтролера.

2.4 Розробка функцiональноi схеми АЦП

МК для мiкропроцесорного АЦП порозрядного врiвноваження, що калiбруiться повинен реалiзувати функцii таких блокiв як: БК, ЦОП, БП, БДС.

Для реалiзацii даних блокiв та iх функцii потрiбно, щоб МК забезпечував роботу:

1 лiнii РЖ/О для прийому сингалу вiд СП;

1 лiнii РЖ/О для передачi сигналу даних для РПН;

1 лiнii РЖ/О для сигналу дозволу перетворення РПН;

1 лiнii РЖ/О для сигналу початкового встановлення РПН;

14 лiнii РЖ/О для паралельного вихiдного двiйкового коду;

програмованого таймера.

Робота мiкропроцесорного АЦП порозрядного врiвноваження, що калiбруiться полягаi в наступному:

БК забезпечуi управлiння РПН за допомогою 3-х лiнiй РЖ/О передачi сигналу даних D та сигналу S, а також сигналу процесом основного перетворення аналог-код з програмною корекцiiю ваг розрядiв надлишкового ЦАП.

Ваги ЦАП вимiряються на етапi виготовлення й записуються в EEPROM МК. У циклi калiбрування потрiбно сформувати в БП точнi значення ваг розрядiв ЦАП. Для цього за допомогою РПН та ЦАП для кожного з i-го розряду формуiться аналоговий сигнал.

На початку перетворення вiдбуваiться початкове встановлення всiх даних МК, а також встановлення сигналiв S та С з рiвня логiчного 0 в рiвень логiчноi 1 для початкового запуску РПН. Сигнал S в процесi перетворення залишаiться в рiвнi логiчноi 1, а сигнал С забезпечуi запуск кожного наступного такту перетворення шляхом формування строб-iмпульсу, що керуi РПН по передньому фронту переходу з рiвня логiчного 0 в логiчну 1. Вiдбуваiться примусове вмикання старшого розряду, що подаiться на надлишковий ЦАП з якого у виглядi компенсуючого сигналу передаiться на компаратор.

Пiсля виконання порiвняння вхiдного сигналу з компенсуючим компаратор видаi сигналу у виглядi певного логiчного рiвня (логiчного 0 або 1).

МК сприймаi даний сигнал на БК через порт та вiд його значення виконуi функцii керування РПН, а також забезпечуi формування цифрового еквiваленту аналогового сигналу за допомогою збережених в БП ваг розрядiв.

У цьому режимi ЦОП з метою перетворення надлишкового коду на виходi РПН у двiйковий вихiдний код здiйснюi просте пiдсумовування двiйкових еквiвалентiв ваг розрядiв, якi виявилися включеними пiсля зрiвноважування вхiдного аналогового сигналу.

Про iх включення на РПН свiдчить сигнал з компаратора, що сприймаiться БК.

Час перетворення в основному режимi визначаiться за допомогою програмованого таймера, що формуi часовий перiод для виконання одного з тактiв врiвноваження. Пiсля завершення перiоду роботи таймера вiдбуваiться перевiрка лiчильника такту перетворення, i вiдсутностi переповнення оцiнюiться рiвень сигналу з компаратора, а також передача сигналiв даних та дозволу для запуску РПН.

Пiсля обчислення двiйкового вихiдного коду в ЦОП, на основi збережених в EEPROM двiйкових еквiвалентiв надлишкових кодiв, що вiдповiдають кодам на виходi РПН, вiдбуваiться iх виведення через порти МК. Вивiд здiйснюiться за допомогою 14 лiнiй РЖ/О для паралел

Вместе с этим смотрят:

GPS-навигация

GPS-прийомник авиационный

IP-телефония и видеосвязь

IP-телефония. Особенности цифровой офисной связи

Unix-подобные системы