Разработка архитектуры, принципиальной схемы и конструкции специализированного микроконтроллера

Введение

Микропроцессорные интегральные схемы (МП ИС) и микро-ЭВМ, построенные на их основе, явились следствием бурного развития микроэлектроники, позволившего в одном кристалле полупроводника размещать сложные вычислительные структуры, содержащие десятки тысяч транзисторов. Изготовление больших интегральных схем (БИС) сопряжено с трудоемкой работой по разработке схем, фотошаблонов и подготовкой производства и служб контроля технологических параметров и характеристик БИС. Снижение себестоимости БИС возможно лишь при максимальной автоматизации этапов, предшествующих их изготовлению, и массовости производства.

Массовое производство БИС предполагает широкий спрос потребителя, а следовательно, возможность ее использования для большого круга решаемых задач. Микропроцессорные БИС (МП БИС) представляют тот класс интегральных схем, который сочетает в себе высокую степень интеграции, обеспечивающую огромные функциональные возможности, с большой универсальностью по применению.

Целями курсового проекта являются:

- изучение методики проектирования микропроцессорных систем от технического задания до рабочих чертежей;

- углубление знаний полученных в теоретических курсах;

- получение навыков внедрения теоретических знаний в практические применения.

Основной задачей курсового проекта является разработка архитектуры, принципиальной схемы и конструкции специализированного микроконтроллера, выполняющего функции, определенные заданием, на базе заданных технических средств.

Исходные данные для проекта

1. Базовый восьмиразрядный микроконтроллер.

2. Оперативные периферийные устройства: индикаторы семисегментные (10 знакомест), клавиатура (16 клавиш), внешние прерывания (3 линии).

3. Внешние устройства: входное АЦП (7 каналов, 12 разрядное,  В);

В);

выходное ЦАП (1 канала, 10 разрядное,  В).

В).

4. Интерфейс для связи с дополнительными внешними устройствами  .

.

5. Схема сопряжения с фотоимпульсным датчиком углового положения ФИ.

1 Описание функциональной схемы

На рисунке 1 представлена функциональная схема микроконтроллера с внешними устройствами.

Рисунок 1 тАУ Схема электрическая функциональная микроЭВМ

Рисунок 1 тАУ Схема электрическая функциональная микроЭВМ

Микропроцессорная система включает в себя:

1. Микроконтроллер AT89C5131A-L

2. Контроллер клавиатуры и индикации КР580ВВ79.

3. 1-канальный10-разрядный цифро-аналоговый преобразователь с интерфейсом SPI MAX503

4. 8-канальный 14-разрядный аналого-цифровой преобразователь с интерфейсом SPI AD7949.

5. Схема сопряжения с фотоимпульсным датчиком.

AT89C5131A-L тАУ высокопроизводительная версия 8-разрядного однокристального микроконтроллера 80C51 с флэш-памятью и функциями полноскоростной USB-связи.

Микроконтроллер имеет:

- высокопроизводительное микропроцессорное ядро C51 совместимое со стандартом 8051.

-аппаратно реализованные последовательные интерфейсы I2С, SPI и интерфейс USB

- 34 цифровых входа/выхода

- две линии внешних прерываний.

Микроконтроллер имеет встроенную схему слежения за напряжением питания, сторожевой таймер, тактовый генератор и представляет собой функционально законченную систему на одном кристалле. Все аналоговые и цифровые периферийные модули могут включаться/отключаться и настраиваться программой пользователя.

Контроллер клавиатуры-дисплея (ККД) КР580ВД79 обеспечивает обслуживание клавиатуры (сканирование клавиатуры, и выдача сигнала процессору, при нажатии клавиши) и обслуживание индикаторов (обеспечивается подключение 10 семисегментных индикаторов и регенерацию изображения в динамическом режиме).

В качестве индикатора используется 10 семисегментных индикаторов АЛС348А. Подключается к МК через контроллер клавиатуры/дисплея.

Клавиатура 2×8 (16 клавиш) подключается к МК также через контроллер клавиатуры/дисплея.

Для связи с внешними используется встроенный последовательный интерфейс I2С.

Для обеспечения подключения 12-разрядного ЦАП MCP4921 и 14-разрядного АЦП AD7949 используется встроенный в микроконтроллер последовательный SPI интерфейс.

Для организации трёх клавиш прерывания и прерываний от внешних устройств используется логическая схема расширения прерываний, которая подаёт сигнал прерывания на вход порта Р3.1 и Р3.2 при нажатии одной из клавиш прерывания.

2 Разработка принципиальной схемы

В полную принципиальную схему контроллера, кроме описанного выше блока процессора, входят ЦАП, АЦП, клавиатура, индикаторы.

2.1 Описание микроконтроллера

AT89C5131A-L содержит следующие компоненты: 32 кбайт флэш-памяти с поддержкой внутрисистемного программирования через интерфейс USB, 3 кбайт флэш-памяти для загрузочной программы, 1 кбайт ЭСППЗУ для хранения данных, 256 байт ОЗУ, встроенное ОЗУ расширения (ERAM) 1024 байт, встроенная схема контроля питания (сброс при подаче питания/определение снижения напряжения питания), полноскоростной модуль USB, совместимый с требованиями USB1.1 и USB 2.0, 34 линий ввода-вывода общего назначения, байт-ориентированный 2-проводной последовательный интерфейс TWI, последовательный порт SPI (режим ведущий/подчиненный), режимы холостого хода и снижения мощности, расширенный диапазон напряжения питания: 2.7-5.5В.

AT89C5131A-L поддерживает два программно-управляемых режима со сниженной активностью, позволяющие снизить уровень потребления. В режиме холостого хода прекращает работу ЦПУ, а таймеры, последовательные порты и система прерываний продолжают функционировать. В режиме снижения мощности сберегается содержимое ОЗУ и останавливается синхронизация периферийных устройств, а возобновление работы микроконтроллера возможно при возникновении событий USB или внешних прерываний.

Микроконтроллер выпускается по технологии высокоплотной энергонезависимой памяти компании Atmel. Механизм программирования встроенной флэш-памяти позволяет перепрограммировать ее внутрисистемно через последовательный интерфейс SPI с помощью обычного программатора энергонезависимой памяти или с помощью встроенной загрузочной программы, выполняемой ядром AVR. Загрузочная программа может использовать любой интерфейс для загрузки программного кода во флэш-память. За счет разделения флэш-памяти на загрузочный сектор и сектор прикладной программы поддерживается действительная возможность чтения во время записи, когда загрузочный код продолжает исполняться и выполняется обновление сектора прикладной программы.

2.2 Организация памяти

В состав памяти входит ОЗУ объемом 256 байт. К младшим 128 байтам можно получить доступ при прямой или косвенной адресации. Старшие 128 байт имеют двойную конфигурацию. В режиме косвенной адресации осуществляется доступ к старшим 128 байтам ОЗУ общего назначения, а в режиме прямой адресации осуществляется доступ к 128 байтам адресного пространства регистров специального назначения (SFR).

При обращении к памяти по адресу выше адреса 7Fh, процессор определяет доступ к старшим 128 байтам RAM данных или к регистрам SFR способом адресации.

Память программ МК состоит из 32 Кбайт Flash-памяти. Эта память может перепрограммироваться внутрисистемно, не требуя при этом специального внешнего напряжения программирования, а используя стандартное напряжение VDD.

Согласно сказанного выше область хранения данных используемых при работе ЦМК удобно расположить в адресах 30hтАж7Fh, где возможна прямая адресация регистров, в случае нехватки места можно задействовать регистры косвенной адресации 80hтАжFFh.

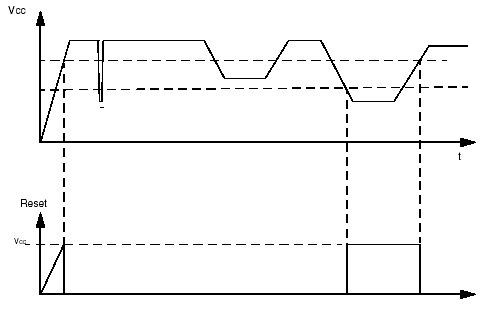

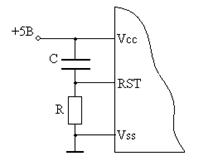

2.3 Формирование сигнала сброс

МК AT89C5131A-L содержат схему слежения за напряжением питания. При включении питания схема контроля питания немедленно осуществляет сброс, которая удерживает МК в состоянии сброса, пока напряжение питания VDD не превысит в процессе включения уровень VRST, в соответствии с временной диаграммой представленной на рисунке. При этом запускается внутренний счетчик для задержки. В течение таймаута схемы слежения за напряжением питания на выводе /RST удерживается низкий логический уровень, что позволяет напряжению питания стабилизироваться.

2.4 ЦАП

MCP4921 тАУ экономичные 12-разрядные цифро-аналоговые преобразователи с возможностью изменения коэффициента передачи выходного буфера и SPI-интерфейсом. Преобразователи обеспечивают высокую точность и малый уровень шумов во всем расширенном диапазоне температур. Данный тип преобразователя может быть использован в телевизионных и радиолокационных системах, системах сбора и обработки данных в реальном масштабе времени, измерительной аппаратуре и др. Конструктивно она выполнена в корпусе типа DIP-8.

Напряжение питания: AVDD=5В, DVDD=5В.

Выходное напряжение: Vout=0тАж5В;

Разрядность: 12 бит;

Диапазон выходного напряжения соответствует заданным требованиям.

ЦАП сопрягается с МК по интерфейсу SPI в 4-х проводном режим работы. Обращение к ЦАП производится сигналом микроконтроллера с P1.1/SS на вывод выборки микросхемы CS. При этом МК является ведущим устройством, а ЦАП тАУ ведомым.

Сигнал MOSI (master-out, slave-in - Влвыход ведущего, вход ведомогоВ») является выходом данных ведущего устройства и входом данных ведомых устройств. Он используется для последовательной передачи данных от ведущего к ведомому. Данные передаются старшими значащими разрядами вперед. При работе в ведущем режиме значение сигнала MOSI определяется старшим значащим разрядом сдвигового регистра как в 3-х проводном, так и в 4-х проводном режимах.

Сигнал MISO (master-in, slave-out - Влвход ведущего, выход ведомогоВ») является выходом данных ведомого устройства и входом данных ведущего устройства. Он используется для последовательной передачи данных от ведомого к ведущему. Этот сигнал является входом. Данные передаются старшими значащими разрядами вперед. Вывод MISO переводится в высокоимпедансное состояние, когда модуль SPI отключен, а также тогда, когда модуль SPI работает в 4-х проводном режиме как ведомый, который не выбран. Когда модуль SPI работает в 3-х проводном режиме как ведомый, сигнал MISO всегда определяется старшим значащим разрядом сдвигового регистра.

Сигнал SCK (serial clock тАУ Влимпульсы тактирования последовательного интерфейсаВ») является выходом ведущего устройства и входом ведомых устройств. Он используется для синхронизации обмена данными между ведущим и ведомым устройствами по линиям MOSI и MISO. При этом сигнал SCK игнорируется ведомым SPI, когда ведомый не выбран (SS = 1).

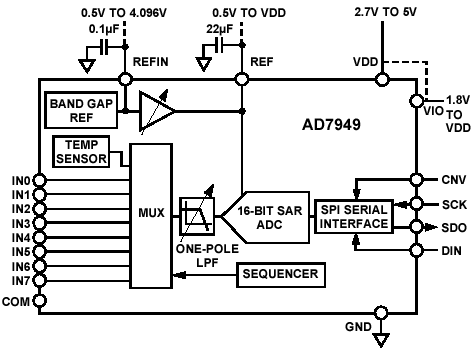

2.5 АЦП

По заданию устройство должно считывать информацию с восьми аналоговых каналов, имеющих диапазон входного напряжения  Ваи преобразовывать входной аналоговый сигнал в 14-ти разрядный цифровой код на выходе.

Ваи преобразовывать входной аналоговый сигнал в 14-ти разрядный цифровой код на выходе.

Для этого выбираем АЦП AD7949 фирмы Analog Devices. Данный АЦП имеет 8 аналоговых входа и диапазон входного напряжения от 0 B до 5 В, поэтому необходимо вводить дополнительные внешние элементы для преобразования входного напряжения. Снижение уровня сигнала осуществляется на микросхемах DA1 тАУ DA4 AD-8513, имеющих в своем составе по четыре операционных усилителя. На двух усилителях происходит снижение напряжения, при этом они включены по инвертирующей схеме, на двух других осуществляется инверсия сигнала. Условное графическое обозначение микросхемы операционного усилителя представлено на рисунке 14.

Рисунок тАУ Функциональная блок схема АЦП

АЦП типа AD7949 предназначена для применения в электронной аппаратуре в составе блоков аналогового ввода. Микросхема выполняет функцию 8-канального 14-разрядного аналого-цифрового преобразования однополярного или биполярного входного сигнала с представлением результатов преобразования в последовательном двоичном коде.

Для организации обмена информацией используется также SPI интерфейс. Обращение к АЦП производится сигналом микроконтроллера с P1.1/SS на вывод выборки микросхемы CNV. При этом МК является ведущим устройством, а АЦП тАУ ведомым.

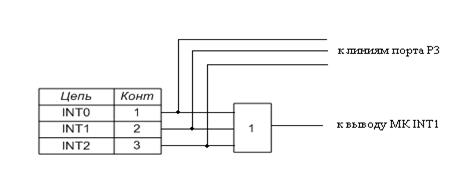

2.6 Организация прерываний

Прерывания осуществляются от 3 клавиш и от контроллера клавиатуры/дисплея. Сигнал прерывания, приходящий от ККД, поступает на вход Р3.2/INT0 МК.

Поскольку количество источников прерываний больше линий внешних прерываний микроконтроллера, то необходимо использовать дополнительную логическую схему ВлИЛИВ». При осуществлении хотя бы одного прерывания сигнал с элемента ВлИЛИВ» приходит на линию Р3.3/INT1 МК. При этом на одну из линий порта Р3 (P3.0, P3.1, P3.4) подается логическая 1. Таким образом, проанализировав программно состояние линий Р3.0, Р3.1 и Р3.4 можно в зависимости от номера нажатой клавиши передать управление подпрограмме обработки данного прерывания.

2.7 Последовательный интерфейс I2C

В данном разделе приводится описание двухпроводного последовательного I2C -интерфейса, так как он используется для обмена информацией между микроконтроллером внешними периферийными устройствами. В данном микроконтроллере данный интерфейс именуется как интерфейс TWI. Протокол TWI позволяет связываться с устройствами через одну двухпроводную двунаправленную шину, где одна линия - линия синхронизации SCL и одна - линия данных SDA.

В качестве внешних аппаратных компонентов, которые требуются для реализации шины, необходимы только подтягивающий к плюсу питания резистор на каждой линии шины. Все устройства, которые подключены к шине, имеют свой индивидуальный адрес. Внешнее подключение устройств к шине TWI изображено на рисункетАж.

Подключение устройств к шине TWI

Протокол передачи данных по шине разработан таким образом, чтобы гарантировать надежный качественный прием/передачу данных. При передаче данных одно устройство является тАЬВедущимтАЭ, которое инициирует передачу данных и формирует сигналы синхронизации. Другое устройство тАЬВедомоетАЭ, которое может начать передачу данных только по команде ведущего шины.

Каждое устройство на шине имеет уникальный адрес. Когда ведущий инициирует передачу данных, то сначала передается адрес устройства, к которому выполняется обращение. Остальные устройства проверяют переданный ведущим адрес. В составе байта адреса устройства входит бит направления передачи данных (выполняется чтение из ведомого или запись). Ведомый и ведущий шины всегда находятся в противоположном режиме работы, что можно представить в виде двух состояний: ведущий передатчик тАУ ведомый приемник; ведомый передатчик тАУ ведущий приемник. В обоих случаях ведущий формирует тактовый сигнал.

Вывод тактового сигнала SCL и данных SDA должны иметь выход с открытым коллектором, чтобы выполнять требования тАЬмонтажного ИтАЭ на шине. Число устройств, которые могут быть подключены к шине, ограничивается только максимальной емкостью шины (400 пФ).

3 Описание работы контроллера клавиатуры/дисплея КР580ВД79

микроконтроллер разработка схема

Микросхема КР580ВД79, именуемая для краткости ККД (контроллер клавиатуры/дисплея), представляет собой универсальное программируемое устройство сопряжения с клавиатурой и дисплеем на основе семисегментных светодиодных индикаторов (ССИ).

Он состоит из двух основных функционально разделимых частей: клавиатурной и дисплейной. Клавиатурная часть предназначена для сопряжения с клавиатурой печатающих устройств и с произвольными наборами переключателей. Дисплейная часть ПККИ позволяет отображать информацию с помощью индикаторов различных типов (дисплеев). В нашем случае используется десять семисегментных индикаторов, которые используются в качестве алфавитно-цифрового дисплея.

Клавиатурная часть обеспечивает работу с клавиатурой размером 8x8 + 2 клавиши или с матрицей 8x8 датчиков. Обеспечиваются различные дисциплины распознавания нажатых клавиш, антидребезговый контроль. Имеется память кодов нажатых клавиш на 8 байт, организованная в виде очереди FIFO. При занесении в эту память более 8 кодов устанавливается признак переполнения. Нажатие клавиши возбуждает линию прерывания, которая может опознаваться в МК.

Дисплейная часть обеспечивает работу с дисплеем на семисегментных индикаторах (их может быть до 32 шт.). Имеется ОЗУ дисплея на 16 байт, организованное в виде двух массивов 16х4 бита. Память дисплея может быть загружена из МК и прочитана им. И в том, и в другом случае возможно автоинкрементирование адреса ОЗУ дисплея. Таким образом, ККД освобождает МК от задач постоянного сканирования клавиатуры и поддержания изображения на дисплее.

Назначение входных, выходных и управляющих сигналов ПККИ приведено в таблице 3.

Таблица 3

| Обозначение вывода | Назначение вывода |

| RL0-RL7 | Входы линий возврата, служащие для подачи сигналов от датчиков через контакты клавиш или ключа |

| SHIFT | Вход сигнала сдвига, используемого для сканирования клавиатуры |

| CNTL/STB | Вход сигнала управления для режима сканирования клавиатуры или стробирующего сигнала для режима ввода по стробу |

| RD | Вход сигнала чтения L-уровня, разрешающего передачу информации из ПККИ в канал данных микропроцессора |

| WR | Вход сигнала записи L-уровня, разрешающего передачу информации из канала данных микропроцессора в ПККИ |

| A0 | Вход для управления записью/чтением данных или команд; при сигнале Н-уровня происходит запись команды или чтения состояния ПККИ, при сигнале L-уровня тАФ запись или чтение данных |

| CS | Выбора микросхемы; L тАФ уровень сигнала разрешает работу схемы |

| CLK | Вход сигнала синхронизации микросхемы |

| RESET | Линия сброса ПККИ в начальное состояние |

| DB0 тАУ DB7 | Двунаправленная шина данных |

| OA0 тАУ OA3 | Выходы канала А (старшая тетрада) |

| OB0 тАУ OB3 | Выходы канала В (младшая тетрада) |

| BD | Выход сигнала гашения отображения L-уровня |

| SL0 тАУ SL3 | Выходы сигналов сканирования клавиш клавиатуры |

| IRQ | Выход сигнала прерывания |

Вместе с этим смотрят:

GPS-навигация

GPS-прийомник авиационный

IP-телефония и видеосвязь

IP-телефония. Особенности цифровой офисной связи

РЖсторiя диктофону