Сигнальнi мiкропроцесори

Змiст

Вступ

1. Загальнi вiдомостi про цифрову обробку сигналiв

2. Специфiка задач цифровоi обробки сигналiв

3. Сигнальнi процесори компанii ANALOG DEVICES

3.1 Структурна схема ADSP21xx та призначення функцiональних блокiв

3.2 Функцiонування хост-порта ADSP-2181

3.3 Функцiонування циклiчних буферiв

Лiтература

Вступ

Тема реферату ВлСигнальнi мiкропроцесориВ» з дисциплiни ВлМультимiкропроцесорнi системиВ».

У мiру зменшення вiдносини вартiсть/продуктивнiсть стаi бiльше економiчним застосовувати кiлька мiкропроцесорiв (далi ─ МП), замiсть одного складного.

Мета роботи тАУ загальне ознайомлення з сигнальними мiкропроцесорами.

1. Загальнi вiдомостi про цифрову обробку сигналiв

Цифрова обробка сигналiв - це арифметична обробка в реальному масштабi часу послiдовностi значень амплiтуди сигналу, визначаiмих через рiвнi промiжки часу.

Прикладами цифровоi обробки i:

- фiльтрацiя сигналу;

- згортка двох сигналiв;

- обчислення значень кореляцiйноi функцii двох сигналiв;

- посилення, обмеження або трансформацiя сигналу;

- пряме/зворотне перетворення Фур'i перетворення.

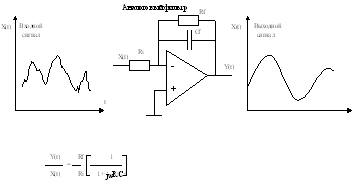

Аналогова обробка сигналу (мал.1) i бiльше дешевим способом досягнення бажаного результату. Використовуваний у фiльтрi операцiйний пiдсилювач розширюi динамiчний дiапазон оброблюваних сигналiв. Форма амплiтудно-частотноi характеристики (АЧХ) фiльтра визначаiться значеннями величин Rf, Cf. Для аналогового фiльтра складно забезпечити високе значення добротностi, характеристики фiльтра сильно залежать вiд температурного режиму. Компоненти фiльтра вносять додатковий шум у результуючий сигнал. Аналоговi фiльтри важко перебудовувати в широкому дiапазонi частот.

Малюнок 1 Аналогова обробка сигналу

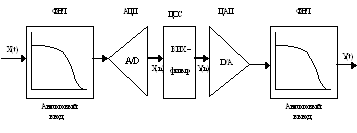

Однак, коли потрiбна висока точнiсть обробки, мiнiатюрнiсть пристрою, стабiльнiсть його характеристик у рiзних температурних умовах функцiонування, цифрова обробка (мал.2) виявляiться iдино прийнятним рiшенням.

Малюнок 2 Цифрова обробка сигналу

Фiльтри низькоi частоти виконують попереднi й наступне видалення iз частотного спектра додаткових гармонiк сигналу. АЦП i ЦАП призначенi для перетворення аналогового сигналу в цифровий i навпаки. АЧХ Ких-фильтра визначаiться значеннями коефiцiiнтiв фiльтра h(к). Змiнюючи кiлькiсть коефiцiiнтiв (довжину фiльтра) i iхнього значення, можна одержати фiльтр iз будь-який необхiдноi АЧХ. Внесений шум (шуми квантування) залежить вiд частоти й розрядностi АЦП i ЦАП, а також точностi обчислень.

Для ефективноi реалiзацii алгоритмiв цифровоi фiльтрацii необхiдна апаратна пiдтримка базових операцiй : множення з накопиченням (МАС), модульноi адресноi арифметики, нормування результатiв арифметичноi операцii.

РЖснуi велика розмаiтiсть реалiзацiй дискретного перетворення Фур'i. У рядi алгоритмiв використаються прийоми, що дозволяють зменшити обсяг необхiдних обчислень. Цi алгоритми вiдомi пiд загальною назвою Влшвидке перетворення Фур'iВ»

2. Специфiка задач цифровоi обробки сигналiв

Для цифровоi обробки сигналiв використаються так названi сигнальнi процесори. До iхнiх особливостей вiдноситься малоразрядна (40 розрядiв i менш) обробка операндiв у форматi iз плаваючою крапкою, переважне використання чисел у фiксованому форматi (розряднiсть 32 i менш), а також орiiнтацiя на нескладну обробку бiльших масивiв даних.

Особливiсть завдань цифровоi обробки - потоковий характер обробки бiльших обсягiв даних у реальному масштабi часу.

Сигнальнi процесори мають високий ступiнь спецiалiзацii. У них широко використаються методи скорочення тривалостi командного циклу, характернi й для унiверсальних RISC-процесорiв, такi як конвеiризацiя на рiвнi окремих мiкроiнструкцiй i iнструкцiй, наявнiсть тiньових регiстрiв для збереження стану обчислень при перемиканнi процесiв (контексту), подiл шин команд i даних (Гарвардська архiтектура).

Характерним i наявнiсть апаратного множника, що дозволяi виконувати операцii множення двох чисел за один командний цикл. РЖншою особливiстю сигнальних процесорiв i включення в систему команд таких операцiй, як множення з накопиченням (МАС) = З: =А*В +С с зазначеним у командi числом виконань у циклi й iз правилом змiни iндексiв використовуваних елементiв масивiв А и В. У сигнальних процесорах реалiзуiться апаратна пiдтримка програмних циклiв, кiльцевих буферiв. Один або трохи операндiв витягаються з пам'ятi в циклi виконання команди.

Сигнальнi процесори рiзних компанiй-виробникiв утворять два класи: бiльше дешевi мiкропроцесори обробки даних у форматi з фiксованою крапкою й бiльше дорогi, апаратно пiдтримуючi операцii у форматi iз плаваючою крапкою.

Використання в сигнальнiй обробцi формату iз плаваючою крапкою обумовлено декiлькома причинами. Для багатьох завдань, пов'язаних з виконанням iнтегральних i диференцiальних перетворень, особливу значимiсть маi точнiсть обчислень, забезпечити яку дозволяi експонентний формат подання даних. Алгоритми компресii, декомпресii, адаптивнiй фiльтрацii в цифровiй обробцi сигналiв пов'язанi з визначенням логарифмiчних залежностей i досить чутливi до точностi подання даних у широкому динамiчному дiапазонi.

Робота з даними у форматi iз плаваючою крапкою iстотно спрощуi й прискорюi обробку, пiдвищуi надiйнiсть програми, оскiльки не вимагаi операцiй округлення й нормалiзацii даних, вiдстеження ситуацiй втрати значимостi й переповнення. Платою за цi тАЬ комфорт i швидкiстьтАЭ, i висока складнiсть функцiональних пристроiв, що виконують обробку даних у плаваючому форматi, необхiднiсть використання бiльше складних технологiй виробництва мiкросхем, великий вiдсоток вiдбраковування виробiв i як наслiдок - дорожнеча МП.

У цей час став популярний i iнший пiдхiд до одержання високоi продуктивностi. Велика кiлькiсть транзисторiв на кристалi може бути використана для створення симетричноi мультипроцесорноi системи з бiльше простими процесорами, що обробляють цiлочисленi операнди. Прикладами таких медiйних процесорiв i Mediaprocessor компанii MicroUnity, Trimedia компанii Philips, Mpact Media Engine компанii Chromatic Research, NV1 компанii Nvidia, MediaGx компанii Сyrix. Цi процесори створювалися, виходячи з потреби обробки в реальному часi вiдео- i аудiоiнформацii в мультимедiйних ПК, iгрових приставках, побутових радiоелектронних приладах. У зв'язку з бiльш простою системотехнiкою в порiвняннi з унiверсальними сигнальними процесорами вартiсть медiйних процесорiв досить низька (порядку $100 ), а значення показника Влпродуктивнiсть/вартiстьВ» на два-три порядка бiльше. Пiкове значення продуктивностi медiйних процесорiв становить кiлька мiльярдiв операцiй у секунду.

У числi найпоширенiших сигнальних процесорiв можна назвати вироби наступних компанiй Motorola (56002,96002),Intel (i960),Texas Instruments (TMS320Cxx),Analog Devices (21xx,210xx). Бiльша продуктивнiсть, необхiдна при обробцi сигналiв у реальному масштабi часу, спонукала двi останнi з перерахованих компанiй випустити трансптАЩютернi сiмейства мiкропроцесорiв TMS320C4x i ADSP2106х, орiiнтованi на використання в мультипроцесорних системах.

Вибiр того або iншого процесора для реалiзацii конкретного проекту i складним завданням, однак слiд зазначити перевагу процесорiв компанii Analog Devices для додаткiв, що вимагають виконання бiльших обсягiв математичних обчислень (таких як цифрова фiльтрацiя сигналiв, обчислення кореляцiйних функцiй i т.п.) оскiльки iхня продуктивнiсть на подiбних завданнях вище, нiж у процесорiв компанii Motorola, Texas Instruments. У той же час для завдань, що вимагають виконання iнтенсивного обмiну iз зовнiшнiми пристроями (багатопроцесорнi системи, рiзного роду контролери) переважнiше використати процесори фiрми Texas Instruments, що володiють високошвидкiсними iнтерфейсними пiдсистемами.

3. Сигнальнi процесори компанii ANALOG DEVICES

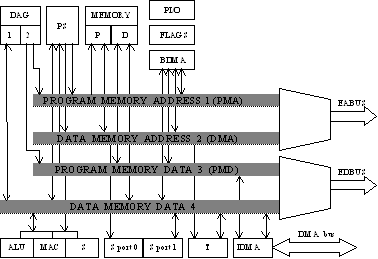

3.1 Структурна схема ADSP21xx та призначення функцiональних блокiв

РЖснуi два сiмейства цiii компанii:

- ADSP21xx - набiр однокристальних 16-розрядних МП iз загальною базовою архiтектурою, оптимiзованою для виконання алгоритмiв цифровоi обробки сигналiв i iнших додаткiв, що вимагають високошвидкiсних обчислень iз фiксованою крапкою. На даний момент iснуi 14 представникiв, що вiдрiзняються друг вiд друга набором периферiйних пристроiв, розташованих на кристалi. Загальна частина - АЛУ, блок МАС, зсувач, генератор адресу даних, генератор адресу команд, ОЗУ даних, ОЗУ команд, таймер. Змiнна частина - багатоканальний послiдовний порт, послiдовний порт 1, порт хост-интерфейса, порт прямого доступу в пам'ять, аналоговий iнтерфейс.

- ADSP210xx-однокристальнi 32-розряднi мiкропроцесори, орiiнтованi на сигнальнi алгоритми, що вимагають виконання обчислень iз плаваючою крапкою. (ADSP21010, ADSP21020, ADSP21060, ADSP21062).

МП мiстить три незалежних повнофункцiональних обчислювальнi пристроi: АЛУ, МАС- множинник iз накопичуванням, пристрiй барабанного зрушення. Кожний пристрiй безпосередньо оперуi з 16-розрядними даними й забезпечуi апаратну пiдтримку обчислень iз рiзною точнiстю.

Пристрiй формування адреси - це генератор адреси команд (PS) i два генератори адреси даних (DAG), що забезпечують адресацiю до даних i команд, розташованим як у внутрiшнiй так i в зовнiшнiй пам'ятi. Паралельне функцiонування генераторiв скорочуi тривалiсть виконання команди, дозволяючи за один такт вибирати з пам'ятi команду й два операнда.

Таймер-лiчильник забезпечуi перiодичну генерацiю переривань.

Послiдовнi порти забезпечують послiдовний iнтерфейс iз бiльшiстю стандартних послiдовних пристроiв, а також з апаратними засобами вiдбудови-стиснення-вiдновлення даних, що використають А i μ - закони компандирування.

Порт iнтерфейсу з хост-процесором дозволяi без додаткових iнтерфейсних схем взаiмодiяти з головним процесором системи, у якостi якого може використатися як процесор даного сiмейства, так i iнший мiкропроцесор, наприклад Motorola або Intel8051.

Малюнок

3 Узагальнена структура мiкропроцесора ADSP21хх

МП даного типу вiдрiзняi високий ступiнь паралелiзму внутрiшнiх операцiй. За один такт процесор виконуi:

- генерацiю адреси наступноi команди;

- завантаження з пам'ятi наступноi команди;

- виконання однiii або двох пересилань даних;

- вiдновлення одного або двох покажчикiв на данi;

- виконати операцiю.

МП, що маi периферiйнi пристроi у своiму змiнному составi, може одночасно з виконанням команди виконати й наступнi операцii:

- прийняти й/або передати данi через послiдовнi порти;

- прийняти й/або передати данi хост-процесору;

- прийняти й/або передати данi через аналоговий iнтерфейс.

Внутрiшнi функцiональнi модулi зв'язанi мiж собою за допомогою п'яти шин: шина адреси пам'ятi даних (DMA), шина адреси пам'ятi команд (РМА), шина даних пам'ятi даних (DMD), шина даних пам'ятi команд (РМ), шина внутрiшнiх результатiв ( R ). Першi чотири шини мають мультиплексiрований зовнiшнiй iнтерфейс у виглядi шини адреси й шини даних.

мультикомпресорна процесор сигнал цифровий

3.2 Функцiонування хост-порта ADSP-2181

Порт iнтерфейсу хост-машини можна представити як область загальноi чи пам'ятi регiстрiв поштовоi скриньки, за рахунок яких здiйснюiться комунiкацiя мiж хост-машиной i цифровим сигнальним процесором. Хост-машина звертаiться до порту iнтерфейсу хост-машини (далi тАУ ХИП), як до областi пам'ятi, що мiстить 8- чи 16-розряднi слова. Для процесора ХИП виступаi як група з восьми регiстрiв, вiдображених у картi пам'ятi даних.

ХИП складаiться з чотирьох функцiональних блокiв:

- керуючий блок iнтерфейсу хост-машини;

- блок iз шести регiстрiв даних (HDR0 тАУ HDR5);

- блок, що складаiться з двох регiстрiв стану (HSR6-HSR7);

- регiстр HMASK, призначений для маскування переривань, сгенерованих ХИП.

Керуючий блок забезпечуi керування записом регiстрiв хост-машини i зчитуванням з них. Два регiстри стану представляють статусну iнформацiю, як хост-машинi так i цифровому сигнальному процесору.

Регiстри даних можна представити як блок двухпортовой пам'ятi. Нi для одного з цих регiстрiв не заданий напрямок роботи: як хост-машина так i цифровий сигнальний процесор можуть зчитувати i записувати iнформацiю в цi регiстри. Коли хост-машина зчитуi данi з регiстрiв даних, генеруiться маскуiме переривання зчитування ХИП. Коли здiйснюiться операцiя запису вiд хост-машины, генеруiться маскуiмий сигнал переривання запису.

Стану зчитування/запису зберiгаються в регiстрах стану. Формат регiстрiв стану наступний:

HSR6 тАУ з 0 по 5 розряди тАУ вiдображення стану запису з хост-машины у вiдповiдний буфер даних ХИП Приклад тАУ 0 розряд = 1 тАУ проведена операцiя запису в буфер HDR0 c хост-машини; 1 розряд = 1 тАУ проведена операцiя запису в буфер HDR1 з хост-машини i т.д. З 8 по 15 розряди тАУ вiдображення стану запису з цифрового сигнального процесора у вiдповiдний буфер даних ХИП.

Тому що ХИП, як правило, сполукаiться з бiльш повiльною хост-машиною, сигнальний процесор виконуi своi команди незалежно вiд роботи хип-порта.

Тому що хост-машина, для якоi потрiбно квитирування встановлення зв'язку, повинна очiкувати пiдтвердження вiд сигнального процесора, то вона може зависнути. Якщо перезапуск сигнального процесора вiдбуваiться, коли хост-машина инициалiзувала передачу, але ще не одержала пiдтвердження, то таке пiдтвердження не може бути потiм сгенеровано, i, таким чином, хост-машина може знаходитися в станi чекання невизначений час.

У ХИП не передбачено нiякого апаратного забезпечення для запобiгання ситуацii, коли хост-машина здiйснюi запис у регiстр, стан якого в цей момент зчитуiться цифровим сигнальним процесором ( i навпаки). Коли хост-машина i сигнальний процесор намагаються одночасно записати данi в той самий регiстр, перевагою в такiй операцii користаiться хост-машина.

Опитування i одним з методiв передачi даних мiж хост-машиной i сигнальним процесором. Щораз, коли хост-машина записуi данi в регiстр HDR, встановлюiться один бiт у молодшому байтi регiстра HSR6. Цей бiт залишаiться встановленим доти, поки цифровий сигнальний процесор не зчитуi вмiст даного регiстра HDR. Подiбним чином, коли сигнальний процесор записуi данi в регiстр HDR, у старшому байтi регiстра HSR6 (i в молодшому байтi регiстра HSR7) установлюiться вiдповiдний бiт. Цей бiт автоматично скидаiться при зчитуваннi вмiсту регiстра HDR хост-машиной.

Наприклад: сигнальний процесор може очiкувати в циклi пiд час зчитування бiта HSR, щоб упевнитися, що хост-машина записала новi данi. Коли сигнальний процесор виявляi, що вiдповiдний бiт установлений, вiн виходить з циклу по командi умовного переходу, обробляi новi данi, а потiм повертаiться в цикл. При передачi даних на хост-машину сигнальний процесор очiкуi, поки та не вважаi останнi записанi данi, щоб можна було передавати новi данi. Хост-машина опитуi бiти регiстра HSR, щоб упевнитися, що новi данi i доступними.

Використання протоколу з керуванням по перериваннях звiльняi хост-машину i сигнальний процесор вiд опитування стану регiстрiв стану. Для керованих перериваннями передач на сигнальний процесор хост-машина записуi данi в регiстри даних, а ХИП автоматично генеруi при цьому внутрiшнi переривання. Обслуговування цього переривання аналогiчно всiм iншим.

Для передачi на хост-машину сигнальний процесор записуi данi в регiстри даних, потiм установлюi висновок прапора, зв'язаний iз входом переривань хост-машины, повiдомляючи в такий спосiб останню про те, що данi готовi для передачi . Якщо сигнальний процесор передаi данi на хост-машину тiльки через один регiстр даних, то вмiст цього регiстра може бути безпосередньо злiчено хост-машиной при одержаннi нею сигналу переривання. Якщо для пересилання даних використовуються кiлька регiстрiв даних, хост-машина повинна прочитати регiстр стану, щоб визначити через якi регiстри передаiться iнформацiя.

Крiм передачi iнформацii для хост-машины iснуi ще режим завантаження через ХИП. При цьому можна завантажити внутрiшнi ОЗУ програмою функцiонування сигнального процесора.

Початкове завантаження здiйснюiться двома способами:

- iз зовнiшньоi пам'ятi (звичайно ППЗУ ) з використанням iнтерфейсу пам'ятi;

- з хост-машины з використанням ХИП.

При використаннi якого-небудь конкретного способу необхiдно формувати вiдповiднi файли завантаження, користаючись вiдповiдними утилiтами програмного забезпечення.

3.3 Функцiонування циклiчних буферiв

Для бiльш повного визначення поняття обертового (циклiчного) буфера (регiстра) необхiдно розглянути функцiонування циклiчних буферiв у сигнальних процесорах фiрми ADSP.

РД три реiстрових файли:

1.Файл регiстрiв модифiкацii (М);

2.Файл iндексних регiстрiв (I);

3.Файл регiстрiв довжини (L).

Зчитування i запис даних здiйснюiться через окрему шину,називаний шиною данi пам'ятi даних. РЖндекснi регiстри мiстять дiйснi адреси, використовуванi для доступу до пам'ятi ( як до пам'ятi даних так i до пам'ятi програм). Крiм прямоi адресацii використовуiться також битреверсна адресацiя, при якiй бiти адреси на виходi генератора адреси можуть бути переставленi в зворотному порядку за рахунок установки вiдповiдного бiта режиму в регiстрi станiв чи режиму з використанням спецiальноi команди асемблера сигнального процесора. Цей особливий вид адресацii полегшуi виконання операцiй швидкого перетворення Фур'i. Генератори адреси даних використовують так названу пост-модифiкацiю, а саме пiсля доступу до даних при використаннi непрямоi адресацii вмiст заданого регiстра М додаiться до вмiсту заданого регiстра I. У межах пар I0-I3, M0-M3 ( генератор адреси - даних 1) i пара I4-I7, M4-M7 (генератор адреси тАУ даних 2) можливi будь-якi комбiнацii iндексних регiстрiв i регiстрiв модифiкацii. Адресацiя генератора адреси тАУ даних 1 поширюiться на пам'ять даних, а адресацiя генератора адреси - даних 2 тАУ на пам'ять програм. Це також i особливiстю архiтектури сигнальних процесорiв, тому що в пам'ятi даних зберiгаються перемiннi значення одержуваних сигналiв у дискретному еквiвалентi, а в пам'ятi програм тАУ коефiцiiнти для обчислення формули Фур'i.

Значення, що мiстяться в регiстрах модифiкацii М i цiлими числами зi знаком, так що наступна адреса може бути бiльше чи менше попереднього.

Генератори адреси тАУ даних пiдтримують адресацiю як з лiнiйним так i з циклiчним буфером. Цей режим забезпечуiться регiстром L, що вiдповiдаi номеру регiстра I. Для нециклiчного буфера вмiст L = 0, а для циклiчного буфера дорiвнюi довжинi буфера. Розглянемо використання такоi адресацii на прикладах.

РЖнiцiалiзацiя регiстрiв довжини L для здiйснення нециклiчноi адресацii (лiнiйноi непрямоi адресацii):

I3 = 0 x 3800;

M2 = 0;

L3 = 0;

AX0 = DM (I3,M2)

Перемiнна пам'ятi використовуiться для збереження покажчика адреси

VAR/DM/RAM add_prt (0x3800);

I3 = DM (addr_prt);

L3 =0;

M1 = 0;

AX0 = DM(I3,M1);

Адресацiя по модулю ( циклiчнi буфери). Логiчний пристрiй адресацii по модулю виконуi автоматичну адресацiю по модулю для досягнення доступу до вмiсту циклiчних буферiв. Для обчислення наступного адреси використовуiться тАУ поточна адреса комiрки пам'ятi, що знаходиться в iндексному регiстрi (без знака), що модифiкуiться значенням , що знаходиться в регiстрi М ( зi знаком) i довжина буфера в регiстрi L (без знака). Базова адреса циклiчного буфера довжини L дорiвнюi 2n чи кратний 2n , де n задовольняi умовi 2n-1< L ≤ 2n . РЖншими словами базова адреса i округлення вмiсту L до найближчого ступеня чи двiйки кратноi йому числа. Дане правило припускаi, що визначене число бiт базовоi адреси повинне дорiвнювати 0. Це поняття аналогiчне поняттю вирiвнювання адрес для процесорiв фiрми INTEL. На практицi редактор зв'язкiв сам розмiщаi буфера, обумовленi як циклiчнi по правильних адреса.

Лiтература

1. Ю-Чжен Лю, Г.Гибсон Микропроцессоры семейства 8086/8088 М.: Радио и связь, 1987.

2. Б.В.Шевкопляс Микропроцессорные структуры. Инженерные решения М.: Радио и связь, 1990

3. В.Шевкопляс Микропроцессорные структуры. Инженерные решения. Дополнение первое. М.: Радио и связь, 1993

4. М.Гук Аппаратные средства IBM PC С.Петербург ²Питер² 2000

5. В.Корнеев, А.Киселев Современные микропроцессоры Санкт-Петербург ² БХВ тАУ Петербург ² 2003

6. Локазюк В.М. и др Микропроцессоры и микроЭВМ в производственных системах Киев Издательский центр ² Академия ² 2002

7. Гуржий А.М. и др Архитектура, принципы функционирования и управления ресурсами IBM PC Харьков, 2003

8. В.В.Сташин, А. В. Урусов, О.Ф. Мологонцева Проектирование цифровых устройств на однокристальных микроконтроллерах Л. Энергоатомиздат

9. Под ред.А.Д.Викторова Руководство пользователя по сигнальным микропроцессорам семейства ADSP-2100 Санкт- Петербургский государственный электротехнический университет. Санкт- Петербург 1997

10. М.Предко Руководство по микроконтроллерам в 2-х томах М: Постмаркет, 2001

Вместе с этим смотрят:

IP-телефония. Особенности цифровой офисной связи

РЖсторiя звтАЩязку та його розвиток

Автоматика, телемеханика и связь

Анализ режимов автоматического управления