Унiверсальнi мiкропроцесори, застосовуванi в ММПС. Мiкропроцесори з архiтектурою Itanium (IA-64)

ЗМРЖСТ

ВСТУП

1. УНРЖВЕРСАЛЬНРЖ МРЖКРОПРОЦЕСОРИ, ЗАСТОСОВУВАНРЖВ ММПС

1.1 Типи архiтектур унiверсальних мiкропроцесорiв

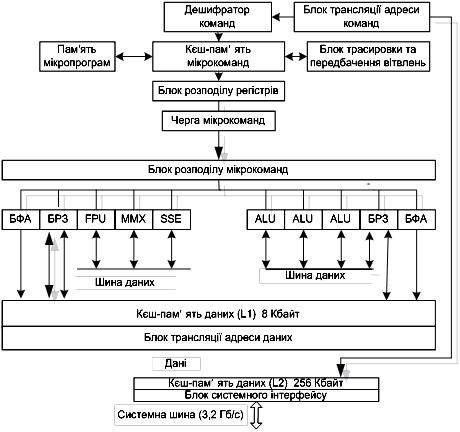

1.2.Архiтектура PENTIUM

1.2.1 Призначення функцiональних блокiв

1.3 Архiтектура PENTIUM MMX

1.4 Архiтектура PENTIUM PRO (P6)

2. МРЖКРОПРОЦЕСОРи з АРХiТЕКТУРОЮ ITANIUM (IA-64)

2.1 Формати та засiб обробки команд

2.2 Структурна схема ITANIUM

2.3 Призначення програмних регiстрiв

ЛРЖТЕРАТУРА

ВСТУП

Тема реферату ВлУнiверсальнi мiкропроцесори, застосовуванi в ММПС. Мiкропроцесори з архiтектурою Itanium (IA-64)В» з дисциплiни ВлМультимiкропроцесорнi системиВ».

Мультимiкропроцесорнi системи (ММПС) - це системи, що мають два й бiльше компонент, якi можуть одночасно виконувати команди. Пiдпорядкованими процесорами можуть бути спецпроцесори, розрахованi на виконання певного типу завдання або процесори широкого застосування. Спецпроцесори - спiвпроцесори, процесори вводу-виводу.

У мiру зменшення вiдносини вартiсть/продуктивнiсть стаi бiльше економiчним застосовувати кiлька мiкропроцесорiв (далi ─ МП), замiсть одного складного

Крiм полiпшення економiчних показникiв системи, мультипроцесорнi конфiгурацii забезпечують кiлька позитивних якостей, вiдсутнiх в однопроцесорнiй конфiгурацii.

Кiлька процесорiв краще пристосовуються пiд вимогу конкретного застосування, крiм витрат на непотрiбнi можливостi централiзованоi системи. Бiльше того, модульнiсть ММПС дозволяi в мiру необхiдностi вводити додатковi процесори.

У ММПС завдання розподiляються мiж модулями. При виникненнi вiдмови у системi простiше та дешевше знайти й замiнити несправний процесор, чим замiняти (вiдшукувати) елемент, що вiдмовив, у складному процесорi.

1. УНРЖВЕРСАЛЬНРЖ МРЖКРОПРОЦЕСОРИ, ЗАСТОСОВУВАНРЖ В ММПС

Домiнуюче положення на ринку мiкропроцесорiв займають мiкропроцесори фiрми Intel - 90 % усього виробництва, iншi 10 % - RISC процесори. РЖснують наступнi типи архiтектур МП:

- архiтектура х86 - фiрма Intel (Pentium P5,P6, P-PRO, P-MMX), фiрма AMD (K5,K6), фiрма CYRIX (M1,M2);

- архiтектура PA - фiрма HP (PA-8000);

- архiтектура ALPHA - фiрма DEC (ALPHA 21064, 21164,21164A);

- архiтектура SPARS - фiрма SUN (лiнiя SPARS);

- архiтектура MIPS - компанiя SILICON GRAPHICS (лiнiя MIPS R-X (R1000));

Тi самi МП використаються в ПЕОМ, робочих станцiях i супер-ЕОМ. У двох останнiх випадках найчастiше використаються симетричнi МП i обчислювальнi системи з масовим паралелiзмом.

На сьогоднiшнiй день всi основнi виробники мiкропроцесорiв мають приблизно рiвнi технологiчнi можливостi, тому в боротьбi за основну характеристику (тактова частота) виходить фактор архiтектури.

На даний момент часу iснують два напрямки розвитку архiтектури:

- SPEED DAEMON - досягнення високоi продуктивностi за рахунок пiдвищення тактовоi частоти;

- BRAINIAC - досягнення високоi продуктивностi за рахунок ускладнення логiки планування обчислень i внутрiшньоi структури МП. Загальна особливiсть всiх МП - високошвидкiсна обробка 64-розрядних операндiв з фiксованою й плаваючою крапкою.

1.2 Архiтектура PENTIUM

Малюнок 1. Структура мiкропроцесора Pentium 4

Технiчнi характеристики:

- тактова частота вiд 60 до 200 Мгц;

- близька до суперскалярноi архiтектура;

- роздiльнi К-П даних i команд;

- пророкування переходiв;

- високопродуктивнi операцii iз плаваючою крапкою;

- удосконалена 64-розрядна шина даних;

- наявнiсть засобiв забезпечення цiлiсностi даних;

- SL-технологii iз засобами керування;

- пiдтримка багатопроцесорностi;

- пiдтримка рiзних розмiрiв сторiнок пам'ятi;

- монiторинг продуктивностi.

Суперскалярна органiзацiя (виконання декiлькох команд за один такт) здiйснюiться за рахунок двох конвеiрiв.

Подвiйний конвеiр Pentium виконуi целочисленi команди в п'ять етапiв:

- передвиборка;

- декодування 1;

- декодування 2;

- виконання;

- запис результатiв.

При цьому кiлька команд можуть перебувати на рiзних етапах виконання (конвеiри залежнi, тобто при зупинцi одного, зупиняiться й другий ).

мiкропроцесор pentium itanium

К-П частково асоцiативна з розмiром рядка рiвним 32 байтам. Буфер TLB перетворить адресу комiрки зовнiшньоi пам'ятi у вiдповiдну адресу даних у К-П. К-П даних використаi метод зворотного запису й протокол MESI. Наявнiсть блока предсказування переходiв - перший тип МП iз такою характеристикою. Виконання твердження переходiв здiйснюiться через буфер BTB i два буфери попередньоi вибiрки. Перший буфер - для попередньоi вибiрки команд у припущеннi, що переходу немаi. Другий буфер тАУ пiд час передвиборки використуiться буфер BTB, у якому зберiгаiться вмiст при виконаннi переходу. Пiдтримуються й вкладенi цикли, тому що BTB зберiгаi кiлька адрес переходiв i до 256 результатiв переходiв.

Операцii iз плаваючою крапкою

Блок операцiй iз плаваючою крапкою розташований усерединi кристала й використовуi складнi 8-рiвневi конвеiри й внутрiшнi функцii. Бiльшiсть команд iз плаваючою крапкою починають виконуватися в одному iз цiлочисельних конвеiрiв, а потiм передаються на конвеiри iз плаваючою крапкою. Функцii додавання, дiлення й множення реалiзованi як внутрiшнi функцii. Блок iз плаваючою крапкою Pentium у порiвняннi з i486 виконуi операцii в 10 разiв швидше.

64-розрядна шина даних

При цiй шинi даних обмiн МП iз пам'яттю здiйснюiться зi швидкiстю 528 Мбайт /с, тобто в 5 разiв перевищуi максимальну швидкiсть IntelDX2 66 Мгц - 105 Мбайт/с.

Розширена шина даних пiдтримуi потiк команд i даних, переданих суперскалярному виконавчому процесорному ядру, що сприяi пiдвищенню iнтенсивностi обробки. У результатi загальна продуктивнiсть в 2,5 рази вище IntelDX2.

Крiм цього, Pentium органiзуi конвеiризацiю циклiв шини, що дозволяi почати другий цикл до завершення першого. Це даi пiдсистемi пам'ятi бiльше часу для декодування адреси й внаслiдок чого можна застосовувати бiльше повiльнi й менш дорогi елементи пам'ятi, що вiдбиваiться на вартостi системи. Крiм того, збiльшенню пропускноi здатностi й надiйностi системи сприяi пiдтримка пакетного читання й запису, перевiрка парностi адреси й даних.

Для пiдвищення швидкостi виконання послiдовних операцiй запису в пам'ять Pentium маi два буфери запису ( по одному на кожний конвеiр), завдяки яким процесор може продовжувати роботу, виконуючи наступнi команди, хоча результат однiii з поточних команд ще не записаний в пам'ять через зайнятiсть шини.

Засоби забезпечення цiлiсностi даних

Забезпечення внутрiшнього виявлення помилок (наявнiсть бiтiв парностi внутрiшнiх буферiв процесора), а також тестування за допомогою функцiональноi надмiрностi (використання двох МП - основного й що перевiряi). У парi цi МП виконують паралельнi обчислення. Один МП порiвнюi результати обчислень iз результатами обчислень другого МП. У випадку непорiвняння результатiв генеруiться переривання.

Керування енергоспоживанням

Здiйснюiться на двох рiвнях - на рiвнi МП i на рiвнi системи. На першому рiвнi - при виконаннi завдань, не потребуючi виконання iнтенсивних обчислень (редагування текстiв), переклад МП у режим зi зниженою тактовою частотою й зниженою напругою живлення. Можливий навiть SL- режим (сплячий). На другому рiвнi використаiться режим SMM (System Management Mode), що контролюi енергоспоживання у всiм ПК (включаючи периферiйнi пристроi). Цей режим забезпечуi iнтелектуальне керування системою, що дозволяi МП сповiльнювати функцiонування, припиняти або повнiстю припиняти роботу окремих системних компонентiв.

Пiдтримка мультипроцесорностi

Здiйснюiться з використанням протоколу когерентностi К-П MESI, а також за допомогою контролера багатопроцесорних переривань, що пiдтримуi до 60 процесорiв i 2-входового контролера К-П другого рiвня, що дозволяi двом процесорам спiльно використати одну К-П другого рiвня.

Пiдтримка рiзних розмiрiв сторiнок пам'ятi

Для першого режиму розмiр сторiнок дорiвнюi 4 Кб, а для другого - 4 Мб. Для програмного забезпечення цей режим прозорий. Вiн уведений для зменшення частоти перемикання сторiнок у складних графiчних додатках i ядрi операцiйноi системи.

Монiторинг продуктивностi

Це засiб, що дозволяi проектувальникам системи й розроблювачам додаткiв оптимiзувати апаратне й програмне забезпечення, завдяки виявленню в програмному кодi Влвузьких мiсцьВ». Розроблювачi можуть спостерiгати й пiдраховувати такти для внутрiшнiх процесорних подiй, що впливають на продуктивнiсть операцii читання й записи, на промах i влучення в К-П, перериванню, використання системноi шини.

1.3 Архiтектура PENTIUM MMX

МП Pentium ММХ мiстить у собi всi функцii Pentium плюс 57 додаткових команд (реалiзацiя мультимедiйних алгоритмiв), цифрова обробка сигналiв, операцii над векторами, згортка, перетворення Фур'i.

Також реалiзованi подвоiнi обсяги К-П даних i команд ( по 16 Кбайт кожна), розширена конвеiризацiя - 6 команд. Полiпшено логiку пророкування переходiв i здiйснена бiльше глибока буферiзацiя пам'ятi.

Для виконання додаткового набору команд використаiться ММХ - пристрiй i блок регiстрiв iз плаваючою крапкою. Доданi 8 ММХ регiстрiв (ММ0-ММ7). Вони фiзично сполученi з 64-розрядними регiстрами iз плаваючою крапкою тому що можуть бути використанi тiльки над операцiями iз ММХ даними.

Швидкiсть виконання мультимедiйних операцiй на 60 % вище в порiвняннi з Pentium.

Застосовуiться при проектуваннi старших моделей робочих станцiй i мультипроцесорних систем. Ефект використання досягаiться тiльки для 32-розрядних додаткiв. Нова конструкцiя корпуса, що складаiться iз двох мiкросхем, помiщених в один керамiчний корпус i не погодиться з виводами Pentium. У випадку використання Pentium-PRO необхiдний перехiд на новi системнi плати.

Тактова частота - 133 Мгц (для технологii 0,6мкм), i 200 Мгц (для технологii 0,35мкм). Потужнiсть розсiювання - 14 Вт.

Висока продуктивнiсть у Р-РRO забезпечуiться за рахунок використання нововведень в архiтектурi й технологii, а саме - рознесена архiтектура, динамiчне виконання команд, подвiйна незалежна шина.

Нова архiтектура К-П тАУ DIB -передбачаi використання рiзних шин для з'iднання процесорного ядра з К-П i основною оперативною пам'яттю. Перша шина працюi на тактовiй частотi процесора, друга iз частотою системи. Такий подiл шин дозволило в три рази прискорити обмiн процесора з пiдсистемою пам'ятi.Завдяки цьому вiдпадаi необхiднiсть у зовнiшньоi К-П.

МП мiстить роздiльнi К-П першого рiвня для даних i команд, кожна обсягом 8 Кбайт, i об'iднану К-П другого рiвня. К-П даних першого рiвня двухпортова, що не блокуi , пiдтримуi одну операцiю завантаження й одну операцiю запису за такт.

РЖнтерфейс К-П другого рiвня працюi з тактовою частотою центрального процесора й може передавати 64 бiта за такт. Зовнiшня шина МП працюi з 1/2, 1/3, 1/4, тактовоi частоти центрального процесора.

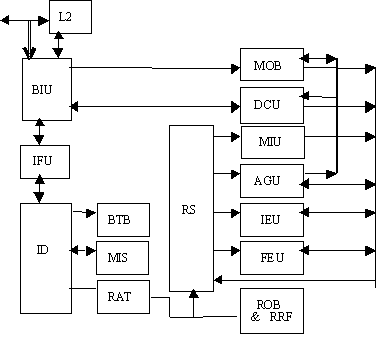

Малюнок 2. Структура PENTIUM PRO

BUI - пристрiй iнтерфейсу iз шиною;

IFU - пристрiй пiдкачування команд ( з К-П команд);

BTB - буфер адрес переходiв;

ID - декодер команд;

MIS - планувальник мiкрокоманд;

RAT - таблиця псевдонiмiв регiстрiв;

ROB - буфер переупорядкування;

RRF - файл регiстрiв вивантаження;

RS - станцiя, що резервуi;

IEU - пристрiй цiлочисельних команд;

FEU - пристрiй команд iз плаваючою крапкою;

AGU - пристрiй генерацii адреси;

MUI - пристрiй iнтерфейсу з пам'яттю;

DCU - пристрiй керування К-П даних;

МОВ - буфер переупорядкування звертань до пам'ятi

L2 - К-П другi рiвнi.

512-елементний буфер адрес переходiв (ВТВ -Branch Target Buffer) дозволяi скоротити число тактiв при вибiрцi рядкiв з К-П пристроiм пiдкачування команд. Процес вибiрки конвеiризований. Новий рядок вибираiться кожний такт центрального процесора. Три паралельних декодери кожний такт перетворюють кiлька команд архiтектури х86 у набори мiкрооперацiй.

Таблиця псевдонiмiв регiстрiв використаiться для перейменування регiстрiв. Результат перейменування посилаi в пристрiй резервування й у буфер переупорядкування.

Мiкрооперацii з перейменованими операндами мiстяться в чергу в пристроi резервування, де очiкують значень операндiв, що надходять незалежно вiд декiлькох джерел. Даними i результати виконаноi мiкрооперацii, адреси iз ВТВ, умiст регiстрiв.

Вибiр мiкрооперацiй iз черги й динамiчне виконання здiйснюiться з облiком iхнiх iстинних залежностей по даним, а також залежно вiд доступностi виконавчих пристроiв (IEU, FEU,AGU). Порядок, у якому виконуються мiкрооперацii, у загальному випадку вiдрiзняiться вiд iхнього розташування у вихiднiй програмi.

При плануваннi звертань до пам'ятi використаiться пристрiй резервування, пристрiй генерацii адреси, i буфер переупорядкування звертань до пам'ятi.

Мiкрооперацiя стаi кандидатом на вивантаження вiдразу, як тiльки вона виконана, визначена адреса переходу й отриманих результатiв спрямованi до нужденнiй у них мiкрооперацii. Для вiдновлення первiсного порядку мiкрооперацiй використаються тимчасовi мiтки мiкрооперацiй у буферi переупорядкування й файлi регiстрiв вивантаження. Процес вивантаження повинен забезпечити не тiльки вiдновлення первiсного порядку мiкрооперацiй, але й гарантувати правильну обробку переривань i помилок, а також скасовувати всi або частина результатiв, отриманого пiсля неправильного пророкування розгалуження. У момент вивантаження мiкрооперацii ii результат з буфера переупорядкування мiститься у файл регiстрiв вивантаження.

2. МРЖКРОПРОЦЕСОРи з АРХiТЕКТУРОЙ

ITANIUM (IA-64)

Початок випуску тАУ2001 рiк, технологiя 0,18мкм з тактовою частотою 660,733,800 Мгц, концепцiя EPIC (Explicity Parallel Instruction Computing) тАУявне паралельне виконання команд. Основнi особливостi концепцii:

1.Велика кiлькiсть регiстрiв;

2.Масштабування по кiлькостi функцiональних пристроiв (можливiсть збiльшення числа функцiональних пристроiв в подальших моделях мiкропроцесора);

3.Явне завдання паралелiзму в машинному кодi;

4.Предикативне виконання iнструкцiй;

5.Попереджуюче завантаження даних по припущенню;

Вiдмiннiсть мiж функцiями архiтектури i86 i ITANIUM приведенi в табл.1

Таблиця 1

| Архiтектура i86 | Архiтектура ITANIUM |

| Використовування складних iнструкцiй змiнноi довжини, оброблюваних по однiй | Використовування простих iнструкцiй однаковоi довжини, згрупованих по три в групi |

| Переупорядковування i оптимiзацiя iнструкцiй пiд час виконання | Переупорядковування i оптимiзацiя iнструкцiй пiд час компiляцii |

| Спроби прогнозу переходiв | Виконання декiлькох послiдовностей команд одночасно без прогнозу переходiв |

| Завантаження даних з пам'ятi у мiру потреби | Завантаження даних з пам'ятi до того, як вони будуть потрiбно |

Вместе с этим смотрят:

GPS-навигация

IP-телефония. Особенности цифровой офисной связи

РЖсторiя звтАЩязку та його розвиток

Автоматика, телемеханика и связь

Анализ режимов автоматического управления