Разработка схемы управления на дешифраторе

Одной из составляющих частей многих электронно-вычислительных систем является схема управления. Схема управления крайне необходима в построении сложных схем. Она предназначена для формирования последовательностей управляющих импульсов и должна обладать высокой надежностью и соответствовать заданному алгоритму управления, так как от корректности её работы во многом зависит функционирование всей системы в целом. Управляющие импульсы могут использоваться, например, для синхронизации двух и более устройств, для запуска и инициализации других схем, для тактирования регистров, счетчиков, запоминающих устройств. Очевидно, что неверно спроектированная схема управления приведет к неправильной работе данных устройств.

В настоящее время существует множество средств реализации схем управления. В частности, в данной работе приведена схема управления с применением дешифратора, которая позволяет формировать импульсную последовательность в зависимости от управляющего кода. Конечно, использование дешифратора в данной схеме можно было избежать, но с помощью него при изменении алгоритма управления гораздо проще перестроить схему, чем при применении вместо него, например, логических элементов.

1 Разработка функциональной схемы

Исходя из задания, схема должна включать в себя блоки запоминания и дешифрования управляющего кода, блок обработки результата дешифрирования, тактовый генератор. Кроме этих составляющих схемы необходим также блок формирования сигнала готовности к приему нового управляющего кода.

Блок запоминания необходим для хранения управляющего числа до прихода нового стартового импульса. Кроме этого данный блок служит своеобразным синхронизатором тАУ по каждому стартовому импульсу в него будет заноситься новое управляющее число, которое передается по 4-х разрядной шине данных. Блок запоминания реализован на 4-х разрядном параллельном регистре.

Блок дешифрирования управляющего кода является основным функциональным звеном схемы, позволяя распознать управляющий код. Этот блок реализован на дешифраторе 4х16, так как разрядность управляющего числа тАУ 4. По инвертированному стартовому сигналу, поступающему на входы стробирования дешифратора, на всех его выходах формируется уровень логической единицы.

Блок обработки результатов дешифрования формирует сигнал управления в соответствии с заданным алгоритмом. То есть по всем четным числам ≥ 8 посылается сигнал разрешения запуска генератора с частотой Fтакт = 100 МГц. Блок обработки результата дешифрирования управляющего кода реализован на логическом элементе И-НЕ.

Блок формирования сигнала готовности к приему нового управляющего кода содержит линию задержки и D-триггер. По стартовому сигналу, поступающему на вход R триггера (вход установки в 0), на выходе формируется сигнал низкого уровня тАУ неготовность к приему нового управляющего числа. К информационному входу триггера приложено напряжение высокого уровня, а на вход C поступает сигнал с блока обработки результатов дешифрования, по переднему фронту которого на выходе триггера формируется сигнал высокого уровня, что означает готовность к приему нового управляющего числа. Это происходит одновременно с запуском генератора. Если управляющее число нечетное или < 8, то на вход C триггера тактовый сигнал не поступает, и на его выходе сигнал низкого уровня (неготовность к приему). Для этого случая необходима линия задержки, служащая для смещения стартового сигнала во времени, который затем поступает на вход S триггера (вход установки в 1). Линия задержки должна обеспечивать задержку формирования сигнала готовности, достаточную для появления сигнала на входе управления генератора, по стартовому сигналу.

Следует также отметить, что стартовый импульс должен быть сигналом низкого уровня и должен поступать только при сформированном сигнале готовности схемы к приему нового управляющего числа. Необходимо обеспечить, чтобы длительность этого импульса составляла 10-15 нс.

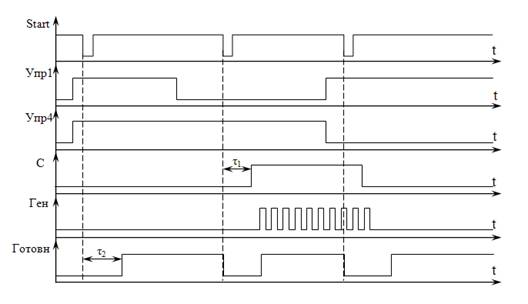

Для более детального представления работы схемы приводятся временные диаграммы ее работы (рис. 1).

Так как согласно алгоритму управления тактовый генератор запускается по всем четным числам ≥ 8, то на его работу влияют только 0-й и 3-й разряды 4-х разрядного управляющего числа. Потому что если 0-й разряд равен 1, то управляющее число нечетное, а если 3-й разряд равен 0, то управляющее число < 8.

В схеме разряды управляющего числа соответствуют сигналам:

0-й разряд тАУ Упр1,

1-й разряд тАУ Упр2,

2-й разряд тАУ Упр3,

3-й разряд тАУ Упр4.

Таким образом, когда Упр1=0 и Упр4=1 при любых сигналах Упр2 и Упр3 запускается генератор. Во всех остальных случаях запуска генератора не происходит.

Временные диаграммы построены для сигналов:

Start тАУ стартовый сигнал;

Упр1 тАУ 0-й разряд управляющего числа;

Упр4 тАУ 3-й разряд управляющего числа;

C тАУ сигнал с выхода блока обработки результатов дешифрования;

Ген тАУ сигнал с выхода генератора;

Готовн тАУ сигнал готовности к приему нового управляющего числа.

τ1 тАУ задержка формирования сигнала на выходе блока обработки результатов дешифрования (равна суммарной задержке распространения сигнала в регистре, в дешифраторе и на логическом элементе И-НЕ).

τ2 тАУ задержка формирования сигнала готовности к приему нового управляющего числа, сформированная линией задержки (τ2 > τ1).

Рис. 1. Временные диаграммы работы схемы управления на дешифраторе

2 Разработка принципиальной схемы

При разработке принципиальной схемы было принято решение об использовании микросхем серии КР1533. Это маломощные быстродействующие цифровые интегральные микросхемы, построенные на основе ТТЛШ технологии. Допуск на напряжение питания для этой серии составляет В± 10%. Микросхемы серии КР1533 имеют наибольший порог переключения среди микросхем ТТЛ тАУ 1,52 В и, как следствие, наибольшую помехоустойчивость. Входы микросхем этой серии можно подключать к источнику питания +5 В непосредственно. Использование микросхем одной серии решает проблему совместимости.

Блок запоминания состоит из регистра хранения информации КР1533ТМ8, содержащего 4 синхронных D-триггера. Сброс триггеров происходит при подаче логического 0 на вход R, запись по переднему фронту тактового импульса на входе CLK. Информация на входах D1 тАУ D4 может меняться в любой момент, она важна лишь непосредственно перед изменением сигнала на входе CLK с логического 0 на логическую 1.

Блок дешифрования управляющего кода реализован на микросхеме К1533ИД3. Это дешифратор, имеющий 4 адресных входа 1, 2, 4, 8, два инверсных входа стробирования STR, объединенных по И, и 16 выходов 0 тАУ 15. Если на обоих входах стробирования логический 0, то на том из выходов, номер которого соответствует десятичному эквиваленту входного кода (вход 1 тАУ младший разряд, вход 8 тАУ старший), будет логический 0, на остальных выходах тАУ логическая 1. Если хотя бы на одном из входов стробирования логическая 1, то независимо от состояний входов на всех выходах микросхемы формируется логическая 1.

Блок обработки результата дешифрования построен на микросхеме КР1533ЛА1, которая представляет собой два логических элемента 4ИтАУНЕ. В блоке используется только один из элементов, второй элемент используется в схеме сброса по питанию регистра.

Блок формирования сигнала готовности к приему нового управляющего кода реализован на микросхемах КР1533ТМ2 и КР1533ЛН1. Микросхема КР1533ЛН1 представляет собой 6 логических элементов НЕ и служит для формирования задержки распространения стартового сигнала, поступающего на вход установки в 1 триггера КР1533ТМ2. Задержка каждого элемента 12 нс, общая задержка линии задержки τ2 = 6*12 нс = 72 нс. Задержка формирования сигнала на входе сброса генератора с момента поступления стартового сигнала равна суммарной задержке распространения сигнала на регистре ТМ8, дешифраторе ИД3 и логическом элементе ЛА1: τ1 = 17 + 33 + 18 = 68 нс. Таким образом, выполняется неравенство τ2 > τ1 , обеспечивающее правильное функционирование схемы.

Микросхема ТМ2 содержит два D-триггера, в схеме же используется только один. При логической 1 на входе D по переднему фронту тактового импульса на входе CLK триггер устанавливается в единичное состояние. При сигнале низкого уровня на входе R триггер устанавливается в нулевое состояние, а при сигнале низкого уровня на входе S тАУ в единичное.

В качестве тактового генератора использована микросхема КР1533АГ3 тАУ сдвоенный ждущий мультивибратор. В схеме используется только один мультивибратор. Он имеет два входа для запуска D, объединенных по И, вход сброса R, выводы C и RC для подключения времязадающих элементов, прямой и инверсный выходы. Логический 0 на входе R прекращает генерацию импульса и принудительно устанавливает выходы мультивибратора в исходное состояние независимо от состояния других входов.

Для защиты схемы от высокочастотных помех в цепях питания в схему вводят несколько конденсаторов, по числу корпусов микросхем, и один электролитический конденсатор для защиты от низкочастотных помех.

3 Электрический расчет

Для определения максимальной потребляемой мощности необходимо суммировать мощности всех интегральных микросхем. Потребляемую мощность для каждой микросхемы возьмем из справочника:

КР1533ТМ8 тАУ P1 = 70 мВт;

К1533ИД3 тАУ P2 = 75 мВт;

КР1533ЛА1 тАУ P3 = 4,75 мВт;

КР1533ТМ2 тАУ P4 = 20 мВт;

КР1533ЛН1 тАУ P5 = 12 мВт;

КР1533АГ3 тАУ P6 = 100 мВт.

Найдем общую потребляемую мощность схемы:

P = 70 + 75 + 4,75 + 20 + 12 + 100 = 281,75 (мВт).

Для расчета нагрузочной способности выделим наиболее нагруженный элемент схемы тАУ им является микросхема КР1533ЛА1, которая связана с тремя источниками тАУ с одновибратором КР1533АГ3, с триггером КР1533ТМ2 и с регистром КР1533ТМ8. Выполним расчет для них.

Минимальный выходной ток микросхемы КР1533ЛА1 Iвых min = 30 мА;

максимальный входной ток одновибратора КР1533АГ3 Iвх max = 0,1 мА;

максимальный входной ток триггера КР1533ТМ2 Iвх max = 0,1 мА;

максимальный входной ток регистра КР1533ТМ8 Iвх max = 0,1 мА.

Тогда 30 мА > 0,1 мА + 0,1 мА + 0,1 мА.

Исходя из неравенства, следует вывод, что выходной мощности достаточно для работоспособности схемы. Остальные микросхемы сопряжены с меньшим количеством источников.

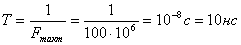

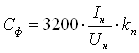

Рассчитаем номиналы времязадающих элементов на одновибраторе КР1533АГ3. Номиналы связаны с периодом следования импульсов следующей формулой  . По условию задания тактовая частота генератора должна быть

. По условию задания тактовая частота генератора должна быть

Fтакт = 100 МГц, тогда  .

.

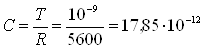

Зададимся величиной сопротивления R = 5,6 кОм. Тогда емкость конденсатора рассчитаем по формуле:

Ва(Ф).

Ва(Ф).

Ближайший номинал конденсатора из ряда стандартных емкостей тАУ 18 пФ.

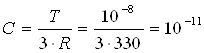

Рассчитаем элементы схемы

сброса по питанию регистра КР1533ТМ8. Согласно справочным данным микросхем серии 1533, для обеспечения надёжного сброса длительность импульса должна быть не менее 10 нс.

Для реализации схемы сброса была взята типовая схема. Рассчитать номиналы элементов можно, исходя из соотношения:  .

.

Выберем сопротивление резистора R = 330 Ом. Тогда емкость конденсатора рассчитаем по формуле:

Ва(Ф).

Ва(Ф).

Ближайший номинал конденсатора из ряда стандартных емкостей тАУ 10 пФ.

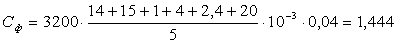

Рассчитаем емкость фильтрующих конденсаторов. Емкость электролитического конденсатора находится по формуле:

Ва,

Ва,

где  ВатАУ коэффициент пульсаций.

ВатАУ коэффициент пульсаций.  .

.

Тогда  (мкФ).

(мкФ).

Выберем электролитический конденсатор емкостью 1,5 мкФ.

По справочной литературе выберем емкости керамических конденсаторов 0,1 мкФ. Их количество определяется количеством корпусов микросхем.

В качестве резистора для формирования уровня логической единицы из напряжения питания возьмем резистор сопротивлением 1 кОм.

Выбранные дискретные элементы относятся к следующим типам:

тАУ резисторы типа С2-23-0,125;

тАУ конденсаторы: К10-23-М75-10пФ, К10-23-М75-18пФ, КМ5-Н90-0,1мкФ, К53-18-30В-1,5мкФ.

Заключение

дешифратор алгоритм элементный электрический

В ходе выполнения данной курсовой работы была разработана схема управления на дешифраторе, работающая по заданному алгоритму управления, и описано функционирование данной схемы. Также были рассчитаны потребляемая мощность, нагрузочная способность и другие характеристики схемы, подтверждающие ее правильность.

Библиографический список

1. Бирюков С.А. Применение цифровых микросхем серий ТТЛ и КМОП. тАУ 2-е изд. тАУ М.: ДМК, 2000.

2. Шило В.Л. Популярные цифровые микросхемы: Справочник.тАУ М.: Радио и связь, 1987.

3. Справочник по электрическим конденсаторам / М.Н. Дьяконов, В.И. Карабанов, В.И. Присняков и др.; Под общ. ред. И.И. Четверткова и В.Ф. Смирнова. тАУ М.: Радио и связь, 1983.

4. Гендин Г.С. Все о резисторах: Справочник тАУ М.: Горячая линия - Телеком, 1999.

5. Классификация и обозначение электрорадиоэлементов в конструкторской документации: Справочное пособие для курсового и дипломного проектирования по специальностям 2303, 2205, 2301, 2201. Часть 1/ Сост. Леухин В.Н. тАУ Йошкар-Ола: МарПИ, 1994.

Вместе с этим смотрят:

GPS-навигация

IP-телефония. Особенности цифровой офисной связи

РЖсторiя звтАЩязку та його розвиток

Автоматика, телемеханика и связь

Анализ режимов автоматического управления